# On the characterization of the trapped charge in FG-CMOS inverters

Jesus E. Molinar-Solis · Rodolfo Z. Garcia-Lozano · Ivan Padilla-Cantoya · Alejandro Díaz-Sánchez · José Miguel Rocha-Pérez

Received: 16 July 2008/Revised: 16 January 2009/Accepted: 2 February 2009/Published online: 24 February 2009 © Springer Science+Business Media, LLC 2009

Abstract In this work, an experimental comparison between measured FG CMOS inverters using the quasifloating gate (QFG) and layout-based (L-b) techniques for charge removal in the Floating-gate (FG) and simulations through PSpice is presented. The experiment was developed through the measurements of 40 different IC's with a total of 200 FG and QFG CMOS inverters characterized on AMI C5FN 0.5  $\mu$ m technology. The data obtained shows that the layout-based technique reduces the initial charge present at the FG, but presents a very small residual charge. Nevertheless, the offset associated to the charge follows a normal distribution and is predictable. Comparison between measured QFG inverters and simulations shows that the high resistance parasitic diode must be modeled accurately for a proper simulation.

**Keywords** Neuron-MOS · vMOS · Floating-gate transistors

# 1 Introduction

Nowadays, important efforts have been realized in order to eliminate the initial trapped charge at FG due to fabrication process conditions. Early UV techniques were employed to remove this charge [1-3], but the UV exposure in postfabrication represents a serious drawback from the

manufacturing perspective. Other approaches include extra circuitry and high voltages for the use of electron tunneling and/or hot electron injection [4–6]. Recently, the quasi-floating gate (QFG) concept has demonstrated not only to overcome the initial charge problem, but also set the FG to a given DC bias potential through a very high resistance. This important feature, along with the ac-coupled input signal through capacitive coupling Poly1-Poly2, allows the QFG transistor to work in a desired quiescent point [7, 8]. A serious drawback of QFG transistors is that they are not suitable for frequencies below 1 Hz range, where, the cutoff frequency depends mainly by the value of the high resistance connected to the FG.

On the other hand, a recent publication proposes a Layout-based technique (FG L-b) to deal with the initial trapped charge [9]. This technique offers to remove the initial trapped charge at expenses of no extra-circuitry or special post-process steps. Since a previous work has compared both FG transistors; without discharging technique and with the L-b technique [10], in the present work, a statistical comparison between three different techniques is carried out: FG without discharging technique, FG L-b, and QFG by means of CMOS inverters.

# 2 CMOS FG-inverter

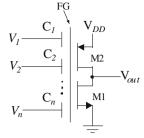

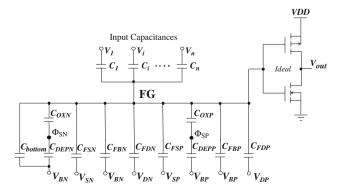

An FG inverter is a typical CMOS push–pull inverter with one or more input capacitances coupled to an isolated FG, which, is shared by the NMOS and PMOS transistors, Fig. 1. The potential induced to the FG can be controlled as a weighted sum, in voltage-mode, of all input signals. This potential, which is common to the complementary MOS-FET transistors, establishes the on–off state of the CMOS inverter [11, 12].

J. E. Molinar-Solis (⊠) · R. Z. Garcia-Lozano Mexico State Autonomous University UAEM, Jose Revueltas 17, Tierra Blanca, Ecatepec, Estado de Mexico, Mexico e-mail: jmolinar@sees.cinvestav.mx

I. Padilla-Cantoya · A. Díaz-Sánchez · J. M. Rocha-Pérez National Institute for Astrophysics, Optics and Electronics, INAOE, Luis E. Erro 1, Tonantzintla, Puebla, Mexico

Fig. 1 FG CMOS push-pull inverter

From the charge conservation law, the potential at the FG is given by the following expression:

$$V_{\rm FG} = \frac{1}{C_T} \left[ \sum_{i=1}^n C_i V_i + Q_{\rm par} + Q_{\rm FG} \right] \tag{1}$$

where,  $C_i$  denotes de *i*-th input capacitance,  $V_i$  the *i*-th voltage input,  $Q_{FG}$  the post-process FG trapped charge,  $Q_{par}$  the parasitic charge associated to NMOS and PMOS parasitic capacitances, and  $C_T$  is the sum of all capacitances to the FG including parasitics.

#### **3** FG layout-based technique

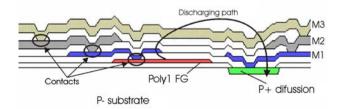

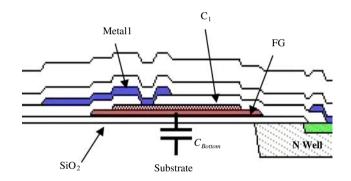

The layout-based technique for discharging the FG was first proposed in [9], the idea consists of adding metal contacts to the isolated FG in the layout, a contact for each available metal level in such technology. The key element lies on the discharging path for the FG provided by the metal layer deposited over the die during the fabrication process, Fig. 2. In such a way, any substrate contact connected to such metal layer will act as a discharging trajectory. For a brief moment, the FG will be connected to substrate until the metal etching step isolate the FG again.

#### 4 CMOS QFG inverter

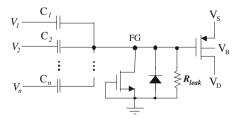

The QFG concept was first introduced by [7]. Here, the main idea is to connect the FG to a DC potential through a high resistance path. In this way, the FG is fixed to a given DC value and the capacitive coupled inputs set the AC value to the FG. A high resistance from FG to P-substrate

Fig. 2 The layout-based technique, which includes contacts from the FG to every metal layer

can be implemented by the parasitic N  $+/P_{sub}$  junction using an NMOS in cut-off, Fig. 3. This reversed diode provides a high resistance, which allows cut-off frequencies below 1 Hz.

According to [7], the  $V_{FG}$  for a PMOS can be expressed as

$$V_{\rm FG}(s) = \frac{sR_{\rm leak}}{1 + sR_{\rm leak}C_T} \left[\sum_{i=1}^n C_i V_i + Q_{\rm par}\right]$$

(2)

where the charge  $Q_{par}$  in this case is given by

$$Q_{\text{par}} = C_{\text{GS}} \cdot V_S + C_{\text{GD}} \cdot V_D + C_{\text{GB}} \cdot V_B \tag{3}$$

The capacitances  $C_{\text{GS}}$ ,  $C_{\text{GD}}$ , and  $C_{\text{GB}}$  are the parasitic couplings between the FG and the source  $(V_S)$ , drain  $(V_D)$ , and bulk  $(V_B)$ , respectively.

Considering that all input voltages  $V_I$ ,  $V_2$ ,..., $V_n$  vary in time, Eq. 2 can be solved for those potentials at DC and the initial post-process trapped charge at FG,  $Q_{FG}$ . Since  $V_B$ and  $V_S$  are fixed to  $V_{DD}$  for a PMOS transistor, then, in the time domain  $V_{FG|DC}$ ,  $Q_{FG}$  is given by

$$V_{\rm FG}|_{\rm DC, Q_{\rm FG}} = (C_{\rm GS} \cdot V_S + C_{\rm GB} \cdot V_B + Q_{\rm FG}) e^{\frac{R}{R_{\rm teak}}C_T}$$

(4)

Equation 4 reveals that any charge contribution to the FG due to DC will disappear after several time constants  $\tau = R_{\text{leak}}C_T$ . The FG potential will be affected only by those capacitive coupled signals with frequency above the cutoff frequency  $1/(2\pi R_{\text{leak}}C_T)$ . This important feature of the QFG concept makes it suitable to deal with the initial trapped charge and at the same time it causes the FG to be less sensitive to DC parasitic contribution.

Fig. 3 QFG PMOS with multiple inputs

Fig. 4 QFG CMOS push-pull inverter

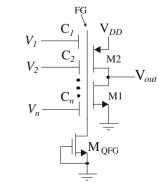

The QFG concept can be extended to CMOS push–pull inverters, i.e., the same structure presented in Sect. II, but, with the NMOS in cut-off tied to the FG, Fig. 4.

In the QFG Inverter, the voltage  $V_{FG}$  depends also on the input voltages  $V_i$  through capacitive couplings  $C_i$ , and parasitic capacitances related to both NMOS and PMOS transistors.

## 5 Simulations on PSpice

The simulations of a typical CMOS inverter, an ideal FG CMOS Inverter with  $Q_{FG} = 0$  and a QFG CMOS inverter were realized using PSpice in order to make the comparisons with the fabricated devices on AMI CF5N 0.5 µm technology. The inverter was designed using an aspect ratio of 12 µm/0.6 µm for the NMOS and PMOS transistors, respectively. A single input capacitance of 186 fF was used in the design of the FG.

## 5.1 The FG inverter

The potential at the FG of the inverter, as shown in Fig. 4, depends on input voltages  $V_1, ..., V_b ... V_n$  through a capacitive voltage divider,  $C_i/C_T$ , in addition to the parasitic contribution. In order to simulate the ideal behavior of the FG-inverter with  $Q_{FG} = 0$ , the use of a macromodel is necessary. Since most circuit simulators replace capacitors by open circuits in the DC analysis, the FG results a floating node which leads to convergence problems. The use of specialized macromodels overcomes this situation; several approaches exist in literature [13–16]. In this work; we used the latter, since all NMOS and PMOS parasitic capacitances connected to the FG are considered using PSpice MOSFET model parameters, Fig. 5.

Where  $C_i$ , is the capacitive coupling to the FG for *i*-th input,  $V_i$  is the *i*-th input voltage,  $V_{\text{DN}}$ ,  $V_{\text{DP}}$ ,  $V_{\text{SN}}$ ,  $V_{\text{SP}}$ , and  $V_{\text{BN}}$ ,  $V_{\text{BP}}$  are the drain, source and substrate voltages for the NMOS and PMOS transistors, respectively. From now

Fig. 5 FG inverter parasitic capacitances

on, the right side subscripts N and P will denote NMOS and PMOS, respectively.  $C_{\text{FDN}}$ ,  $C_{\text{FDP}}$  and  $C_{\text{FSN}}$ ,  $C_{\text{FSP}}$  are the overlap capacitances between the FG and the drain or source.  $C_{\text{FBN}}$  and  $C_{\text{FBP}}$  are the overlap capacitances between the FG and the bulk along the edge of the channel,  $C_{\text{OXN}}$  and  $C_{\text{OXP}}$  are the gate oxide capacitances and  $C_{\text{DEPN}}$  and  $C_{\text{DEPP}}$ , are the depletion layer capacitances, which can be neglected after the channel begins to form under the floating gate [17]. Potentials  $\Phi_{\text{SN}}$  and  $\Phi_{\text{SP}}$  represent the potential of the semiconductor surface. All input voltages to the FG are referenced to substrate.

The capacitance  $C_{\text{Bottom}}$  represents the parasitic associated to FG-substrate where the FG acts as the bottom plate for input capacitances, in this case for  $C_I$  is shown, Fig. 6. The value of  $C_{\text{Bottom}}$  is calculated from the FG layout area and the poly1-substrate capacitance per area.

Using the BSIMv3.1 parameters for AMI C5FN 0.5  $\mu$ m available from MOSIS, all parasitic capacitances for the FG inverter were calculated, Table 1. The total capacitance  $C_T$  is 239 fF and the capacitive voltage divider  $C_1/C_T = 0.778$ .

The parasitic charge  $Q_{par}$  can be easily computed and included to the macromodel.

**Fig. 6**  $C_{\text{Bottom}}$  parasitic capacitance composed by the bottom plate of  $C_1$  and substrate

| Table 1 | Values for | the FG | inverter | parasitic | capacitances |

|---------|------------|--------|----------|-----------|--------------|

|---------|------------|--------|----------|-----------|--------------|

| PMOS | $C_{\rm FDP}$    | 3.6 fF  |

|------|------------------|---------|

|      | $C_{\rm FSP}$    | 3.6 fF  |

|      | $C_{ m FBP}$     | 4 fF    |

|      | $C_{\text{OXP}}$ | 10.4 fF |

| NMOS | $C_{\rm FDN}$    | 2.6 fF  |

|      | $C_{\rm FSN}$    | 2.6 fF  |

|      | $C_{ m FBN}$     | 4 fF    |

|      | $C_{\rm OXN}$    | 11.5 fF |

|      | $C_{ m Bottom}$  | 20 fF   |

|      |                  |         |

$$Q_{\text{par}} = C_{\text{FSN}} \cdot V_{\text{SN}} + C_{\text{FBN}} \cdot V_{\text{BN}} + C_{\text{FDN}} \cdot V_{\text{DN}} + C_{\text{FSP}} \cdot V_{\text{SP}} + C_{\text{FBP}} \cdot V_{\text{BP}} + C_{\text{FDP}} \cdot V_{\text{DP}} + C_{\text{OXN}} (\Phi_{\text{SN}} + V_{\text{BN}}) + C_{\text{OXP}} (-\Phi_{\text{SP}} + V_{\text{RP}}) C_{\text{Bottom}} \cdot V_{\text{BN}}$$

(5)

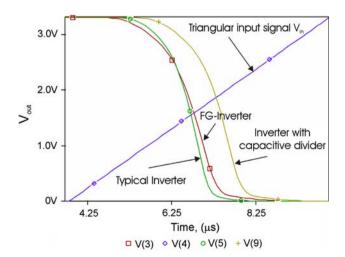

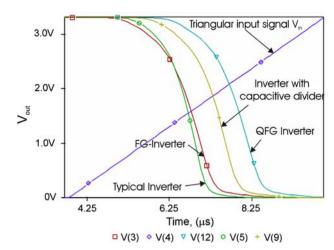

Using the above information, the macromodel was developed in PSpice. Using a  $V_{\rm DD} = 3.3$  V and a triangular input signal of 80 kHz with  $3.3V_{\rm pp}$  the transient response of three different inverters was obtained, Fig. 7. The trace with circles corresponds to the typical inverter with no extra circuitry, the input voltage  $V_{\rm in}$  necessary for an output voltage of  $V_{\rm out} = 1/2V_{\rm DD} = 1.65$  V will be the reference data for inverters comparison, from now, this voltage will be denoted by  $V_{\rm inTP}$ , so for the typical inverter case,  $V_{\rm inTP} = 1.55$  V.

The trace with squares is the response of the FG CMOS inverter (using the macromodel) and the transition point corresponds to  $V_{inTP} = 1.58$  V. Finally, the trace with crosses is a typical inverter, but, with a capacitive voltage divider of 0.778 at the input, here  $V_{inTP} = 1.92$  V. This curve gives the idea of how shifted to the right is the inverter curve with a capacitive voltage divider at the input and no DC parasitic contribution to the FG.

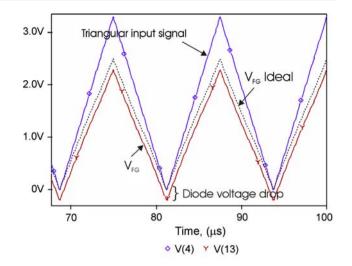

## 5.2 Simulation of the QFG inverter

In the QFG inverter circuit Fig. 3, the NMOS in cut-off provides a parasitic junction with a large resistance associated to substrate. In this case, the electrical simulator computes the DC analysis without convergence problems and as a consequence, the use of a macromodel can be avoided.

For large signal, both the junction and the FG behave as a clamping circuit, Fig. 8. Ideally, the FG signal should swing above the 0 V level, but the real behavior presents a

Fig. 8 Transient analysis simulation for the QFG Inverter, the circuit acts as a clamping circuit

DC offset due to the diode voltage drop. Although all DC contribution to the FG vanishes along time, the offset voltage related to the diode causes an important shift in the QFG inverter curve as will be shown.

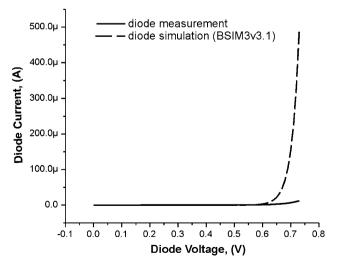

In order to simulate the QFG inverter accurately, the parasitic diode  $N^+/P^-$  must be adequately modeled. For this purpose, the Source-Bulk junction of  $M_{QFG}$  was forward biased and measured using a Keithley 236 I–V meter. This junction exhibits the same size as the Drain-Bulk junction. The comparison made with the PSpice DC sweep simulation, including the drain area AD and the drain perimeter PD using the BSIM3v3.1 parameters, is presented in Fig. 9. In the absence of some model parameters as JS, JSSW, NJ, and IJTH, the BSIM3v3.1 model uses some default values which can cause an important difference from the real behavior in forward bias. Since the

Fig. 7 Results of the FG inverter transient analysis simulation

**Fig. 9** Comparison between the parasitic diode measurement and simulation using the BSIM3v3.1 parameters in PSpice

Fig. 10 Comparison of the measured parasitic diode and the adjusted model

drain-substrate and source-substrate junctions are used normally in reverse bias in the MOSFET model, those parameters involved to describe the forward bias are not carefully extracted [18].

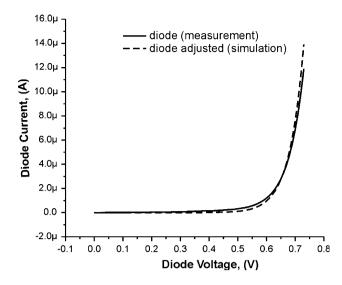

The simulation was performed using different simulators, e.g., PSpice, AIM-Spice, T-Spice and Spectre, all of them bringing analogous results, but with an important deviation from measurements. A more detailed analysis of this situation is beyond the scope of this work; nevertheless, the diode curve was adjusted manually using the model available for discrete diodes in SPICE for a more accurate simulation, hence the parasitic diode in Fig. 3 was simulated with this discrete adjusted diode. The parameters used are as follows:

D1 1 0 DPN .0077

Fig. 11 Results of the QFG inverter transient analysis simulation

The comparison of the simulated discrete diode and the measurement are in Fig. 10.

The QFG inverter was simulated using this approach and the results are presented in Fig. 11. The  $V_{inTP}$  for the QFG is 2.20 V, an expected value due to the offset produced by the clamping circuit.

## 6 Chip design

The experiment was designed with CMOS inverters since the output in voltage mode allows the use of a conventional digital oscilloscope to realize the measurements. A shift on the measured inverter transfer curve compared with a simulated reference will be the offset voltage present at the FG related to the amount of trapped charge, this will be shown in Sect. VIII.

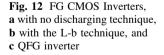

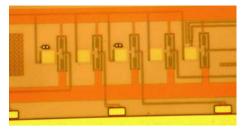

A test chip prototype was designed on CMOS AMI CF5N 0.5  $\mu$ m in order to compare the simulations and the three different approaches of FG inverters: without discharging technique, Fig. 12(a), with the layout-based technique, Fig. 12(b) and the QFG technique, Fig. 12(c).

Fig. 13 Inverters microphotograph

The QFG inverter was designed with the gate and source of  $M_{\rm QFG}$  controllable externally, thus,  $M_{\rm QFG}$  can work in cutoff or as a pass transistor, which, with a voltage sweep on the source the output curve of the inverter can be directly obtained, i.e., as a typical inverter. This curve represents an important reference, since it acts as a point of comparison among the three different techniques.

# 7 Experimental results

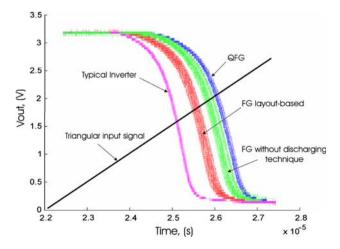

The measurements of 80 FG inverters without discharging technique, 80 with the layout-based technique, 40 with the QFG technique, and 40 typical inverters (accessing the FG through  $M_{\rm QFG}$ ) are presented.

All of them from 40 different IC's and measured with a digital oscilloscope; a picture of the different inverters is shown in Fig. 13. The measurement was developed as simulations with  $V_{\rm DD} = 3.3$  V, a triangular input signal of  $3.3V_{\rm pp}$  with 80 kHz frequency and each inverter with a capacitive load of  $C_L \approx 200$  pF, Fig. 14.

All traces were saved on the digital oscilloscope and displayed with a numerical software. The four groups in Fig. 14, follow a normal distribution and, in order to obtain a mean and a standard deviation for each one, the  $V_{inTP}$  voltage was also considered. The results are shown in Table 2.

Fig. 14 Measurements results

#### 8 Discussion

From the results shown in Table 2, each group presents a different standard deviation, the typical inverter presents the smallest, this situation arises from the fact that small transistors are used and mismatch effects are present. In the QFG inverter case, the deviation is a little bit larger; this could be explained if an added mismatch to the inverter is produced by the input capacitance, which cannot be avoided from one inverter to another. The behavior exhibited by the other two curves is different, despite of the layout-based technique; the standard deviation of these inverters is almost twice when compared with the QFG group and larger the obtained from the inverters without discharging technique. This suggests that this deviation is a consequence of charge present in the FG.

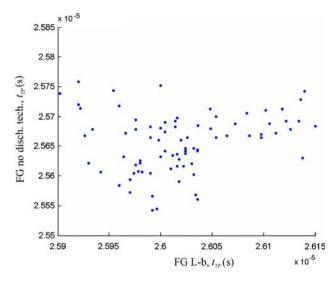

Since in both latter techniques, the fabrication process is involved on the amount of charge present at the FG, both groups could be correlated. A correlation analysis between these techniques was realized considering in this case the time  $t_{\rm TP}$  where the inverter output voltage is  $V_{\rm out} = 1/2 \cdot V_{\rm DD}$ , from Fig. 13. A scatter plot for FG L-b vs. FG no disch. tech. using the  $t_{\rm TP}$  for inverters in the same die is shown in Fig. 15.

The correlation analysis brings a result of  $r^2 = 0.027$  which denotes a weak correlation between both FG groups.

The Analysis of Variance (ANOVA) is a set of statistical methods used mainly to compare the means of three or more independent groups. The ANOVA method was realized among the three different groups: FG L-b, QFG, and FG with no discharging technique. The analysis brings an *F* value of 1495.2, a large value that rejects the null hypothesis ( $H_0$ :  $\mu_1 = \mu_2 = \mu_3$ ), which clearly indicates the three groups belong to different populations.

Comparing the mean value of  $V_{inTP}$  from the measured and the simulated inverters in Table 2, it can be noticed that the simulation of the typical inverter is almost the value of the mean obtained in measurements. However, the simulation of the FG inverter and the measured FG L-b inverter present a difference of -260 mV and with the FG with no discharging technique of -510 mV. This offset

| Table 2 | Results | of | the | simulated | and | measured | $V_{inTP}$ |

|---------|---------|----|-----|-----------|-----|----------|------------|

|---------|---------|----|-----|-----------|-----|----------|------------|

| Technique                     | Mean $(V_{inTP})$ | Std. Dev. $(V_{inTP})$ |

|-------------------------------|-------------------|------------------------|

| Typical inv. (meas.)          | 1.56 V            | 9.23 mV                |

| Typical inv. (simulation)     | 1.55 V            | _                      |

| FG inv. no dis. tech. (meas.) | 2.12 V            | 34.57 mV               |

| FG L-b inv. (meas.)           | 1.87 V            | 29.04 mV               |

| FG inv. (simulation)          | 1.59 V            | _                      |

| QFG inv. (meas.)              | 2.24 V            | 15.11 mV               |

| QFG inv. (simulation)         | 2.20 V            | -                      |

Fig. 15 Scatter plot of FG L-b vs. FG no disch. tech

present could be as mentioned above, to charge present in the FG. This charge could be explained by the fact that every etching step is achieved by the RIE or Plasma technique used normally in modern technology, where, electric fields and charge are already present [19–21]. This technological condition can lead inevitably to charge the FG in the poly1 etching step or when the last metal is etched, this, for the L-b technique case.

The difference of  $V_{inTP}$  between the simulated QFG inverter and the measured is about only 40 mV, a difference easily related to capacitance discrepancies and/or model deviations.

#### 9 Conclusion

The use of FG transistors in analog design has been limited by the unpredictable behavior of the initial trapped charge. In this work, experimental and statistical results about the characterization of FG CMOS inverters using the three different techniques for charge removal at the FG were presented. Experimentally, the three techniques follow a normal distribution with a well defined standard deviation, these important results demonstrate that de FG post-process charge is not unpredictable [10].

The comparison of the experimental and simulated data suggests that the L-b technique reduces the charge present at the FG as compared with the FG with no discharging technique; however, a small residual charge remains. This charge should be determined experimentally for those applications where the small offset can affect the circuit performance.

For the QFG case, an important advantage is that all parasitic DC contribution to the FG vanishes along time, in this sense, the QFG is not sensitive to this effect as a true FG structure. However, the observed offset associated to the clamping circuit is the major drawback, the parasitic diode which provides the high resistance path must be modeled accurately, this, in order to obtain a good agreement between measurements and simulations.

Further device experiments including continuous operation by long periods and temperature will be reported soon.

Acknowledgments This work was supported by MEP MOSIS program, Center for Research and Advanced Studies (CINVESTAV) and the National Institute for Astrophysics, Optics and Electronics (INAOE).

#### References

- Lenzlinger, M., & Snow, E. H. (1969). Fowler-Nordheim tunnelling into thermally grown SiO2. *Journal of Applied Physics*, 40(1), 278–283. doi:10.1063/1.1657043.

- 2. Sze, S. M. (2002). Semicoductor devices, physics and technology (2nd ed.). USA: Wiley.

- Yngvar, B., Lande, T. S., & Naess, Ø. (2001). Programming floating-gate circuits with UV-activated conductances, IEEE transactions on circuits and systems—II: Analog and digital. *Signal Processing*, 48(1), 12–19.

- Hasler, P., Diorio, C., Minch, B. A., & Mead, C. (1995). Single transistor learning synapses, in advances in neural information processing systems 7 (pp. 817–824). Cambridge, MA: MIT Press.

- Diorio, C., Hasler, P., Minch, B. A., & Mead, C. (1998). Floatinggate MOS synapse transistors. In T. S. Lande (Ed.), *Neuromorphic Systems Engineering: Neural networks in silicon* (pp. 315–337). Boston, MA: Kluwer Academic Publishers.

- Hasler, P. (1997). Foundations of learning in analog VLSI. Ph.D. thesis, Department of Computation and Neural Systems, California Institute of Technology, Pasadena, CA.

- Ramírez-Angulo, J., López-Martín, A., González-Carvajal, R., & Chavero, F. M. (2004). Very low-voltage analog signal processing based on quasi-floating-gate transistors. *IEEE Journal of Solid-State Circuits*, 39(3), 434–442.

- Ramírez-Angulo, J., Urquidi, C., González-Carvajal, R., Torralba, A., & López-Martín, A. (2003). A new family of very lowvoltage analog circuits based on quasi-floating-gate transistors. *IEEE Transactions On Circuits and Systems II*, 50(5), 214–220.

- Rodríguez-Villegas, E., & Barnes, H. (2003). Solution to trapped charge in FGMOS transistors. *Electronics Letters*, 39(19), 1416– 1417. doi:10.1049/el:20030900.

- Rodríguez-Villegas, E., Jimenez, M., & Carvajal, R. G. (2007). On dealing with the charge trapped in floating-gate MOS (FGMOS) transistors. *IEEE Transactions on Circuits and Systems II*, 54(2), 156–160.

- Shibata, T., & Ohmi, T. (1992). A functional MOS transistor featuring gate-level weighted sum and threshold operations. *IEEE Transactions on Electron Devices*, 39(6), 1444–1455. doi: 10.1109/16.137325.

- Shibata, T., & Ohmi, T. (1993). Neuron MOS binary-logic integrated circuits—Part I: Design fundamentals and soft-hardwarelogic circuit implementation. *IEEE Transactions on Electron Devices*, 40(3), 570–576. doi:10.1109/16.199362.

- Ramírez-Angulo, J., Gonzalez-Altamirano, G., & Choi, S.C. (1997). Modeling multiple-input floating-gate transistors for analog signal processing. IEEE International Symposium on Circuits and Systems, Hong Kong.

- Ochiai, T., & Hatano, H. (1999). A proposition on floating-gate neuron MOS macromodeling for device fabrications. IEICE Trans. on Fundamentals, vol. *E* (Norwalk, Conn.), 82-A(11).

- 15. Rodríguez-Villegas, E., Huertas, G., Avedillo, M. J., Quintana, J. M., & Rueda, A. (2001). A practical floating-gate muller-C element using vMOS threshold gates. Transactions on Circuits and Systems I, 48(1), 102-106. doi:10.1109/82.913193.

- 16. Guan, H., & Tang, Y.-S. (2000). Accurate and efficient models for the simulation of neuron MOS integrated circuits. International Journal of Electronics, 87(5), 557-568. doi:10.1080/0020 72100131986.

- 17. Shibata, T., & Ohmi, T. (1993). Neuron MOS binary-logic integrated circuits-Part II: Simplifying techniques of circuit configuration and their practical applications. IEEE Transactions on Electron Devices, 40(5), 974–979. doi:10.1109/16.210207.

- 18. Liu, W. (2001). MOSFET models for SPICE simulation including BSIM3v3 and BSIM4. USA: Wiley-IEEE Press.

- 19. Campell, S. A. (1996). The Science and Engineering of microelectronic fabrication. Oxford: Oxford University Press.

- 20. Fonash, S. J. (1990). An overview of dry etching damage and contamination effects. Journal of Electrochemical Society, 137(12), 3885-3892. doi:10.1149/1.2086322.

- 21. Fonash, S. J. (1999). Plasma processing damage in etching and deposition. IBM Journal of Research and Development, 43(1), 103-107.

Jesus Ezequiel Molinar Solis was born in Chihuahua, Mexico, in 1976. He received the electronics engineering degree from the Technological Institute from Ciudad Guzman (ITCG), Jalisco, in 1999. He obtained the M.Sc. and Ph.D. degrees in electrical engineering at the Center for Research and Advanced Studies (CINVE-STAV-IPN), Mexico City, in 2002 and 2006, respectively. He is currently working as a Titular

Professor with the Mexico State Autonomous University (UAEM) at Ecatepec, Estado de Mexico, his research interests are related to analog circuits, neural networks and vision chips.

Rodolfo Zola Garcia Lozano was born in Mexico City, Mexico in 1973. He received the electronics engineering degree from Technologic of Advanced Studies from Ecatepec (TESE), Mexico in 1996. He obtained the Ph.D degree in Electrical Engineering at the Center of Research and Advanced Studies (CINVESTAV-IPN), Mexico City, in 2005. He is currently working as a Titular Professor with the Mexico State Autono-

mous University (UAEM) at Ecatepec, Estado de Mexico. His research interests are related to electronics circuits and thin film devices application.

Ivan Padilla Cantoya was born in Mexico city, Mexico. He received the degree in electronic systems engineering from the Technological Institute and Superior Studies of Monterrey (ITESM-CEM), Mexico city, Mexico in 1999, and the M.S.E.E. degree and the Ph.D. degree from the New Mexico State University, Las Cruces, NM, in 2004 and 2007 respectively. He is with the National Institute for Astrophysics Optics

and Electronics (INAOE) where he is taking a post-doctorate course. His research interests are related to low-voltage, low-power analog circuit design and mixed-signal processing.

Alejandro Díaz Sánchez received the B.E. from the Madero Technical Institute and the M.Sc. from the National Institute for Astrophysics, Optics and Electronics, both in México, and the Ph.D. in Electrical Engineering from New Mexico State University at Las Cruces, NM. He is actually working as Full Professor at the National Institute for Astrophysics, Optics and Electronics, in Tonantzintla, Mexico. His

research concerns analog and digital integrated circuits, high performance computer architectures and signal processing.

México. He received the B.S. degree in electronics from the Universidad Autónoma de Puebla, Puebla, México in 1986 and the M.Sc. and Ph.D. degrees from the Instituto Nacional de Astrofísica Optica y Electrónica (INAOE), Puebla, in 1991 and 1999, respectively. During 1991-1996, he was working on the control of telescopes in the Astrophysics Department, and during 1999-2001 he was with the Instrumentation Lab at INAOE. He

José Miguel Rocha Pérez was

born in Huixcolotla, Puebla,

was a Visiting Researcher in the Department of Electrical Engineering, Texas A&M University, College Station in 2002 and in for CINVESTAV Guadalajara México in 2003 . In 2004 he was working as a design engineer with Freescale Semiconductor, México. Currently, he is working at INAOE in the Electronics Department. His current research interests are on the design of integrated circuits for communications and IC implementation of digital algorithms.