# ARQUITECTURA BASADA EN FPGA PARA LA RECUPERACIÓN ESTÉREO EN TIEMPO REAL PARA UNA CÁMARA INTELIGENTE.

Por:

Víctor Manuel García y García

Tesis sometida como requisito parcial para obtener el grado de Maestro en Ciencias en la especialidad de Ciencias Computacionales en el Instituto Nacional de Astrofísica, Óptica y Electrónica.

Supervisada por:

Dr. Miguel O. Arias Estrada.

©INAOE 2008

Derechos reservados. El autor otorga al INAOE el permiso de reproducir y distribuir copias de esta tesis en su totalidad o en partes.

## Resumen

La visión estéreo permite calcular o construir una estructura tridimensional de una escena a partir de dos o más imágenes tomadas desde distintos puntos de vista. La idea básica de los algoritmos estéreo es encontrar el punto de una escena capturada por un sensor de imagen con su respectivo punto proyectado en otro sensor de imagen. El procesamiento de búsqueda requiere de un alto número de operaciones. La ejecución de las operaciones, así como el acceso a los datos, representan limitantes para aplicaciones en tiempo real.

En este trabajo, se propone un sistema de visión estéreo para la recuperación tridimensional en tiempo real, empotrado en un dispositivo FPGA. Al integrar un par de sensores estéreo con el dispositivo FPGA que contiene la arquitectura hardware se obtiene una cámara inteligente 3D. La arquitectura hardware se diseñó analizando los datos independientes con respecto al tiempo, los resultados de rendimiento, muestran que la arquitectura propuesta permite una velocidad de procesamiento de 30 cuadros por segundo usando imágenes de tamaño 640x480 píxeles. Mientras que los resultados de implementación muestran que el uso del FPGA es del 60% (6,580 flip-flops). La comparación entre arquitecturas hardware no es trivial, sin embargo, se puede utilizar el número de píxeles procesados por segundo como métrica de comparación. Usando la métrica anterior, se determina que la arquitectura propuesta tiene mejor desempeño que las encontradas en la literatura. Una de las aportaciones de la arquitectura hardware es la configuración variable en tamaño de imágenes, tamaño de ventana de búsqueda y tamaño de rango de disparidad. Cualquier configuración alcanza la velocidad de procesamiento en tiempo real, sin embargo, el uso de recursos en el FPGA aumenta.

## **Summary**

Stereo vision allows to calculate a tridimentional structure of a scene from two or more captured images taken from diferents points of view. The basic idea of stereo algorithms is to find the point of one scene captured with a image sensor with its respective point projected in another image sensor. The search processing requieres a high number of operations. A real time application is limited by the execution of those operations and the data access.

In this work is proposed a real-time 3D recovery stereo vision system, embebed on a FPGA. The integration of a FPGA based hardware arquitecture with a pair of stereo images sensors results into a 3D smart camera. The hardware arquitecture design was based on an independient-time data analisys. The performance results shows that the propose arquitecture can process 30 frame per second with 640x480 pixels images. The implementation results shows that a 60% FPGA resource were used (6,580 flip-flops). The hardware arquitecture comparative is not easy to stablish, however, we can use the processed pixels per second number as a comparation metric. Using this metric, it can be stablished that the arquitecture in this work has a better performance than the found in the literature. One of the hardware arquitecture contribution is the variable performance configuration based on images sizes, search window size and disparity range size. Any configuration achieves a real time performance, but the FPGA usage increases.

## Agradecimientos.

Agradezco al CONACYT por el apoyo económico otorgado para realizar mis estudios de maestría. Al Instituto Nacional de Astrofísica, Óptica y Electrónica por el apoyo en instalaciones.

Deseo agradecer al Dr. Miguel O. Arias Estrada por su apoyo, consejos y conocimientos necesarios para la realización de este trabajo. Agradezco también a Gerardo Sosa por su gran ayuda y paciencia que me brindó. Hago extenso el agradecimiento al comité encargado de la revisión de mi tesis por el tiempo dedicado y por las observaciones recibidas.

Por último doy gracias a mis compañeros de generación en especial a Eliezer, Felix y Olmo, ya que con ellos aprendí muchas cosas más que los conocimientos científicos.

## A mis padres:

<u>Profa. Margarita García Bello.</u> Prof. Luis Roberto García Hernández.

## A mis hermanos:

Ing. Luis Roberto García y García.

Dr. Víctor Hugo García y García.

## A mi esposa:

Dr. Angélica Ponce Gómez.

## A la familia Ponce Gómez:

Lic. Fernando Ponce Ceballos.

Sra. María Guadalupe Gómez Pérez.

Ing. Eder Ponce Gómez.

## Tabla de contenido

| Capítu | ılo 1 |                                              | 6  |

|--------|-------|----------------------------------------------|----|

| Introd | ucció | ón                                           | 6  |

| 1.1    | Des   | scripción del problema                       | 6  |

| 1.2    | Ob    | jetivos                                      | 9  |

| 1.3    | Org   | ganización de la tesis                       | 9  |

| Capítu | ılo 2 |                                              | 12 |

| Funda  | men   | tos teóricos                                 | 12 |

| 2.1    | Intr  | oducción                                     | 12 |

| 2.2    | Add   | quisición y formación de imágenes            | 13 |

| 2.3    | Vis   | ión estéreo                                  | 14 |

| 2.3    | 3.1   | Geometría monocular                          | 14 |

| 2.3    | 3.2   | Modelo de Cámaras geométricas                | 18 |

| 2.3    | 3.3   | Distorsiones en las cámaras                  | 20 |

| 2.3    | 3.4   | Geometría estéreo.                           | 25 |

| 2.3    | 3.5   | Geometría epipolar                           | 28 |

| 2.3    | 3.6   | Calibración                                  | 30 |

| 2.4    | Coi   | rrespondencia Estéreo (Taxonomía de métodos) | 32 |

| 2.4    | 4.1   | Métodos locales                              | 34 |

| 2.4    | 4.2   | Métodos globales                             | 41 |

| 2.5    | Arq   | uitecturas Hardware de visión estéreo        | 42 |

| 2.6    | Dis   | cusión                                       | 46 |

| Capítu | ılo 3 |                                              | 48 |

| Arquit | ectu  | ra Hardware para la recuperación 3D          | 48 |

| 3.1    | Intr  | oducción                                     | 48 |

| 3.2    | Des   | scripción general de la arquitectura         | 49 |

| 3.3 Descripción de los módulos funcionales               | 51  |

|----------------------------------------------------------|-----|

| 3.3.1 Módulo Transformación Geométrica                   | 51  |

| 3.3.2 Módulo Correlación Estéreo                         | 55  |

| 3.3.3 Módulo Control                                     | 63  |

| 3.4 Extensiones propuestas a la arquitectura estéreo     | 65  |

| 3.4.1 Extensión para el módulo Transformación Geométrica | 65  |

| 3.4.2 Extensiones para el módulo Correlación Estéreo     | 68  |

| 3.5 Análisis de rendimiento                              | 73  |

| 3.6 Discusión                                            | 78  |

|                                                          |     |

| Capítulo 4                                               | 80  |

| Implementación y Resultados                              | 80  |

| 4.1 Introducción.                                        | 80  |

| 4.2 Implementación                                       | 81  |

| 4.3 Resultados SW / Simulación HW                        | 82  |

| 4.3.1 Resultados Transformación Geométrica               | 82  |

| 4.3.2 Resultados Correlación Estéreo.                    | 86  |

| 4.4 Resultados de síntesis                               | 92  |

| 4.4.1 Síntesis del módulo Transformación Geométrica      | 93  |

| 4.4.2 Síntesis del módulo Correlación estéreo            | 95  |

| 4.5 Discusión                                            | 104 |

| Capítulo 5                                               | 106 |

| Conclusiones                                             |     |

| 5.1 Conclusiones                                         |     |

|                                                          |     |

| 5.2 Aportaciones                                         |     |

| 5.3 Trabajo futuro                                       | 109 |

| Referencias                                              | 111 |

# **Índice de figuras.**

| Figura 2.1                                                                     | Modelo de la cámara pinhole                                                                                                                                                                                                                                                                                                                                             | 15                                                     |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Figura 2.2                                                                     | Sistema de coordenadas. Proyección 3D del punto M                                                                                                                                                                                                                                                                                                                       | . 17                                                   |

| Figura 2.3                                                                     | Distorsiones radiales                                                                                                                                                                                                                                                                                                                                                   | . 21                                                   |

| Figura 2.4                                                                     | Ejemplo de distorsión y corrección radial                                                                                                                                                                                                                                                                                                                               | .22                                                    |

| Figura 2.5                                                                     | Corrección radial mediante tablas                                                                                                                                                                                                                                                                                                                                       | . 25                                                   |

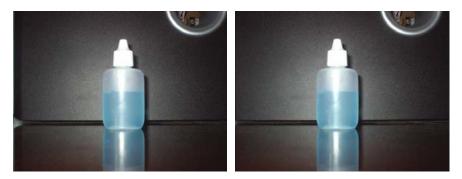

| Figura 2.6                                                                     | Ejemplo de imágenes estéreo                                                                                                                                                                                                                                                                                                                                             | 28                                                     |

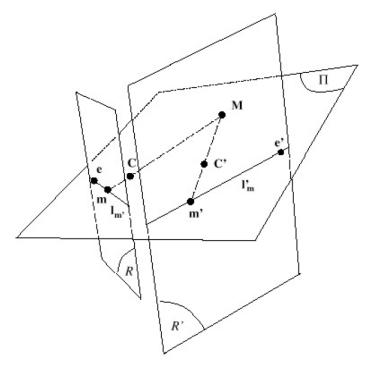

| Figura 2.7                                                                     | Geometría epipolar                                                                                                                                                                                                                                                                                                                                                      | . 29                                                   |

| Figura 2.8                                                                     | Imágenes rectificadas                                                                                                                                                                                                                                                                                                                                                   | 29                                                     |

| Figura 2.9                                                                     | Términos de la búsqueda de correspondencias                                                                                                                                                                                                                                                                                                                             | . 39                                                   |

| Figura 2.10                                                                    | Diagrama de flujo para generar mapas de disparidad                                                                                                                                                                                                                                                                                                                      | 39                                                     |

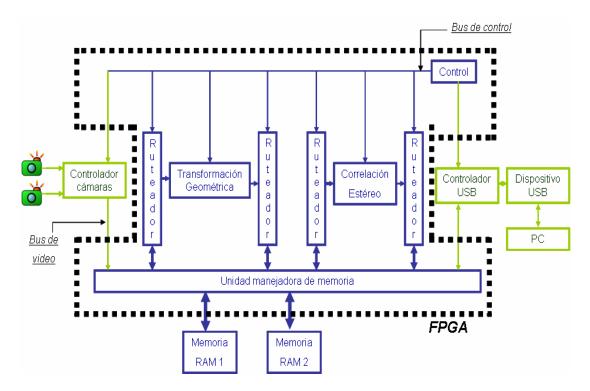

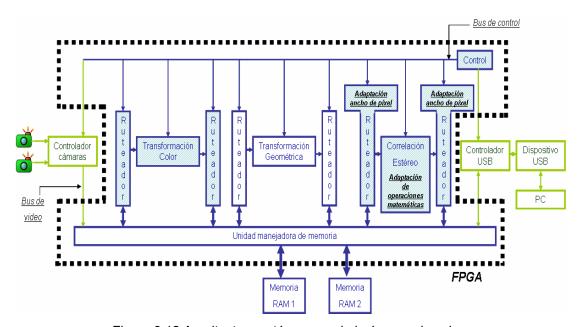

| Figura 3.1                                                                     | Diagrama a bloques: Arquitectura global                                                                                                                                                                                                                                                                                                                                 | 50                                                     |

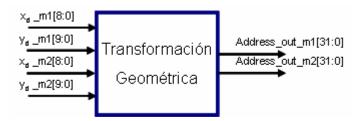

| Figura 3.2                                                                     | Diagrama a bloques: Módulo Transformación Geométrica                                                                                                                                                                                                                                                                                                                    | .54                                                    |

| Figura 3.3                                                                     | Diagrama a bloques: Módulo Ruteador para transformación g                                                                                                                                                                                                                                                                                                               | je-                                                    |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                         |                                                        |

|                                                                                | ométrica                                                                                                                                                                                                                                                                                                                                                                | 55                                                     |

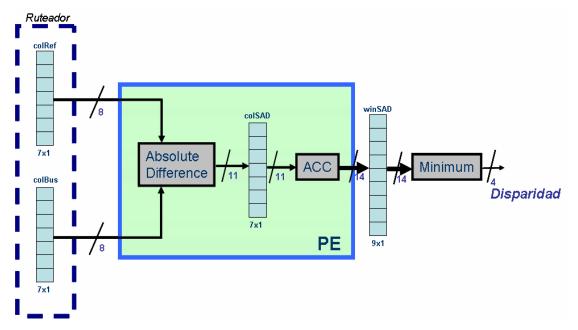

| Figura 3.4                                                                     | ométrica  Diagrama a bloques: Elemento Procesador                                                                                                                                                                                                                                                                                                                       |                                                        |

| Figura 3.4<br>Figura 3.5                                                       |                                                                                                                                                                                                                                                                                                                                                                         | 59                                                     |

| •                                                                              | Diagrama a bloques: Elemento Procesador                                                                                                                                                                                                                                                                                                                                 | 59<br>60                                               |

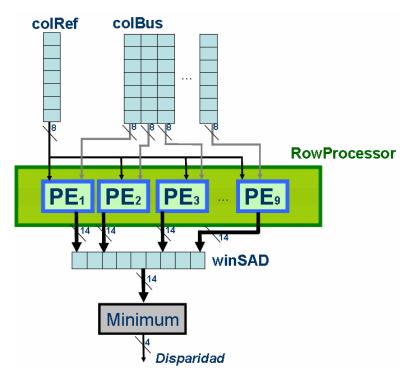

| Figura 3.5                                                                     | Diagrama a bloques: Elemento Procesador  Diagrama a bloques: RowProcessor                                                                                                                                                                                                                                                                                               | 59<br>60<br>61                                         |

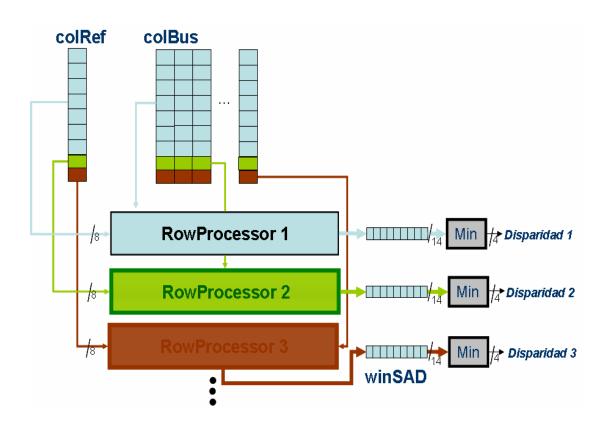

| Figura 3.5<br>Figura 3.6                                                       | Diagrama a bloques: Elemento Procesador  Diagrama a bloques: RowProcessor  Diagrama a bloques: Conjunto de rowProcessor's                                                                                                                                                                                                                                               | 59<br>60<br>61<br>. 62                                 |

| Figura 3.5<br>Figura 3.6<br>Figura 3.7                                         | Diagrama a bloques: Elemento Procesador  Diagrama a bloques: RowProcessor  Diagrama a bloques: Conjunto de rowProcessor's  Diagrama a bloques: Módulo Correlación Estéreo                                                                                                                                                                                               | 59<br>60<br>61<br>. 62<br>té-                          |

| Figura 3.5<br>Figura 3.6<br>Figura 3.7                                         | Diagrama a bloques: Elemento Procesador  Diagrama a bloques: RowProcessor  Diagrama a bloques: Conjunto de rowProcessor's  Diagrama a bloques: Módulo Correlación Estéreo  Diagrama a bloques: Módulo Ruteador para la correlación es                                                                                                                                   | 59<br>60<br>61<br>. 62<br>té-<br>63                    |

| Figura 3.5<br>Figura 3.6<br>Figura 3.7<br>Figura 3.8                           | Diagrama a bloques: Elemento Procesador  Diagrama a bloques: RowProcessor  Diagrama a bloques: Conjunto de rowProcessor's  Diagrama a bloques: Módulo Correlación Estéreo  Diagrama a bloques: Módulo Ruteador para la correlación es reo  Diagrama a bloques: Módulo Control                                                                                           | 59<br>60<br>61<br>. 62<br>té-<br>63<br>65              |

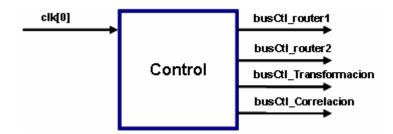

| Figura 3.5 Figura 3.6 Figura 3.7 Figura 3.8 Figura 3.9 Figura 3.10             | Diagrama a bloques: Elemento Procesador  Diagrama a bloques: RowProcessor  Diagrama a bloques: Conjunto de rowProcessor's  Diagrama a bloques: Módulo Correlación Estéreo  Diagrama a bloques: Módulo Ruteador para la correlación es reo  Diagrama a bloques: Módulo Control                                                                                           | 59<br>60<br>61<br>. 62<br>té-<br>63<br>65<br>66        |

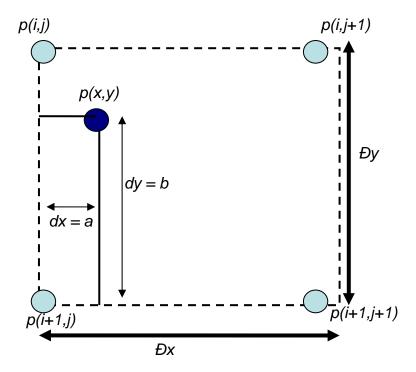

| Figura 3.5 Figura 3.6 Figura 3.7 Figura 3.8 Figura 3.9 Figura 3.10 Figura 3.11 | Diagrama a bloques: Elemento Procesador                                                                                                                                                                                                                                                                                                                                 | 59<br>60<br>61<br>. 62<br>té-<br>63<br>65<br>66        |

| Figura 3.5 Figura 3.6 Figura 3.7 Figura 3.8 Figura 3.9 Figura 3.10 Figura 3.11 | Diagrama a bloques: Elemento Procesador  Diagrama a bloques: RowProcessor  Diagrama a bloques: Conjunto de rowProcessor's  Diagrama a bloques: Módulo Correlación Estéreo  Diagrama a bloques: Módulo Ruteador para la correlación es reo  Diagrama a bloques: Módulo Control  Diagrama de las coordenadas en punto fijo  Arquitectura estéreo usando imágenes de color | 59<br>60<br>61<br>. 62<br>té-<br>63<br>65<br>66<br>.73 |

| Figura 4.3  | Primer imagen sin distorsión radial procesada por el bloque   |    |

|-------------|---------------------------------------------------------------|----|

|             | Transformación geométrica                                     | 33 |

| Figura 4.4  | Segunda imagen sin distorsión radial procesada por el bloque  |    |

|             | Transformación geométrica                                     | 3  |

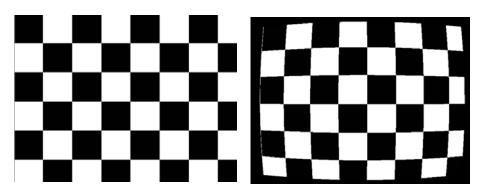

| Figura 4.5  | Tablero de ajedrez 8                                          | 5  |

| Figura 4.6  | Tablero de ajedrez distorsionado                              | 35 |

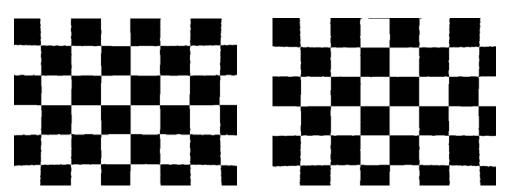

| Figura 4.7  | Correcciones radial. Izquierda sin interpolación, derecha con |    |

|             | interpolación 8                                               | 5  |

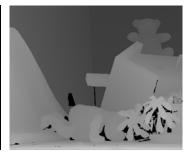

| Figura 4.8  | Par estéreo sintético: Tsukuba y Ground-truth8                | 8  |

| Figura 4.9  | Mapa de disparidad HW: Tsukuba 8                              | 8  |

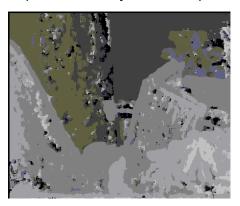

| Figura 4.10 | Par estéreo sintético: Teddy y Ground-truth 8                 | 9  |

| Figura 4.11 | Mapa de disparidad: Teddy                                     | 9  |

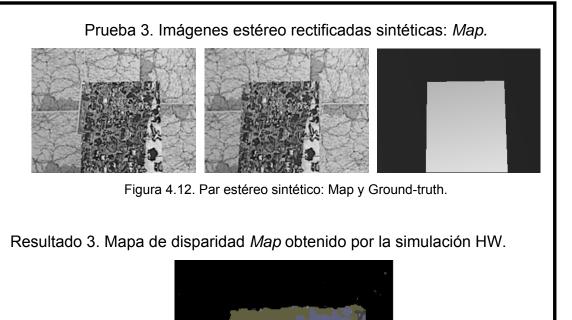

| Figura 4.12 | Par estéreo sintético: Map y Ground-truth 9                   | 0  |

| Figura 4.13 | Mapa de disparidad: Map 9                                     | 0  |

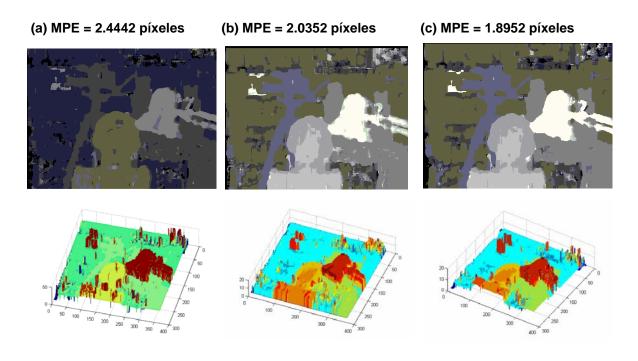

| Figura 4.14 | Mapa de disparidad y profundidad                              | 12 |

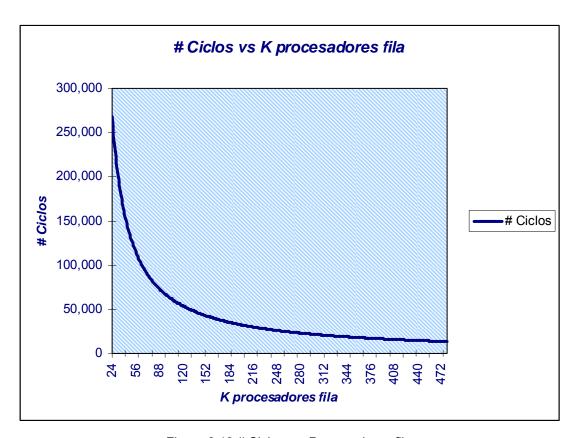

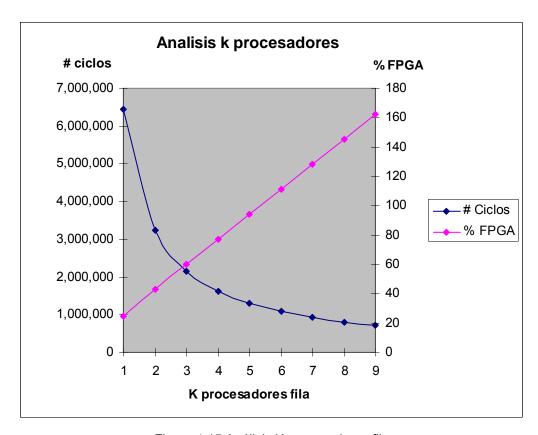

| Figura 4.15 | Análisis K procesadores fila9                                 | 7  |

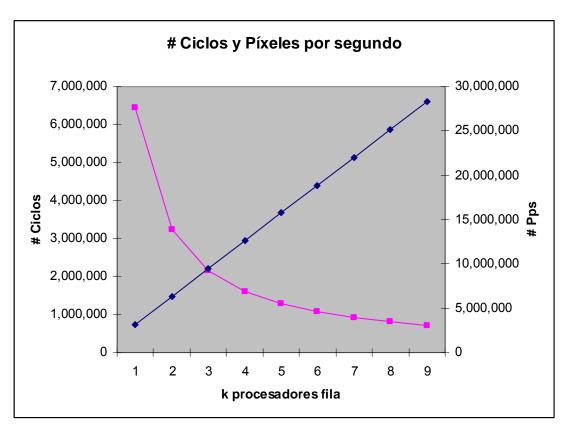

| Figura 4.16 | Píxeles por segundo9                                          | 19 |

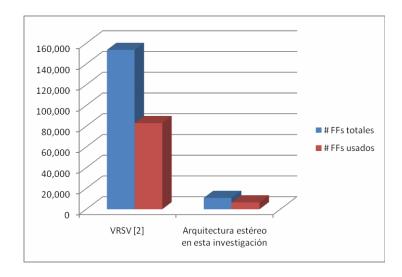

| Figura 4.17 | Comparación de flips-flops10                                  | 2  |

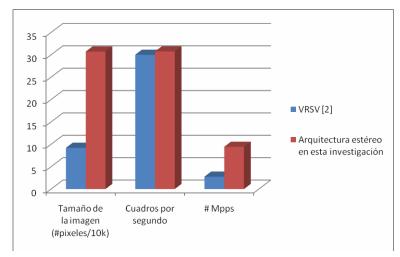

| Figura 4.18 | Comparación Mpps10                                            | )2 |

## Índice de tablas.

| Tabla 2.1 | Parámetros intrínsecos y extrínsecos                         | . 31 |

|-----------|--------------------------------------------------------------|------|

| Tabla 2.2 | Métodos de correspondencia                                   | . 33 |

| Tabla 2.3 | Medidas de similitud                                         | . 39 |

| Tabla 2.4 | Arquitecturas hardware de visión estéreo                     | . 45 |

| Tabla 4.1 | Estimación de área del bloque Transformación Geométrica      | . 94 |

| Tabla 4.2 | Estimación de área para 1,2 y 3 PE                           | 95   |

| Tabla 4.3 | Estimación de área para 1 rowProcessor                       | 96   |

| Tabla 4.4 | Análisis de implementación                                   | . 95 |

| Tabla 4.5 | Estimación de área para la arquitectura estéreo con 3 rowPro | C-   |

|           | cessor.                                                      | 100  |

| Tabla 4.6 | Comparación entre arquitecturas VRVS                         | 101  |

| Tabla 4.7 | Arquitecturas hardware de visión estéreo actualizada         | 103  |

## Capítulo 1

## Introducción.

## 1.1 Descripción del problema.

Los tipos de sistemas compuestos por uno o más sensores de imágenes y un dispositivo de procesamiento empotrado son comúnmente llamados "Cámaras inteligentes" [26]. El objetivo de una cámara inteligente es el procesamiento integrado a nivel chip, esto es, que la carga computacional del procesamiento de bajo nivel se efectúe en el dispositivo empotrado. Este dispositivo debe procesar imágenes automáticamente con el fin de obtener información relevante del escenario capturado. Las cámaras inteligentes deben realizar sus operaciones con restricciones de tiempo, de recursos de cómputo, de memoria y de potencia. El bajo costo y el bajo consumo de potencia de los dispositivos digitales, los convierten en plataformas interesantes para desarrollar sistemas empotrados. Una aplicación de estos sistemas es la visión por computadora, en específico, la visión estéreo.

La palabra estéreo es comúnmente relacionada con el sonido, pues la mayoría de los reproductores de música describen la calidad del sonido que reproducen como sonido estéreo. Es un error popular relacionar la palabra estéreo con un par de objetos cualesquiera que sean. Estéreo, según la Real Academia Española, significa 'Sólido', y hace referencia al estado de la materia sólida es decir, cuerpos definidos en tres dimensiones.

La visión estéreo, por consiguiente, se refiere a la adquisición de imágenes para ser interpretadas en tres dimensiones. La visión estéreo está presente en los seres humanos en el sentido de la vista. Los seres humanos interpretan una escena vista por sus ojos, de manera tridimensional, gracias

al procesamiento que se realiza en la corteza visual del cerebro [11]. El sistema visual de los seres humanos se basa en un par de sensores biológicos de imágenes (los ojos), sin embargo, la visión estéreo no está limitada a sólo 2 sensores.

La visión estéreo permite calcular o construir una estructura tridimensional de una escena a partir de dos o más imágenes tomadas desde distintos puntos de vista. La idea básica de los sistemas de visión estéreo se basa en el hecho de que un punto en el espacio tridimensional se proyecta a un único par de localidades en dos sensores. Por lo tanto, idealmente es posible determinar las localidades que corresponden a un mismo punto en el espacio. De lo anterior se establece que es posible encontrar la estructura tridimensional. En la práctica, existen limitaciones por las que no siempre es posible determinar cuales son las proyecciones únicas de un punto de la escena capturada. Una de estas limitaciones ocurre cuando un sensor está parcialmente ocluido, esto es, que la escena que se captura, está parcialmente obstruida por otro objeto, por lo que no será posible determinar todas las proyecciones únicas. Sensores con diferentes características físicas generan imágenes con diferencia en los valores de intensidad de los píxeles, lo cual genera ambigüedad para encontrar las proyecciones únicas. Otra limitante son las distorsiones de proyección que ocurren al capturar las escenas, entre otras.

En este trabajo se propone un sistema de visión estéreo para la recuperación tridimensional en un dispositivo digital del tipo arreglos de compuertas lógicas programables en el campo, es decir dispositivos FPGAs. Al integrar un par de sensores estéreo con el dispositivo FPGA que contiene la arquitectura hardware que realiza el procesamiento para recuperar la estructura tridimensional, se obtiene una cámara inteligente 3D. Anteriormente, se menciona que la idea básica para los algoritmos estéreo es encontrar el punto de una escena capturada por un sensor de imagen con su respectivo punto proyectado en otro sensor de imagen. Al conocer las posiciones distintas del mismo punto se puede establecer la diferencia en distancia de esas posiciones. A esta diferencia, se le conoce como disparidad. Los algoritmos que calculan las disparidades de dos o más imágenes se les conocen como algoritmos de correspondencia estéreo.

Sin embargo, para poder calcular la correspondencia estéreo, es necesario resolver otros problemas, entre ellos, eliminar las distorsiones presentes en las imágenes capturadas debido a la óptica de los sistemas de captura. También es necesario cumplir con restricciones geométricas para poder realizar la búsqueda de correspondencia en tiempos aceptables para diversas aplicaciones.

La investigación de sistemas de visión estéreo ha tomado un gran auge durante la última década, debido principalmente a las necesidades tecnológicas de diversas aplicaciones, como son: segmentación automática, seguimiento, análisis de estructuras u objetos, vigilancia [7,6] realidad virtual, sistemas médicos [15], entre otros.

Existen diferentes sistemas de visión estéreo que se pueden encontrar en la literatura, sin embargo, la mayoría son implementaciones en sistemas de cómputo de propósito general, estas implementaciones son limitadas por el procesamiento secuencial de los sistemas de cómputo tradicional, entre otras causas como el manejo de memoria realizado por el sistema operativo. También existen implementaciones en sistemas de cómputo de propósito específico que aceleran el algoritmo de correspondencia, sin embargo, la mayoría no realizan las transformaciones geométricas en las imágenes cap-

turadas, dichas transformaciones son necesarias para obtener resultados que describan de mejor forma la estructura tridimensional.

## 1.2 Objetivos.

## Objetivo general

Explorar algoritmos para la recuperación 3D en tiempo real y proponer una alternativa arquitectural basada en FPGA para una cámara inteligente.

## Objetivos específicos.

- Revisión de algoritmos que realizan la corrección geométrica de un par de imágenes estéreo y adaptarlo a una arquitectura hardware.

- Revisión de algoritmos para resolver el problema de correspondencias usando correlación estéreo.

- Analizar diversos algoritmos para el cálculo de medidas de similitud y adaptar los seleccionados a una arquitectura hardware reconfigurable.

- Proponer un modelo hardware que resuelva la gestión de accesos a memoria de manera eficiente.

- Diseñar e implementar un modelo hardware que sincronice los modelos anteriores

## 1.3 Organización de la tesis.

En este trabajo, se realiza una investigación sobre las transformaciones geométricas necesarias para el algoritmo de correspondencia. También se analizan los distintos algoritmos de correspondencia estéreo con el fin de proponer una arquitectura hardware basada en FPGA para la recuperación

tridimensional para una cámara inteligente. Se propone el diseño de la arquitectura que cumple con diversas restricciones, entre las más importantes está que la arquitectura transforma las imágenes recibidas del par de los sensores estéreo con el fin de que cumplan la restricción epipolar, Dicha restricción es necesario cumplirla para poder acelerar la búsqueda de correspondencias al reducir el rango de búsqueda a la línea epipolar. La arquitectura propuesta es capaz de entregar mapas de disparidad con una velocidad de video; es decir 30, cuadros por segundo, cumpliendo con la restricción de tiempo real.

La arquitectura hardware desarrollada en este trabajo puede ser complementada con la integración de módulos de post-procesamiento, en específico, se propone como extensión a la arquitectura hardware, la integración de módulos de interpolación que permitirán obtener mapas de disparidad de mejor calidad. Otra extensión propuesta se basa en el uso de imágenes a color para su procesamiento estéreo. Se ha demostrado estadísticamente [8] que el uso de imágenes a color mejora la calidad de los mapas de disparidad denso.

Por otro lado, la arquitectura propuesta en este trabajo cuenta con características importantes, principalmente la escalabilidad de la misma. A pesar que la arquitectura estéreo propuesta trabaja con parámetros fijos de búsqueda para el algoritmo de correspondencia, la arquitectura tiene la capacidad de rediseñarse de una manera relativamente fácil con el fin de modificar los parámetros de búsqueda, manteniendo la velocidad de procesamiento. Mas adelante se mostrará como resultado de este trabajo de investigación, la implementación de una arquitectura hardware basada en FPGA que permite la recuperación 3D en tiempo real dado un par de imágenes estéreo sin rectificar. La arquitectura hardware se basa en elementos procesador (PE). El número de PEs puede ser variado para cumplir diversas restricciones de la aplicación final.

El documento está dividido por capítulos de la siguiente manera. El capítulo 2 presenta los fundamentos teóricos en donde se basa la investigación de este trabajo. El capítulo 3 describe el diseño de la arquitectura estéreo que permite generar mapas de disparidad a partir de un par de imágenes estéreo no rectificadas. El capítulo 4 muestra los resultados de la implementación, así como los resultados de rendimiento y los resultados de prueba que validan el funcionamiento de la arquitectura estéreo. El documento termina en el capítulo 5 con las conclusiones obtenidas por el desarrollo de esta investigación, así como trabajos a futuro sugeridos para el crecimiento de la arquitectura estéreo.

## Capítulo 2

## Fundamentos teóricos

### 2.1 Introducción.

La visión estéreo permite calcular o construir una estructura tridimensional de una escena a partir de dos o más imágenes tomadas desde distintos puntos de vista. La idea básica de los sistemas de visión estéreo se basa en el hecho de que un punto en el espacio tridimensional se proyecta a un único par de localidades en dos cámaras. Por lo tanto, idealmente es posible determinar las localidades que corresponden a un mismo punto en el espacio. Al conocer las localidades donde un mismo punto se proyecta en 2 o más imágenes es posible encontrar la estructura tridimensional de la escena. En la práctica, existen limitaciones por las que no siempre es posible determinar cuales son las proyecciones únicas de un punto de la escena capturada. Una de estas limitaciones ocurre cuando un sensor está parcialmente ocluido, esto es, que la escena que se captura, esta parcialmente obstruida por otro objeto, por lo que no será posible determinar todas las proyecciones únicas. Por otro lado, existen ambigüedades que no siempre permiten encontrar las correspondencias estéreo, dichas ambigüedades son generadas por diversos factores como diferencia en texturas de los objetos capturados así como imágenes no ecualizada, es decir con imágenes de intensidades normalizadas.

Sin embargo, cuando se es posible conocer las proyecciones de todos los puntos de la escena en ambas cámaras, se puede generar un mapa basado en las diferencias de las proyecciones a lo que se le conoce como **mapa de disparidad**. Si se determinan todas las disparidades de la escena capturada, entonces el mapa de disparidad es *denso*. El mapa de disparidad se

puede calcular a través de distintos métodos llamados *algoritmos de corres*pondencia. Independientemente de la técnica o algoritmo usado para generar el mapa de disparidad, la reconstrucción tridimensional se basa en este mapa junto con el conocimiento de la geometría del sistema estéreo.

La fiabilidad de los resultados generados por los algoritmos de correspondencia depende de distintos factores, en particular, es necesario que las imágenes del sistema estéreo estén rectificadas, esto es, que cumplan con la restricción epipolar logrando realizar la búsqueda de correspondencias solamente sobre la línea definida por los epipolos (línea epipolar). A lo largo de este capítulo, se revisan los fundamentos teóricos en los que se basa la visión estéreo, como lo es la adquisición y formación de imágenes, geometría estéreo y epipolar, calibración y el problema de correspondencia. Una vez presentadas estas bases, se repasan las arquitecturas hardware, de donde se sugiere que una implementación en hardware basada en FPGA podrá acelerar el algoritmo estéreo. En la sección 2.6 se realiza una discusión acerca de las limitaciones y perspectivas de este trabajo.

## 2.2 Adquisición y formación de imágenes.

Las imágenes estéreo se pueden generar de diversas maneras en donde parámetros geométricos y ópticos definen al sistema que las captura. Debido a las distintas configuraciones de los sistemas de captura estéreo, se han realizado trabajos [24] que analizan la geometría y la posición de los sensores para optimizar la recuperación estéreo. También se puede controlar la variación en la iluminación de la escena, a este método se le conoce como fotometría estéreo [29]. Debido a la gran cantidad de factores a controlar, en la práctica estos tipos de sistemas son limitados en sus aplicaciones.

Otro método para la recuperación tridimensional, se basa en la variación del foco de la lente de la cámara. Si se adquieren varias imágenes del mismo objeto, cada imagen capturada con distintos enfoques, entonces se puede recuperar la información tridimensional del objeto. A dicho método se le conoce como "Profundidad a partir del enfoque" (depth from focus/defocus). Se puede revisar [17] para mayor información de este método.

También se puede recuperar imágenes estéreo simulando un sistema estéreo usando una sola cámara. Es necesario capturar una primera imagen y después trasladar la cámara para capturar la segunda. El inconveniente de este método es que el objeto debe estar estático. Otra limitación surge ya que es necesario un montaje robotizado que realice la traslación de la cámara con el fin de realizar la calibración; sin embargo, el proceso de calibración debe entregar resultados milimétricos, los cuales no siempre se logran sin un previo procesamiento que corrija las distorsiones en las imágenes.

En este trabajo se estudiarán los sistemas estéreo basados en dos cámaras. En la siguiente sección se describe la importancia de la geometría en el procesamiento de los sistemas estéreo, así como las correcciones a las diversas distorsiones sufridas durante el proceso de captura.

### 2.3 Visión estéreo.

#### 2.3.1 Geometría monocular.

Existen distintos dispositivos de captura de imágenes, desde los ojos en los animales hasta cámaras de video y radio telescopios. Muchos de estos dispositivos están equipados con lentes. Tómese como primer ejemplo la cámara obscura que fue inventada en el siglo XVI. Esta cámara no tenía len-

tes, en su lugar, usaba un agujero del tamaño de un alfiler o *pinhole*, el cual enfocaba los rayos de la luz hacia un plano translucido. Esta proyección de los rayos de luz, representa la imagen del escenario capturado por el pinhole. En la actualidad, las cámaras digitales son en esencia, una cámara obscura capaz de grabar la cantidad de luz que llega a una pequeña área de su plano anterior.

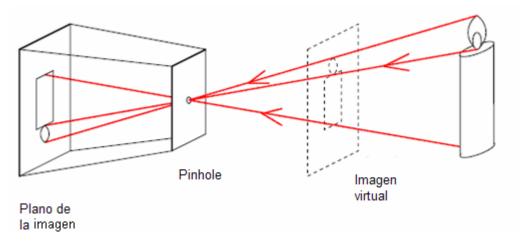

Supongamos una caja con un pequeño agujero en el centro de una de sus caras; y con un plano translucido en la cara contraria al agujero. Si pudiéramos colocar esta caja en un cuarto con poca luz, en donde existiera una fuente de luz, digamos, una vela; al colocar la caja con el agujero en dirección a la vela, se observaría una imagen invertida de la vela proyectada en el plano translucido (Figura 2.1). Esta imagen es formada por los rayos de la luz emitidos por la escena, los cuales pasan por el agujero de la caja y se proyectan en el plato translucido.

Figura 2.1 Modelo de la cámara pinhole.

El proceso anterior que menciona a una caja con un agujero, se le conoce como cámara *pinhole*. En realidad, el agujero tiene un tamaño finito, por lo que cada punto en el plano de la imagen agrupa luz desde un cono de rayos a cierto ángulo. Por otro lado, las cámaras reales están equipadas con lentes, lo que complica el modelado del proceso de captura. En [23], se hace una discusión de las similitudes del modelo de pinhole con respecto al modelo real; donde en resumen, se concluye que el modelo de proyección de perspectiva pinhole es matemáticamente conveniente y a pesar de su simplicidad provee una aproximación aceptable al proceso de captura de imágenes.

Existen dos principales razones que justifican el uso de lentes en cámaras reales. La primera razón es para concentrar mejor la luz, dado que un rayo de luz debería alcanzar un solo punto en el plano de la imagen bajo un modelo ideal pinhole. Como ya fue discutido, el tamaño del agujero es finito, esto ocasiona que mientras más grande sea el agujero, más ancho será el cono de rayos por lo que la imagen tendrá más brillo, sin embargo, esto produce que las imágenes se vuelvan borrosas. Por otro lado, el reducir el tamaño del agujero produce imágenes que representan sus bordes de manera más fina pero reduce la cantidad de luz que llega al plano de la imagen, lo que puede producir efectos de difracción. La segunda razón para usar lentes, es el mantener la imagen enfocada finamente mientras se concentra la luz de un área grande.

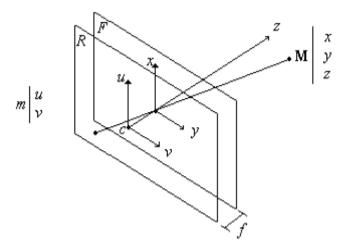

Como se explicó anteriormente, el modelo de la cámara de agujero de alfiler realiza una transformación de perspectiva del espacio tridimensional al plano de la imagen R a través de su centro óptico C. Se define el espacio tridimensional a través del sistema de coordenadas (C, x, y, z) y al plano R con las coordenadas (C, C, C). El eje C0 es perpendicular al plano C1 y se llama eje óptico de la cámara (Figura 2.2).

Figura 2.2 Sistema de coordenadas. Proyección 3D del punto M.

De la figura 2.2 se obtiene que la relación entre las coordenadas de la imagen y las coordenadas tridimensionales del espacio pueden escribirse como:

$$-\frac{f}{z} = \frac{u}{x} = \frac{v}{y} \tag{2.1}$$

Al reescribir la ecuación 2.1 de forma lineal, entonces se puede establecer como sigue:

$$\begin{bmatrix} U \\ V \\ S \end{bmatrix} = \begin{bmatrix} -f & 0 & 0 & 0 \\ 0 & -f & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix}$$

(2.2)

Donde

$$u = \frac{U}{S}$$

,  $v = \frac{V}{S}$  y  $S = z$ .

Se observa de lo anterior que sólo cuando z es distinto de cero, las coordenadas u, v están definidas.

## 2.3.2 Modelo de Cámaras geométricas.

Revisando la geometría de la adquisición y formación de las imágenes, se observa que un punto de la escena capturada se proyecta a un punto en el plano de la imagen. Sin embargo, una línea capturada en una perspectiva paralela al agujero de la cámara (en adelante será llamado centro óptico) se proyectará como un punto en el plano de la imagen, de la misma manera se comporta un plano observado bajo la misma perspectiva proyectándose como una línea en el plano de la imagen. Sin embargo, generalmente, una pequeña perturbación en la perspectiva restaura la proyección correcta.

Es importante tener en cuenta estas consideraciones geométricas cuando se realiza procesamiento de imágenes, en específico, en visión computacional. La importancia de las consideraciones geométricas discutidas anteriormente reside en el hecho de poder determinar restricciones cualitativas de una escena en lugar de suposiciones hechas por la relativa configuración de la cámara que hizo la observación. Es igual de importante establecer restricciones cuantitativas entre las medidas realizadas en la imagen y la orientación y posición de las figuras geométricas tomadas en coordenadas de un sistema exterior.

A continuación se describen los parámetros que definen a una cámara geométrica, dichos parámetros se dividen en internos (son aquellos que definen la geometría de la cámara) y externos (son aquellos que definen la posición y orientación de la cámara con respecto al mundo real).

Parámetros geométricos de una cámara.

En la práctica, el sistema de coordenadas de la cámara y del mundo real, se relacionan a través de parámetros físicos tales como la longitud focal de la lente de la cámara, el tamaño de los píxeles capturados por el sensor CCD o CMOS, la posición del centro óptico y la posición y orientación de la cámara.

En las siguientes secciones se identifican estos parámetros, donde se define como parámetros internos aquellos que establecen la geometría de la cámara y como parámetros externos los que definen la posición y orientación de la cámara con respecto al mundo real.

#### Parámetros internos

- Longitud focal de la lente de la cámara

- Kappa. Coeficiente de distorsión radial generada en las imágenes capturadas. Dicha distorsión es generada por la estructura física de la lente de la cámara.

- Tamaño del píxel. Los sensores que capturan los rayos de luz provenientes de la escena están definidos por el tamaño del píxel que representa dicha luz.

- Coordenadas del centro óptico de la lente de la cámara.

#### Parámetros externos.

- Parámetros de translación. Definen la transformación en movimiento de translación que sufre la imagen capturada con respecto a las coordenadas del mundo real.

- Parámetros de rotación. Definen la transformación del movimiento de rotación que sufre la imagen capturada con respecto a las coordenadas del mundo real.

#### 2.3.3 Distorsiones en las cámaras.

Existen distintos tipos de distorsiones que sufren las imágenes generadas por una cámara. Estas distorsiones son generadas principalmente por las pequeñas imperfecciones en las superficies de las lentes que capturan los rayos de luz provenientes del escenario. Sin embargo, existen otros factores que producen distorsiones, como lo son la posición del sensor de la cámara, el movimiento interno o vibraciones en la cámara y por último por la temperatura.

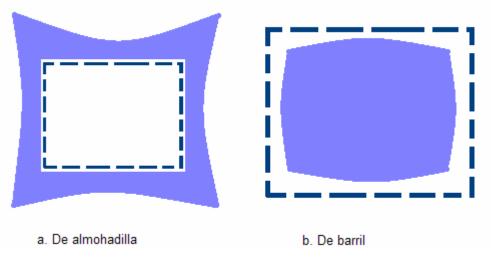

Durante el proceso de la captura del escenario por una cámara para generar una imagen, existe una característica propia de estos sistemas de captura, llamada proyección de perspectiva. Esta característica provoca que los ángulos y las distancias reales del escenario no se conserven en la imagen capturada. La proyección de perspectiva también puede ser clasificada como una distorsión. La distorsión causada por la proyección de perspectiva es una distorsión lineal ya que puede ser expresada como una matriz lineal. Por otro lado, las lentes producen otro tipo de distorsión, ésta, es causada por las características físicas de la lente. Dependiendo de la curvatura de la lente, los rayos de luz de la escena son capturados de forma no lineal. Esto es, los rayos que entran por el zona central de la lente se mantienen uniforme, sin embargo mientras más se alejen los rayos de luz del centro de la lente, éstos son capturados de forma distorsionada. A esta distorsión se le conoce como distorsión radial, donde el desplazamiento es una función no lineal que se define a través del centro óptico y la simetría circular de la lente.

En la práctica se observan dos efectos causados por la distorsión radial. El primer efecto es cuando los puntos son llevados hacia el centro de la imagen; esta distorsión es llamada de barril. El segundo efecto es cuando los puntos de la imagen son llevados desde el centro hacia las orillas; a esta distorsión se le llama de almohadilla. La figura 2.3 muestra estos efectos sobre las imágenes.

Figura 2.3. Distorsiones radiales.

#### Distorsión radial.

Diversos algoritmos de la visión computacional como los algoritmos de fotometría, seguimiento, detección de características [22], entre otros, generan mejores resultados al trabajar con imágenes que representen de forma fidedigna la escena capturada. Dicho escenario se captura a través de una lente que permite pasar rayos de luz de la escena. Sin embargo, por las características físicas de las lentes, esta imagen sufre de varias distorsiones, entre las cuales se encuentra la distorsión radial. La figura 2.4 muestra un ejemplo de una imagen distorsionada (radialmente) y su corrección.

Figura 2.4a. Imagen con distorsión radial.

Figura 2.4b. Imagen corregida.

Una solución para evitar la distorsión radial es ocupando lentes de mayor calidad que mantengan la misma resolución tanto en la zona central (fóvea) como en las orillas de la imagen, sin embargo, esta solución agrega un costo significativo al equipo de captura.

Otra solución es la algorítmica, trabajar con una imagen digital y aplicarle un algoritmo que elimine dicha distorsión radial.

Para implementar el algoritmo que elimina la distorsión radial (y en realidad, la mayoría de los algoritmos de visión computacional), se puede realizar en un sistema de cómputo de propósito general, pero esto representa limitación en tiempo y memoria debido a las características del sistema de cómputo. Una discusión más detallada acerca de las limitantes de la implementación de los algoritmos de visión computacional en sistemas de cómputo de propósito general se presenta en el capítulo 3.

Otra opción para la implementación del algoritmo que elimina distorsiones en imágenes, es usando una arquitectura hardware basada en FPGA [10]. La implementación de cualquier algoritmo en arquitecturas específicas (DSP, sistemas de cómputo de propósito general) está limitada por la resolución de datos binarios. Por otro lado, la descripción de hardware en un FPGA permite diseñar y trabajar con datos con la resolución adecuada para el algoritmo, por lo tanto la implementación de algoritmos en arquitecturas específicas requieren por lo general, una simplificación.

#### Corrección radial.

Para realizar la corrección radial se siguen los siguientes pasos:

1. Calibración geométrica de la cámara.

En este proceso, el objetivo es encontrar los parámetros geométricos de la cámara. La generación de estos parámetros se debe a que las ecuaciones que modelan la corrección radial son dependientes al factor de distorsión, dicho factor es uno de los parámetros internos de la

cámara. El proceso de la calibración es discutido con más detalle en la sección 2.3.6

#### 2. Modelar la corrección radial.

Este modelo matemático se representa mediante las siguientes ecuaciones:

$$x = x_d (1 + \alpha_1 r^2 + \alpha_2 r^4 + \alpha_3 r^6),$$

$$y = y_d (1 + \alpha_1 r^2 + \alpha_2 r^4 + \alpha_3 r^6),$$

(2.3)

donde  $(x_d, y_d)$  son las coordenadas del punto distorsionado,  $r^2 = x_d^2 + y_d^2$  es la distancia del punto distorsionado hacia el punto central y  $\alpha_1$ ,  $\alpha_2$ ,  $\alpha_3$ , son los coeficientes de distorsión de la cámara que se obtienen a través de la calibración de la cámara.

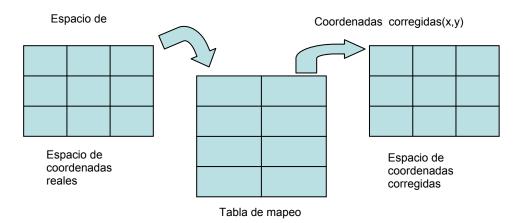

La corrección radial se realiza sobre las coordenadas de la imagen y no sobre los valores de intensidad de sus píxeles. Observando las ecuaciones que modelan la corrección radial, se sigue que este proceso, así como el anterior (calibración de la cámara), se puede realizar fuera de línea, Por lo tanto, la corrección radial se puede implementar mediante un mapeo de coordenadas. Dada una coordenada de la imagen real, realizar un mapeo hacia la coordenada corregida.

Por lo tanto, la idea es generar, mediante el cálculo de las ecuaciones que modelan la corrección radial, las tablas que mantengan el registro de las coordenadas reales con sus correspondientes coordenadas corregidas. Esta idea acelera el algoritmo de corrección radial, pues el cálculo de las tablas de mapeo sólo realiza una sola vez mientras que el mapeo de coordenadas se realiza cada vez que se capture una nueva imagen. La figura 2.5 muestra el procedimiento de forma gráfica.

Figura 2.5 Corrección radial mediante tablas.

#### 2.3.4 Geometría estéreo.

Como se describió en la sección anterior, los parámetros geométricos de la cámara son una representación de las características del sistema de captura. En este trabajo, el sistema que se usa es un sistema estéreo, por lo que existen dos conjuntos de parámetros, uno que relaciona las coordenadas de ambas cámaras y que no depende de la escena capturada, y el segundo componente que relaciona el sistema de coordenadas para cada cámara con el sistema de coordenadas de la escena. Este segundo componente definido para cada cámara es independiente de una cámara a la otra.

El proceso que obtiene los parámetros geométricos relacionados con las posiciones de las cámaras en el espacio se llama calibración estéreo. Durante la revisión de la bibliografía, se puede encontrar comúnmente el método de Tsai propuesto en [24]. Otro método (de Haralick) para la calibración es presentado en [12]. De acuerdo a [13], el método de Haralick [12] presenta mejores resultados que el método de Tsai [24] y que el método DLT [1].

Para el desarrollo de este trabajo, se usará un método mejorado y reducido del método de Haralick, el cual es presentado en [13]. Dicho método es descrito en la sección 2.3.6.

La justificación de la calibración reside en que permite simplificar el problema de la correspondencia al lograr que las imágenes estéreo estén rectificadas. Un par de imágenes estéreo se encuentran rectificadas si para cada píxel en la fila x de la imagen izquierda, su correspondiente píxel de la imagen derecha se encuentra en la misma fila x. Si se cuenta con imágenes estéreo rectificadas, la búsqueda de correspondencias se realiza sólo sobre la línea epipolar, es decir sobre la misma fila.

#### Espacios tridimensionales.

Sea  $P_w$  un punto en el espacio, el cual es representado por el vector columna  $P_w = (x_w, y_w, z_w)^T$ . Por simplicidad, se usarán coordenadas homogéneas, esto es  $P_w = (x_w, y_w, z_w, 1)^T$ . Sea  $P_i$  la proyección del punto  $P_w$  representado en el sistema de referencia de la cámara, entonces  $P_i$  se define de la siguiente manera:

$$P_i = T_{wi} \cdot P_w \tag{2.4}$$

Donde  $T_{wi}$  es la matriz que transforma las coordenadas del espacio a las coordenadas de la cámara. Esta matriz está formada por la matriz de rotación  $R_{3x3}$ , el vector de traslación  $T_{3x1}$  y por el coeficiente K que modela la distorsión radial. Por lo tanto podemos reescribir la ecuación 2.4 como sigue:

$$P_{i} = k \cdot \begin{bmatrix} R_{3x3} & T_{3x1} \\ 0 & 1 \end{bmatrix} \cdot P_{w}$$

(2.5)

Imágenes estéreo.

Al observar un objeto o escena desde dos puntos de vista, se puede notar diferencias de una imagen a la otra, estas diferencias son el desplazamiento causado por la distancia a la que se encuentra una cámara de la otra. Otra causa de la diferencia entre las imágenes es generada por el ángulo en que se encuentren las cámaras. En realidad, estos dos factores se encuentran relacionados. A la geometría en la cual la distancia de una cámara a la otra (de un centro óptico al otro) es grande, se le conoce como geometría estéreo de ángulo amplio. Por otro lado, si la distancia es corta, se le conoce como geometría de ángulo estrecho. La geometría estéreo de ángulo amplio entrega mejores estimaciones tridimensionales de la escena capturada, sin embargo, esta geometría presenta diversas limitantes, principalmente que es más difícil establecer la correspondencia en sus imágenes ya que el rango de búsqueda es mucho mayor que el de las imágenes generadas con un sistema estéreo de ángulo estrecho. Otra limitante de la geometría de ángulo amplio es que existe menos traslape entre los campos de visión por lo que existe mayor posibilidad de oclusión.

La figura 2.6 muestra un ejemplo de imágenes estéreo con cierto desplazamiento y no rectificadas. La mayoría de los sistemas estéreo usan configuraciones paralelas. El ser humano cuenta con un sistema visual un tanto distinto, ya que tiene la capacidad de ajustar el ángulo de convergencia, que en las configuraciones paralelas es de 0°. En [11] reportan que el ojo humano puede comúnmente ajustar su distancia focal de 14mm hasta 17mm siendo el desplazamiento entre los ojos aproximadamente 65mm. Este desplazamiento se le conoce como distancia intraocular.

Figura 2.6 Ejemplo de imágenes estéreo

## 2.3.5 Geometría epipolar

En un sistema estéreo, la principal característica geométrica a la que se debe llegar se le conoce como *la geometría epipolar*. Esta característica permite establecer una correspondencia unidimensional entre las imágenes estéreo. Esto es, al aplicar ciertas transformaciones, se logra que cada píxel en la imagen izquierda tenga su correspondiente píxel ubicado sobre el mismo renglón de la imagen derecha. La figura 2.7 muestra la geometría epipolar.

Si se define a C(C') como el centro óptico de la cámara izquierda (derecha). Existe una línea  $\overline{CC'}$  llamada línea epipolar que se proyecta al plano R(R') hacia los puntos e(e') a los cuales se les llama epipolos. Si cumple lo anterior, se dice que la geometría estéreo cumple la restricción epipolar, por lo que un punto M que se proyecta en m tiene su correspondiente sobre la línea  $I_m$ , por lo tanto, la búsqueda de su correspondiente se realiza sólo sobre la línea  $I_m$ .

Figura 2.7 Geometría epipolar. Si la línea  $I_{m'}$  es igual a la línea  $I'_{m}$  entonces la restricción epipolar se cumple.

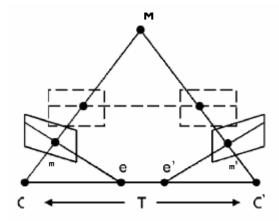

La figura 2.8 muestra la línea *T* a la que se le conoce como línea base, el plano (M,C,C') es llamado plano epipolar. Se muestra como los planos de las imágenes donde se proyecta el punto *M* pueden ser modificados para que cumplan con la restricción epipolar. Los planos modificados se muestran en líneas punteadas y son llamados planos rectificados,

Figura 2.8 Imágenes rectificadas.

Para cumplir con la restricción epipolar, se puede montar el sistema estéreo con los planos de las imágenes de tal manera que sean coplanares y que tengan la misma línea base. Sin embargo, la precisión del montaje mecánico debería ser sub-milimétrica, por lo que su implementación es poco práctica. Existen soluciones analíticas para alcanzar la restricción epipolar, éstas serán discutidas en las siguientes secciones.

#### 2.3.6 Calibración

En la sección 2.3.4 se describió como un punto en el espacio se proyecta en el plano de la imagen a través de una representación matricial. La ecuación 2.5 hace uso de la matriz de transformación  $T_{wi}$  la cual se define a través de las matrices de rotación y traslación así como por los coeficientes de distorsión radial. Para poder conocer con precisión las coordenadas de cualquier punto en el espacio proyectado en el plano de la imagen, es necesario contar con el conocimiento de varios parámetros. Estos parámetros se dividen categóricamente en dos grupos, siendo estos los parámetros extrínsecos e intrínsecos.

Los parámetros extrínsecos son aquellos que definen la posición y orientación de la cámara con respecto al sistema de referencia externo, mientras que los parámetros intrínsecos son aquellos que definen la geometría interna de la cámara. Al proceso por el cual se obtiene el conocimiento de estos parámetros se le conoce como *calibración*.

En la tabla 2.1 se enlistan los parámetros geométricos de la cámara.

| Parámetros extrínsecos.      | Parámetros intrínsecos                                                   |

|------------------------------|--------------------------------------------------------------------------|

| Matriz de rotación [3x3] R   | Distancia focal f                                                        |

| Vector de traslación [3x1] T | Tamaño del píxel $S_x$ , $S_y$                                           |

|                              | Coordenadas del centro de la imagen $C_x, C_y$                           |

|                              | Coeficientes de distorsión radial $\alpha_1$ , $\alpha_2$ , $\alpha_3$ . |

Tabla 2.1 Parámetros intrínsecos y extrínsecos.

Existen diversos métodos para realizar la calibración, entre ellos, el método de Haralick [12] y el método de Tsai [24]. Otro método es el de Abdel [1] llamado DLT y que es uno de los más usados en visión computacional. Sin embargo, en [13] se evalúan los tres métodos anteriores mostrando que el método de Tsai produce los peores resultados. En [13] se propone el método de Haralick con una reducción en su costo computacional, el cual entrega mejores resultados que los encontrados por DLT, Tsai y Haralick. Debido a esto, el método de calibración que se usó en este trabajo fue el de Haralick reducido [13]. La simplificación al método de Haralick descrita en [13] se realiza al introducir un mapeo lineal al sistema de transformación de las coordenadas del espacio tridimensional a las coordenadas del plano de la imagen. Los parámetros de calibración son generados al resolver un sistema de ecuaciones lineales sobreestimado a través del método de mínimos cuadrados. Otro aporte en su trabajo fue el de manejar la distorsión radial de la lente a través de un concepto al cual ellos llaman "Calibración localizada" en el cual se divide la imagen en 9 ventanas, donde cada ventana tiene sus propios valores para la distorsión radial. De acuerdo a sus conclusiones, la técnica presentada mejora significativamente los resultados de la calibración con respecto a los métodos Haralick, Tsai y DLT.

## 2.4 Correspondencia Estéreo (Taxonomía de métodos)

Dado un par de imágenes estéreo, se puede obtener de ellas un mapa de disparidades. Estos mapas se pueden obtener a través de distintos métodos y cumpliendo distintas restricciones. A estos métodos se le conoce como métodos de correspondencia estéreo y su objetivo principal es el de correlacionar a un píxel de una de las imágenes con su correspondiente en la otra imagen. Comúnmente [16] estos métodos de correspondencia se dividen principalmente en dos grupos, locales y globales. En los métodos locales, la comparación se realiza sobre pequeñas ventanas de una imagen con otras ventanas en la otra imagen. Los métodos globales complementan a los anteriores al realizar la comparación en líneas completas o incluso en toda la imagen.

Los métodos locales son sensibles a regiones con ambigüedades, por ejemplo a regiones ocluidas. Los métodos globales son más robustos contra estos problemas, sin embargo, son mucho más costosos en tiempos computacionales.

Los métodos locales realizan comparaciones de ventanas para encontrar una métrica que especifica la similitud entre las ventanas. Las métricas de comparación se calculan a través de funciones llamadas **medidas de similitud**, las cuales se basan en operaciones matemáticas simples (restas, sumas) con números de tipo entero. La implementación en hardware de operaciones matemáticas que no requieren el uso de números de punto fijo o flotante, requieren de menor consumo de recursos, también, estas implementaciones reducen el tiempo de procesamiento. En las siguientes secciones se

| Métodos            | Referencia          | Descripción                          |  |  |

|--------------------|---------------------|--------------------------------------|--|--|

| Métodos globales   |                     |                                      |  |  |

| Programación       | (Quénot, 1992)      | Realiza una división de las imáge-   |  |  |

| dinámica           |                     | nes al agrupar varios renglones,     |  |  |

|                    |                     | después, a estos los divide en vec-  |  |  |

|                    |                     | tores y a ellos los compara con los  |  |  |

|                    |                     | de la otra imagen.                   |  |  |

| Curvas intrínse-   | (Tomasi et al,      | Convierte las líneas epipolares a    |  |  |

| cas                | 1995, 1998)         | curvas intrínsecas y la solución se  |  |  |

|                    |                     | encuentra resolviendo el problema    |  |  |

|                    |                     | del vecino más cercano.              |  |  |

| Grafos de corte    | (Boykov et al,      | Encuentra la disparidad al seleccio- |  |  |

|                    | 2001)               | nar el corte mínimo del flujo máximo |  |  |

|                    |                     | del grafo.                           |  |  |

| Difusión no lineal | (Mansouri et al,    | Se aplica el proceso de difusión lo- |  |  |

|                    | 1998)               | cal.                                 |  |  |

| Propagación de     | (Sun et al, 2002)   | Se resuelve usando una red de pro-   |  |  |

| probabilidades     |                     | babilidades comunicada con paso      |  |  |

|                    |                     | de mensajes.                         |  |  |

| Métodos locales    |                     |                                      |  |  |

| Correlación por    | (Fua, 1991)         | Se comparan regiones o ventanas      |  |  |

| áreas              | (Parr et al., 1976) | de la imagen mediante medidas de     |  |  |

|                    | (Zabih et al. 1997) | similitud.                           |  |  |

| Basados en el      | (Lucas et al.,      | Se minimiza una función sobre una    |  |  |

| gradiente          | 1981)               | pequeña ventana.                     |  |  |

| Correlación por    | (Faugeras et al.,   | Se comparan características de las   |  |  |

| características    | 1998)               | imágenes como esquinas o círculos.   |  |  |

|                    | (Fua et al., 1995)  |                                      |  |  |

Tabla 2.2 Métodos de correspondencia

hará una breve descripción de los métodos de correspondencia globales y locales con particular interés en la correlación por área. En [16] se realiza una revisión a los métodos de correspondencia estéreo. La tabla 2.2 resume algunos de los métodos globales y locales descritos por Myron [16].

#### 2.4.1 Métodos locales

Los métodos de correspondencia estéreo local realizan la comparación por ventanas, esto es, dada una ventana de dimensión  $N_w x M_w$  en una imagen, se busca su correspondiente en la otra imagen. Estos métodos se subdividen comúnmente en tres distintas categorías: métodos basados en el Gradiente, correlación basada en características y correlación basada en áreas.

Métodos basados en el Gradiente.

Para hallar la disparidad de un punto dado en la escena capturada por un sistema estéreo se puede plantear como una ecuación diferencial la cual relaciona el movimiento y la intensidad de brillo de dicho punto. Esta manera de calcular la disparidad se conoce como método basada en el gradiente o en el flujo óptico. Sin embargo, este método se basa en la restricción de asumir que el brillo del punto es el mismo en ambas imágenes, la cual no siempre se cumple debido a las características de los sensores del sistema estéreo. Otra razón de por que la intensidad de un punto no siempre es la misma en ambas imágenes se debe a la posición de los sensores, ya que factores de luz como sombras, afectan la captura de los rayos de luz.

Sin embargo, asumiendo que la intensidad de los puntos son los mismos en ambas imágenes, la traslación de la proyección del punto en una imagen hacia la otra se puede modelar mediante la siguiente ecuación.

$$(\lambda_x E)v + E_t = 0 (2.6)$$

Donde  $\lambda_x E$  es el valor del gradiente en la horizontal de la imagen y  $E_t$  es la derivada temporal, es decir la diferencia entre las dos imágenes.  $\nu$  es la traslación entre las dos imágenes. La complejidad de realizar la correspondencia entre las dos imágenes usando flujo óptico es O(N), con N número de píxeles en las imágenes estéreo.

La disparidad de cualquier punto se puede calcular mediante la solución al sistema de ecuaciones diferenciales lineales usando el método de mínimos cuadrados. El sistema se define como:

$$v = \left(A^T A\right)^{-1} A^T b \tag{2.7}$$

donde

$$A = \begin{bmatrix} \lambda_x E(p1) \\ \lambda_x E(p2) \\ \vdots \\ \lambda_x E(p_{nxn}) \end{bmatrix} \quad \text{y} \quad b = - \begin{bmatrix} E(p1) \\ E(p2) \\ \vdots \\ E(p_{nxn}) \end{bmatrix}$$

$$(2.8)$$

Ahora, la complejidad para resolver el mapa de disparidad es O(Nn), donde n es el número de píxeles de la ventana a computar. O(Nn) es comparable con realizar una búsqueda exhaustiva dentro de las imágenes.

Correlación basada en características.

El principal aporte de los métodos de correspondencia basados en características es que son robustos ante oclusión, escenarios con textura uniforme y ante la discontinuidad de profundidad. Los anteriores son problemas que los métodos basados en el gradiente así como los métodos de correspondencia basados en áreas son sensibles.

La razón de la robustez de los métodos basados en características se debe a que la correlación que realizan es sobre características bien definidas en las imágenes estéreo, estas pueden ser bordes, esquinas, círculos, etc. Sin embargo, un preprocesamiento es requerido para detectar estas características. Existen diversos métodos para la detección de características como SUSAN [22]. Debido a las restricciones anteriores, la densidad del mapa de disparidades se ve limitado. Debido a que la mayoría de las aplicaciones necesitan contar con mapas de disparidad densos, el interés en los métodos de correspondencia basados en características ha ido decayendo durante la última década [16].

Una vez detectadas las características, se procede a realizar la búsqueda de correspondencias. En [25] se propone usar un sistema de jerarquías para resolver el problema de correspondencia. El método de Venkateswar se resume en los siguientes pasos:

- 1. Se extraen las características (En particular, bordes).

- 2. Se construye un grafo jerárquico con las características encontradas.

La construcción del grafo se basa en relaciones estructurales y preceptúales. Las relaciones incompatibles también son usadas con el fin de reforzar el agrupamiento de características.

- 3. Una vez terminado el grafo, se podan las características incompatibles.

- 4. Se realiza la correlación por características usando los grafos de cada imagen estéreo, iniciando con la raíz y llevando un flujo TOP-DOWN. Una vez realizada la correlación con el nivel superior, las características contenidas en este nivel ya no son necesarias en las siguientes búsquedas en los niveles inferiores.

Se observa del paso 4, que el espacio de búsqueda se reduce significativamente por cada nivel que se finaliza. Los autores de [25] reportan que la complejidad del problema de correspondencia para cada nivel es  $O(N^4)$  donde N es el número de características en el nivel. Nótese que estos métodos solo obtienen disparidades (por lo tanto información de profundidad) en las características encontradas, por lo tanto, no producen mapas de disparidades densos.

#### Correlación basada en áreas.

El objetivo de los métodos de correspondencia basados en áreas es estimar la disparidad de un punto en una imagen al comparar la ventana de dimensiones *nxm* con una seria de ventanas de la otra imagen. Como se estableció en la sección 2.3.5, si el par de imágenes estéreo se encuentran rectificadas, la búsqueda se reduce a una dimensión. La búsqueda de correspondencia se basa en estimar la similitud de una ventana de una imagen con la otra ventana de la otra imagen. Para calcular esta semejanza se utilizan medidas de similitud, las cuales comúnmente se dividen en tres clases: me-

didas de correlación, medidas de diferencias de intensidad y métricas de rango.

La medida de similitud llamada Correlación Cruzada Normalizada (NCC por sus iniciales en inglés) es la medida estándar estadísticamente más usada. Por otro lado, la medida de similitud basada en la suma de las diferencias cuadradas (SSD) es un método computacional más simple que el de la correlación cruzada. Por último, existe otra medida de similitud, la cual se basa en la suma absoluta de las diferencias (SAD), y esta ha sido encontrada como la medida de similitud que se usa con frecuencia por su eficacia computacional [7]. En [23] se reporta que la medida de similitud SSD es usualmente preferible que la SAD debido a que la SSD no es sensible a la modificación causada por regiones con valores de intensidad muy pequeños o muy grandes.

La clase de medidas de similitud basada en métricas de rango fueron propuestas en [32]. Las medidas hacen uso de la relación que existe en el píxel central con los píxeles en su vecindad contenidos en su ventana. Estas medidas se basan en la transformada Census y Rank. La transformada Census relaciona a cada píxel y su vecindad con un vector de elementos boléanos. A dicho vector se le conoce como vector Census. Una vez determinados los vectores Census, se pueden comparar usando la diferencia entre ellos, la cual puede medirse el número de elementos que difieren en cada uno usando la distancia Hamming.

La transformada Rank realiza los mínimos pasos que la transformada Census, a diferencia, que cuando ya se obtuvieron los vectores Census, se suman los elementos de cada vector. El cálculo de la similitud, ahora se puede resolver con SAD o SSD. En [4] se compara el rendimiento de las métricas anteriores y entregan como resultado que medidas de similitud basadas

en métricas de rango son mas robustas ante la distorsión radiométrica y oclusión. Sin embargo, las transformadas Rank y Census incrementa la dimensión de los datos de la imagen, haciéndolos caros en sus recursos de cómputo.

La tabla 2.3 resume las medidas de similitud descritas anteriormente. La figura 2.9 describe los términos usados en la tabla 2.3

| Medida de similitud               | Definición                                                                                                                                                                                                                                                |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Correlación cruzada normalizada   | $\sum_{u,v} \left( I_1(u,v) - \bar{I}_1 \right) \cdot \left( I_2(u+d,v) - \bar{I}_2 \right)$                                                                                                                                                              |  |  |

| NCC                               | $\sqrt{\sum_{u,v} (I_1(u,v) - \bar{I}_1)^2 \cdot (I_2(u+d,v) - \bar{I}_2)^2}$                                                                                                                                                                             |  |  |

| Suma de diferencias cuadradas SSD | $\sum_{u,v} (I_1(u,v) - I_2(u+d,v))^2$                                                                                                                                                                                                                    |  |  |

| SSD Normalizada                   | $\sum_{u,v} \left( \frac{\left(I_{1}(u,v) - \bar{I}_{1}\right)}{\sqrt{\sum_{u,v} \left(I_{1}(u,v) - \bar{I}_{1}\right)^{2}}} - \frac{\left(I_{2}(u+d,v) - \bar{I}_{2}\right)}{\sqrt{\sum_{u,v} \left(I_{2}(u+d,v) - \bar{I}_{2}\right)^{2}}} \right)^{2}$ |  |  |

| Suma absoluta de diferencias      | $\sum_{u,v}  I_1(u,v) - I_2(u+d,v) $                                                                                                                                                                                                                      |  |  |

| Transformada Rank                 | $\sum_{u,v} (I_1(u,v) - I_2(u+d,v))$ $I_k(u,v) = \sum_{m,n} I_k(m,n) < I_k(u,v)$                                                                                                                                                                          |  |  |

| Transformada Census               | $\sum_{u,v} HAMMING(I_1(u,v), I_2(u+d,v))$ $I_k(u,v) = BITSTRING_{m,n}(I_k(m,n) < I_k(u,v))$                                                                                                                                                              |  |  |

Tabla 2.3 Medidas de similitud

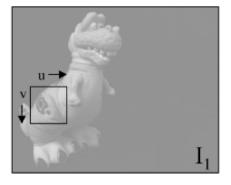

Figura 2.9 Términos de la búsqueda de correspondencias.

Las medidas de similitud hasta ahora analizadas trabajan sobre imágenes codificadas en niveles de gris. Sin embargo, la extensión de las medidas de similitud a imágenes en color ha sido planteada por Chambon en [8] en donde se muestra cómo la correlación puede ser usada con imágenes con color. De igual manera, se presenta un protocolo que permite seleccionar el espacio de colores adecuado para la correlación, así como los métodos que fusionan los canales de color para su aplicación con una medida de similitud. Los resultados reportados demuestran que la correlación estéreo puede ser mejorada usando imágenes a color.

Chambon et al [8] concluyen demostrando que usando cualquiera de los dos métodos propuestos por ellos y usando el espacio de color XYZ se generan los mejores resultados. En la sección 3.4.2 se describe con mayor detalle los métodos propuestos en [8].

Esta sección se finaliza mostrando los pasos típicos necesarios para generar el mapa de disparidad denso de una escena capturada con un sistema estéreo.

- 1. Corrección geométrica.

- a. *Calibración estéreo*. Encontrar los parámetros intrínsecos y extrínsecos del sistema estéreo.

- b. *Geometría epipolar*. Establecer la geometría que permita establecer líneas epipolares en las imágenes estéreo.

- c. Rectificación estéreo. Transformar las imágenes para que cumplan la geometría epipolar.