#### Solid-State Electronics 76 (2012) 44-47

Contents lists available at SciVerse ScienceDirect

Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Performance improvement of low-temperature a-SiGe:H thin-film transistors

## Miguel Dominguez\*, Pedro Rosales, Alfonso Torres

National Institute for Astrophysics, Optics and Electronics (INAOE), Electronics Department, Luis Enrique Erro No. 1, Puebla, ZP 72840, Mexico

#### ARTICLE INFO

Article history: Received 14 February 2012 Received in revised form 26 May 2012 Accepted 4 June 2012 Available online 2 July 2012

The review of this paper was arranged by S. Cristoloveanu

Keywords: Thin-film transistor Hydrogenated amorphous silicon–germanium Hydrogen plasma Low-temperature

#### ABSTRACT

This paper presents the study of an interface preparation procedure in the source/drain regions of the active layer, prior to deposit the n+ a-Ge:H contact layer in the fabrication process of low-temperature a-SiGe:H thin-film transistors. The devices were fabricated on corning 1737 substrates at 200 °C. The improvement in metal-semiconductor interface by the interface preparation procedure was demonstrated. This interface improvement translates in higher mobility and better values of off-current, on/ off-current ratio, subthreshold slope and threshold voltage.

© 2012 Elsevier Ltd. All rights reserved.

### 1. Introduction

Electronic devices fabricated on flexible and large-area substrates are the subjects of growing attention within both the research and the industrial community. Thin-film transistors (TFTs) based on a-Si:H technology have attracted interest due to potential low-temperature process to be integrated in flexible electronics technology.

Since the reduction in process temperature below 200 °C leads to change the deposition mechanisms, as result, the concentration of defects (dangling Si bonds) increases, the mass density decreases, and the doping efficiency drops [1]. Therefore, a-Si:H TFTs fabricated at low-temperatures (<200 °C) suffers of high-contact resistance and have poor stability, higher values of threshold voltage, off-current and subthreshold slope than those deposited at higher temperatures [2,3]. In order to improve the TFT performance, have been reported procedures which reduce the contact resistance and improve the main device interfaces [4-8]. In the inverted staggered structure, as the thickness of the active layer is reduced, the series resistance associated to this thickness decreases while the contact and channel resistances remain unchanged [9]. However, it is well known, that the density of defects increases as the amorphous film becomes thinner. For this reason, an overetching in the source/drain regions of the active layer prior to deposit the n+ contact layer can reduce the series resistance of the TFT, without reducing the thickness of the active layer. Therefore, because the n+ contact layer and the induced-channel get close, some parameters can be improved such as mobility and on/off-current ratio.

In this paper, an interface preparation procedure in the source/ drain regions prior to deposit the n+ contact layer is studied. In order to achieve a high quality insulator–semiconductor interface, high quality SiO<sub>2</sub> films by Spin-On Glass (SOG) diluted with deionized water (DI) and cured at 200 °C was used as gate insulator [10].

#### 2. Experiment

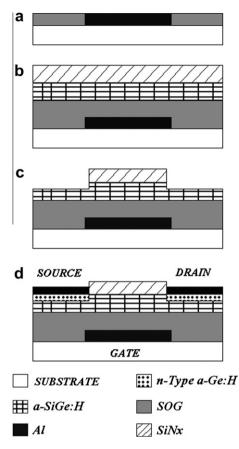

The low-temperature a-SiGe:H TFTs used the inverted staggered structure and were fabricated in corning 1737 substrates. The process flow and cross section of the a-SiGe:H TFTs are shown in Fig. 1. The simplified process flow is as follows: first, to planarize the gate electrode, 100 nm-thick of SOG diluted with DI and cured at 200 °C was used [10]. Then, photoresist was applied and patterned to leave opening for the gate. Later, the SOG was etched by Reactive Ion Etching (RIE) leaving the place of the gate. The SOG was etched with CF<sub>4</sub> plasma at a pressure of 160 mTorr and RF power of 50 Watts. Finally, as shows Fig. 1a, the planarized gate is formed by lift-off process of 100 nm-thick of e-gun evaporated Al. Afterwards, 80 nm-thick of SOG diluted with DI and cured at 200 °C was used as the gate insulator. Then, 100 nm-thick of undoped a-SiGe:H and 100 nm-thick of SiNx films were deposited using low frequency (110 kHz) plasma enhanced chemical vapor deposition (PECVD) at 200 °C, pressure of 0.6 Torr and an RF power of 300 W (Fig. 1b). Later, the SiNx film was patterned as passivation layer above the a-SiGe:H active layer using RIE. In this step, an

<sup>\*</sup> Corresponding author. Tel.: +52 222 266 3100; fax: +52 222 247 0517. *E-mail address*: mdominguez@inaoep.mx (M. Dominguez).

<sup>0038-1101/\$ -</sup> see front matter © 2012 Elsevier Ltd. All rights reserved. http://dx.doi.org/10.1016/j.sse.2012.06.005

**Fig. 1.** Process flow and cross section of the inverted staggered a-SiGe:H TFTs (not to scale). (a) planarization of the gate electrode, (b) deposit of gate insulator, active layer and passivation layer, (c) passivation layer patterned and overetching process and (d) deposit of n+ contact layer and formation of the source/drain contacts.

overetching in the a-SiGe:H film was done by RIE as shown in the Fig. 1c. The time of the overetching was of 30 s (20% of the a-SiGe:H film thickness). After that, hydrogen plasma was done at  $200 \degree \text{C}$ , with H<sub>2</sub> flow of 3500 sccm, pressure of 0.6 Torr and RF power of 300 W for 5 min. To compare the effects of this hydrogen plasma on the electrical characteristics of the TFT, other TFTs without hydrogen plasma were fabricated. Next, 40-nm thick of n-type a-Ge:H film was deposited using low frequency PECVD at  $200 \degree \text{C}$  with a pressure of 0.6 Torr and RF power of 300 W. Then, 300-nm thick of Aluminum was e-gun evaporated and patterned to form the source and drain electrodes. After, the n-type a-Ge:H film was etched using RIE (Fig. 1d). Finally, a thermal treatment at 180 °C for 40 min was done.

In order to compare the effects of the overetching process, a-Si-Ge:H TFTs with higher overetching were fabricated. The time of the overetching was of 2 min (80% of the a-SiGe:H film thickness). Also, hydrogen plasma and thermal treatment were done.

#### 3. Results and discussion

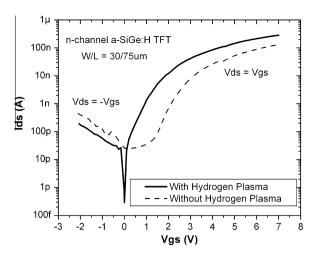

The electrical characterization of the devices was conducted using the *HP* 4156B Semiconductor Parameter Analyzer. All the measurements were done under dark conditions. The transfer characteristics of a-SiGe:H TFTs with and without hydrogen plasma application are shown in Fig. 2. Better electrical characteristics, such as on-current, off-current and on/off-current ratio, are observed for a-SiGe:H TFTs with applied hydrogen plasma. The poor electrical characteristics of a-SiGe:H TFTs without hydrogen plas-

Fig. 2. Comparison of the transfer characteristics of a-SiGe:H TFTs with and without hydrogen plasma application.

ma application are due to plasma-induced damage occasioned by the overetching process [11,12].

For the a-SiGe:H TFTs with applied hydrogen plasma, it can be observed an on/off-current ratio approximately of  $10^6$  and an off-current approximately of 300 fA at 0  $V_{\rm gs}$  which are in the range of those in high-temperature a-Si:H TFTs. The subthreshold slopes values for both a-SiGe:H TFTs with and without hydrogen plasma application were 0.56 and 0.61 V/DEC, respectively. Typically, in a-Si:H TFTs, the subthreshold slope is largely decided by the quality of gate insulator/active layer interface. In the a-SiGe:H TFT, the subthreshold slope is dependent on the trap density in the active layer a-SiGe:H ( $N_{\rm T}$ ) and at the SOG/a-SiGe:H interface ( $D_{\rm it}$ ). The subthreshold slope can be approximated as the following equation [13]:

$$S = qK_{\rm B}T(N_{\rm T}tS + D_{\rm it})C_{\rm OX}\log(e)$$

<sup>(1)</sup>

where q is the electron charge,  $K_{\rm B}$  is the Boltzmann constant, T is the absolute temperature, tS is the a-SiGe:H thickness and  $C_{OX}$  is the SOG insulator capacitance per unit area. If  $N_{\rm T}$  or  $D_{\rm it}$  is separately set to zero, the respective maximum values of  $N_{\rm T}$  and  $D_{\rm it}$  are obtained. The  $N_{\rm T}$  and  $D_{\rm it}$  values for a-SiGe:H TFTs were of  $2.65 \times 10^{17}$  cm<sup>-3</sup> eV<sup>-1</sup> and  $2.65 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> for TFTs with applied hydrogen plasma, respectively, and for TFTs without hydrogen plasma application the values were of  $2.88 \times 10^{17} \text{ cm}^{-3} \text{ eV}^{-1}$  and  $2.88 \times 10^{\hat{1}\hat{2}}\,\text{cm}^{-2}\,\text{eV}^{-1},$  respectively. Because the error estimates of the subthreshold slope are ±0.03 V/DEC for both a-SiGe:H TFTs, the differences in subthreshold slope,  $N_{\rm T}$  and  $D_{\rm it}$  values are considered as a statistical fluctuation. Since both of the a-SiGe:H TFTs have identical insulator-semiconductor interface and the overetching process only affects the source/drain regions, we do not expect any difference in the quality of the insulator-semiconductor interface of the devices.

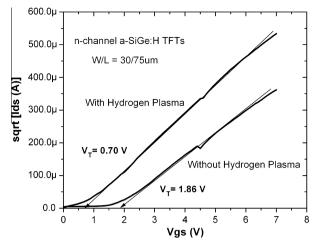

Fig. 3 shows the relation between square root of  $I_{\rm ds}$  and  $V_{\rm gs}$  of the TFT at saturation mode ( $V_{\rm ds} = V_{\rm gs}$ ). In this relation the threshold voltage and field-effect mobility can be extracted from the intercept with  $V_{\rm gs}$  axis, using Eq. (2) of the saturation region.

$$I_{\rm ds} = \mu_{\rm FE} \cdot C_{\rm OX} (W/2L) (V_{\rm gs} - V_{\rm T})^2 \tag{2}$$

where  $\mu_{\text{FE}}$  is the field-effect mobility,  $C_{\text{OX}}$  is the capacitance per unit area of the gate insulator, W and L are the channel width and the length, respectively, and  $V_{\text{T}}$  is the threshold voltage. The measured threshold voltage and field-effect mobility for a-SiGe:H TFTs were of 0.7 V and 0.85 cm<sup>2</sup>/Vs for TFTs with applied hydrogen plasma, respectively, while 1.86 V and 0.52 cm<sup>2</sup>/Vs were for TFTs without hydrogen plasma application, respectively.

**Fig. 3.** Square root of  $I_{ds}$  vs  $V_{gs}$  of a-SiGe:H TFTs with and without hydrogen plasma application at saturation mode ( $V_{ds} = V_{gs}$ ).

It is well known that hydrogen saturates dangling bonds in the amorphous film [14]. Thus, since the mobility and on-current can be affected by the quality of the metal-semiconductor interface, the higher values of mobility and on-current mean that the applied hydrogen plasma improves the metal-semiconductor interface by reducing the plasma-induced damage in the source/drain regions of the a-SiGe:H film and, as result, the series contact resistance of the device is improved.

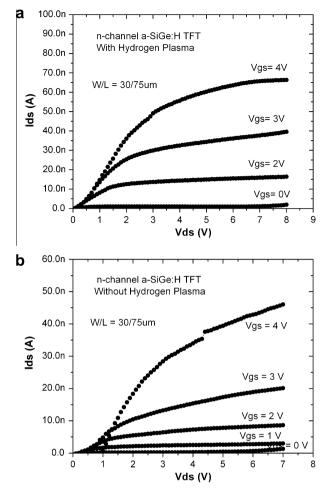

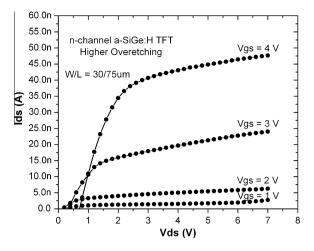

From Fig. 4 can be observed the improvement in the metalsemiconductor interface for a-SiGe:H TFTs with applied hydrogen plasma. In the output characteristics of TFTs without hydrogen plasma application a high contact resistance appears in the bias range of 0–1 V of  $V_{ds}$ . The high contact resistance not appears in TFTs with applied hydrogen plasma. Also, the  $I_{ds}$  values of TFTs with applied hydrogen plasma indicate their better driving current capability. These results confirm that plasma-induced damage by the overetching process is reduced with the applied hydrogen plasma and the interface preparation procedure in the source/drain regions leads to form good ohmic contacts.

Since the SiNx passivation film could let remains between the n+ contact layer and a-SiGe:H active layer due to process variations, the overetching process assures the etching of the SiNx passivation film and gets close the n+ contact layer and the electron induced-channel at positive gate bias.

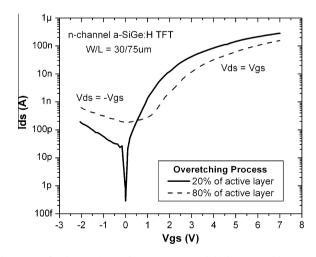

To compare the effects of the overetching process in the source/ drain regions, transfer characteristics of a-SiGe:H TFTs with higher overetching are shown in Fig. 5. Poor electrical characteristics were obtained, even with the applied hydrogen plasma and thermal treatment, the subthreshold slope was of 0.98 V/DEC, the on/offcurrent ratio was approximately  $10^3$  and the off-current was approximately 200 pA at 0  $V_{gs}$ .

The calculated maximum values of the trap density in the active layer a-SiGe:H ( $N_T$ ) and in the SOG/a-SiGe:H interface ( $D_{it}$ ) were 4.63 × 10<sup>17</sup> cm<sup>-3</sup> eV<sup>-1</sup> and 4.63 × 10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup>, respectively.

The measured threshold voltage and field-effect mobility for the a-SiGe:H TFTs with higher overetching were of 1.58 V and  $0.56 \text{ cm}^2/\text{Vs}$ , respectively. On the other hand, in the output characteristics a high contact resistance appears in the bias range of 0–1 V of  $V_{\rm ds}$  (Fig. 6). From these results, the poor quality in the metal–semiconductor interface by the higher overetching process is evident. The plasma-induced damage results in high series contact resistance and cannot be reduced even with the applied hydrogen plasma and thermal treatment.

Previously, it was mentioned that we did not expect any difference in the quality of the insulator-semiconductor interface of the

Fig. 4. Comparison of the output characteristics of a-SiGe:H TFTs, (a) with and (b) without hydrogen plasma application.

Fig. 5. Transfer characteristics of a-SiGe:H TFTs with higher overetching process.

devices, since the overetching process only affects the source/drain regions. However, the increase in the value of the subthreshold slope from 0.56 to 0.98 V/DEC is not explained at all by the high contact resistance. Therefore, the subthreshold region of the device may also be affected by other mechanism and the plasma-induced damage near of the insulator–semiconductor interface by the higher overetching process seems to be the main reason.

Fig. 6. Output characteristics of a-SiGe:H TFTs with higher overetching process.

#### 4. Conclusions

In summary, the interface preparation procedure leads to achieve a good quality metal-semiconductor interface, which translates in low contact resistance. This interface improvement translates in higher mobility and better values of off-current, on/ off-current ratio, subthreshold slope and  $V_{\rm T}$ . An overetching in the source/drain regions of approximately 20% of the a-SiGe:H thickness can improve the TFT performance, since the overetching process assures the etching of the SiNx passivation film and gets close the n+ contact layer and the electron induced-channel at

positive gate bias. Besides, the plasma-induced damage by the overetching process can be reduced with the hydrogen plasma application and thermal treatment. While the plasma-induced damage in TFTs with an overetching in the source/drain regions of approximately 80% of the a-SiGe:H thickness cannot be reduced even with the hydrogen plasma application and thermal treatment.

#### Acknowledgments

The authors want to thank to all personnel of the laboratory of microelectronics at INAOE and to the CONACYT for the scholarship No. 160547.

#### References

- [1] Robertson J. J Appl Phys 2000;87:2608.

- [2] Chen J, Cheng I. J Appl Phys 2008;104:044508.

- [3] Long K, Kattamis A, Cheng I, Gleskova H, Wagner S, Sturm J. IEEE Electron Device Lett 2006;27:111.

- [4] Indluru A, Venugopal SM, Allee DR, Alford TL. Mater Res Soc Symp Proc 2010;1245:A19-02.

- [5] Oudwan M, Moustapha O, Abramov A, Daineka D, Bonnassieux Y, Roca I Cabarrocas P. Phys Status Solidi A 2010;207(5):1245.

- [6] Han C, Han M, Paek S, Kim C, Chung I. Electrochem Solid State Lett 2007;10:J65. [7] Kao C. Lai C. Semicond Sci Technol 2008:23:025020.

- [8] Kim C. Matsumura M. IEEE Trans. Electron Devices 1994:41:1614.

- [9] GadelRab S. Chamberlain S. IEEE Trans Electron Devices 1994:41:462

- [10] Dominguez M, Rosales P, Torres A, Moreno M, Orduña A. Thin Solid Films 2012:520:5018.

- [11] Chen C, Wang S, Shieh M, Chen W, Lin H, Yeh K, et al. J Electrochem Soc 2007;154:H30.

- [12] Kuo Y, Crowder M. J Electrochem Soc 1992;139:548.

- [13] Lee C, Striakhilev D, Tao S, Nathan A. IEEE Electron Device Lett 2005;26:637.

[14] Kazmerski L. Polycrystalline and amorphous thin films and devices. Materials science and technology series. Academic Press; 1980. p. 175–85.