Desarrollo y realización de un subsistema de enlace ascendente con aplicación potencial en comunicaciones inalámbricas satelitales y espaciales en banda X

por

# Ing. Julieta Cortez Green

Tesis sometida como requisito parcial para obtener el grado de

Maestra en Ciencias en el Área de Ciencia y Tecnología del Espacio

en el

Instituto Nacional de Astrofísica, Óptica y Electrónica

Diciembre, 2023

Tonantzintla, Puebla

Bajo la supervisión de:

Dr. Celso Gutiérrez Martínez

Investigador Titular INAOE

#### **©INAOE 2023**

Derechos Reservados El autor otorga al INAOE el permiso de reproducir y distribuir copias de esta tesis en su totalidad o en partes mencionando la fuente.

# Desarrollo y realización de un subsistema de enlace ascendente con aplicación potencial en comunicaciones inalámbricas satelitales y espaciales en banda X

Tesis de Maestría

Por:

Ing. Julieta Cortez Green

Asesor:

Dr. Celso Gutiérrez Martínez

Instituto Nacional de Astrofísica Óptica y Electrónica Ciencia y Tecnología del Espacio

Tonantzintla, Puebla. Diciembre de 2023.

# Resumen

En los esquemas de comunicaciones inalámbricas, generalmente se emplean subsistemas heterodinos, aprovechando su rendimiento mejorado en comparación con esquemas más básicos de modulación y demodulación directa. Estos subsistemas de comunicación heterodina se basan en dos etapas complementarias: frecuencia intermedia (FI) y conversión de alta frecuencia ascendente/descendente.

En tal perspectiva, en este trabajo se aborda el diseño, realización y caracterización de un subsistema de enlace ascendente para comunicaciones inalámbricas satelitales o espaciales en la banda X (7190-7235 GHz), la cual está asignada para telecomunicaciones cercanas a la Tierra, en distancias de hasta 2 millones de km. El enlace ascendente es un esquema heterodino y consta de una etapa de FI, y de una etapa de conversión de radiofrecuencia (RF) ascendente hacia la banda de 7.2 GHz.

El subsistema propuesto incluye el diseño de los osciladores de FI y de RF, operando en 1.1 y 6.1 GHz, respectivamente. El diseño de los osciladores se basa en esquemas de lazo de amarre de fase (PLL). La etapa de FI incluye un modulador en cuadratura para configurar transmisiones con modulaciones analógicas y digitales.

Los resultados del trabajo desarrollado fueron publicados en los congresos internacionales *IEEE MTT-S Latin America Microwave Conference* y *SOMI XXXVII Congreso de Instrumentación*.

# Abstract

In wireless communications schemes, heterodyne subsystems are generally employed, taking advantage of their improved performance compared to more basic direct modulation and demodulation schemes. These heterodyne communication subsystems are based on two complementary stages: intermediate frequency (IF) and high frequency up/down conversion.

In such perspective, this work addresses the design, realization and characterization of an uplink subsystem for satellite or space wireless communications in the X band (7190-7235 GHz), which is assigned for near-Earth telecommunications, in distances up to 2 million km. The uplink is a heterodyne scheme and consists of an IF stage, and an uplink radio frequency (RF) conversion stage towards the 7.2 GHz band.

The proposed subsystem includes the design of the IF and RF oscillators, operating at 1.1 and 6.1 GHz, respectively. The design of the oscillators is based on phase-locked loop (PLL) schemes. The IF stage includes a quadrature modulator to configure transmissions with analog and digital modulations.

The results of the work developed were published at the international conferences *IEEE MTT-S Latin America Microwave Conference* and *SOMI XXXVII Congreso de Instrumentación*.

# Agradecimientos

Al Instituto Nacional de Astrofísica, Óptica y Electrónica por brindarme la oportunidad y el espacio para realizar mis estudios de maestría.

Al Consejo Nacional de Ciencia y Tecnología por el apoyo económico otorgado.

Al Dr. Celso Gutiérrez Martínez, quien dirigió el desarrollo de este trabajo de investigación; al personal de laboratorio, el M.C. J. Alfredo Torres Fórtiz y el M.C. Jacobo Meza Pérez; y a los profesores del área de Ciencia y Tecnología del Espacio, quienes en conjunto me guiaron a través de sus comentarios, consejos y sugerencias en la realización de esta tesis.

A mi familia, amigos y seres queridos por su motivación y apoyo incondicional.

Para Azucena.

# Contenido

| Capítulo 1. Introducción                                        | 8    |

|-----------------------------------------------------------------|------|

| 1.1 Planteamiento del Problema                                  | . 12 |

| 1.2 Justificación                                               | . 13 |

| 1.3 Objetivos                                                   | . 13 |

| 1.3.1 Objetivo general                                          | . 13 |

| 1.3.2 Objetivos específicos                                     | . 14 |

| 1.4 Estructura del documento                                    | . 14 |

| 1.5 Referencias                                                 | . 16 |

| Capítulo 2. Arquitectura general de un esquema de comunicacion  | es   |

| satelitales en banda X                                          | . 17 |

| 2.1 Elementos básicos de un enlace de radiofrecuencia           | . 21 |

| 2.1.1 Osciladores                                               | . 21 |

| 2.1.2 Mezcladores                                               | . 24 |

| 2.1 3 Filtros                                                   | . 25 |

| 2.1.4 Amplificadores                                            | . 28 |

| 2.2 Conclusiones                                                | . 30 |

| 2.3 Referencias                                                 | . 31 |

| Capítulo 3. Arquitectura del subsistema de enlace ascendente en |      |

| banda X                                                         | . 33 |

| 3.1 Etapa de FI                                                 | . 34 |

| 3.1.1 Configuración de un oscilador en lazo de amarre de fase | :   |

|---------------------------------------------------------------|-----|

| (PLL)                                                         | 35  |

| 3.1.2 Modulador en cuadratura                                 | 53  |

| 3.2 Etapa de conversión ascendente de RF                      | 58  |

| 3.2.1 Oscilador de RF                                         | 58  |

| 3.2.2 Mezclador de frecuencias                                | 59  |

| 3.3 Conclusiones                                              | 60  |

| 3.4 Referencias                                               | 61  |

| Capítulo 4. Diseño y realización de la etapa de frecuencia    |     |

| intermedia                                                    | 65  |

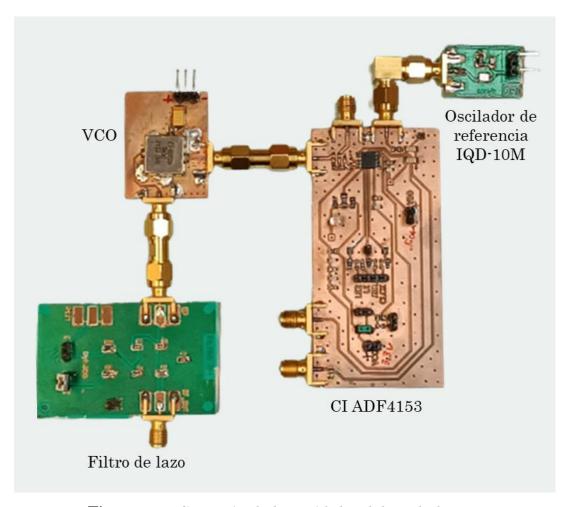

| 4.1 Oscilador de FI basado en PLL fraccional                  | 66  |

| 4.1.1 Oscilador de referencia                                 | 68  |

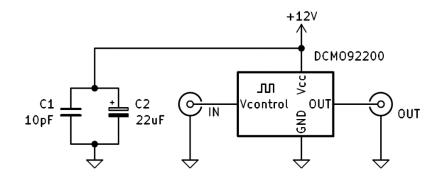

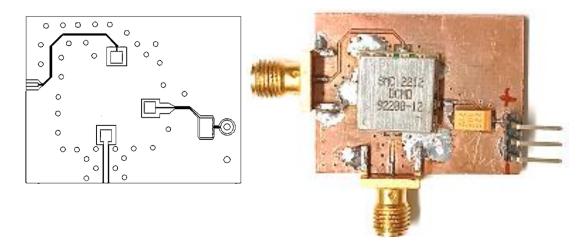

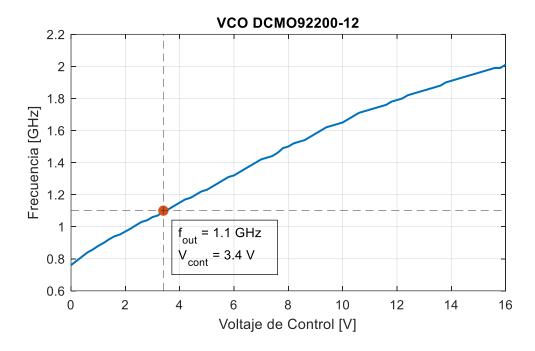

| 4.1.2 Oscilador controlado por voltaje (VCO)                  | 74  |

| 4.1.3 Filtro de lazo                                          | 76  |

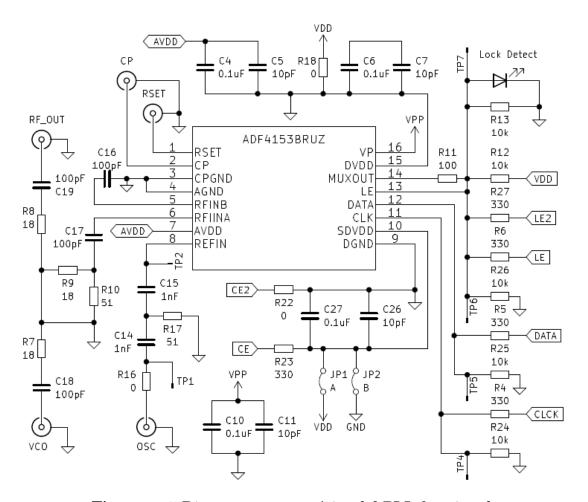

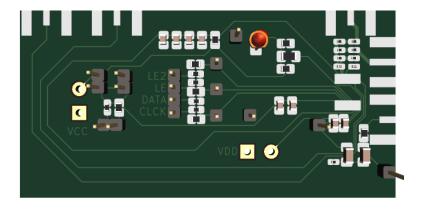

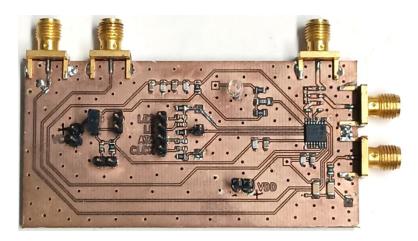

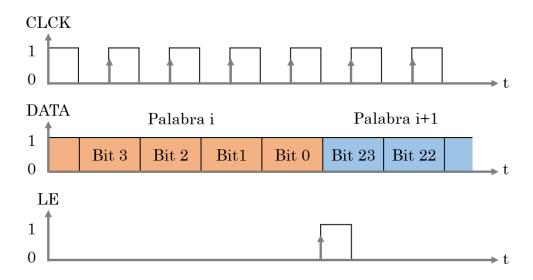

| 4.1.4 Detector de fase-frecuencia y divisor fraccional        | 79  |

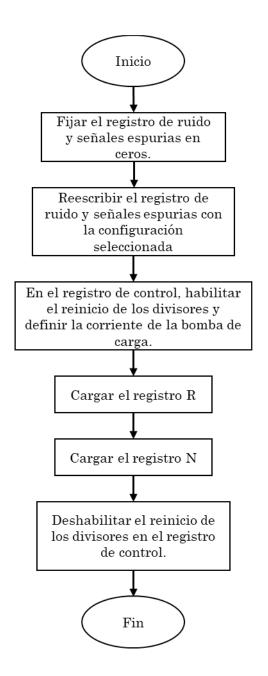

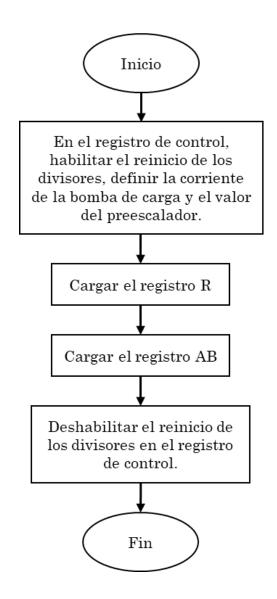

| 4.1.5 Programación de frecuencia de salida                    | 83  |

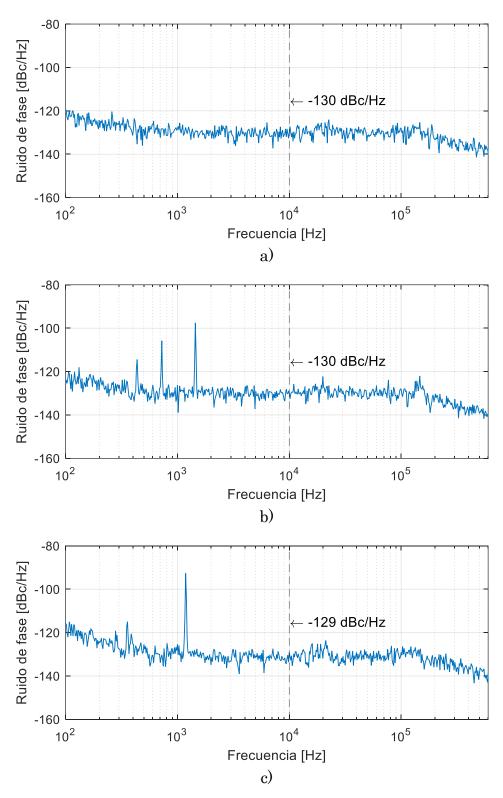

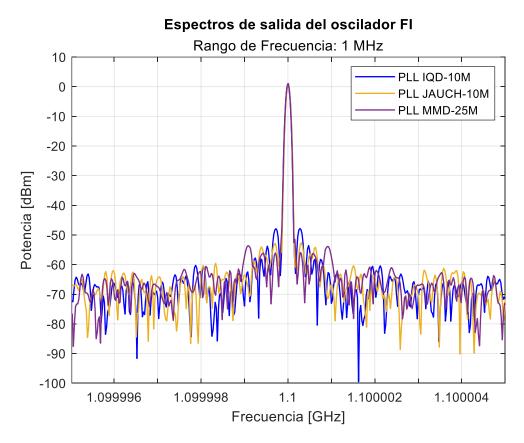

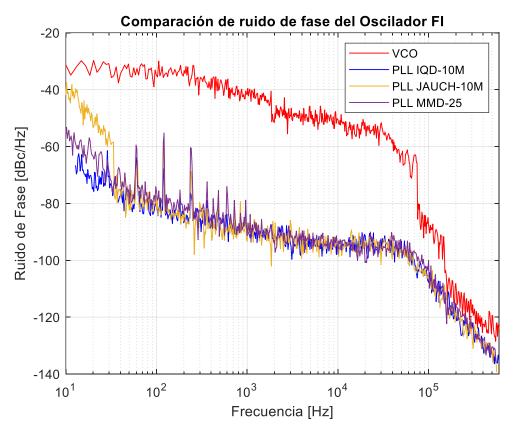

| 4.1.6 Prueba y caracterización del oscilador de FI            | 87  |

| 4.2 Integración, pruebas y caracterización de la etapa de FI  |     |

| modulada en cuadratura                                        | 92  |

| 4.3 Conclusiones                                              | 97  |

| 4.4 Referencias                                               | 98  |

| Capítulo 5. Convertidor de Subida a 7.2 GHz                   | 100 |

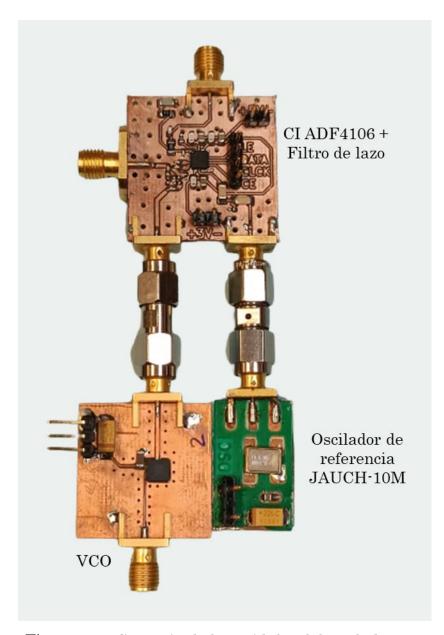

| 5.1 Oscilador del convertidor de subida RF basado en PLL      |     |

| fraccional                                                    | 101 |

| 5.1.1 Oscilador controlado por voltaje (VCO) 10                   | 12  |

|-------------------------------------------------------------------|-----|

| 5.1.2 Detector de fase-frecuencia, divisor fraccional y filtro de |     |

| lazo10                                                            | )4  |

| 5.1.3 Programación de frecuencia de salida 10                     | 18  |

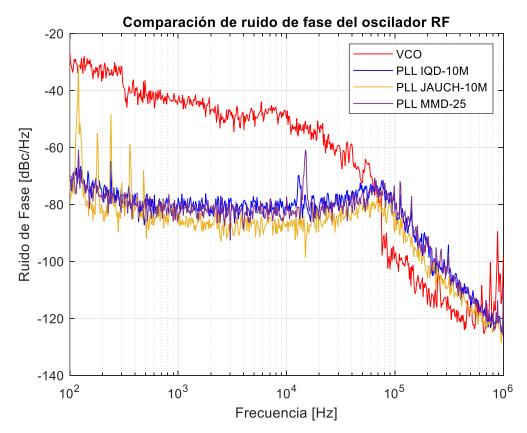

| 5.1.4 Prueba y caracterización del oscilador de 6.1 GHz 11        | . 1 |

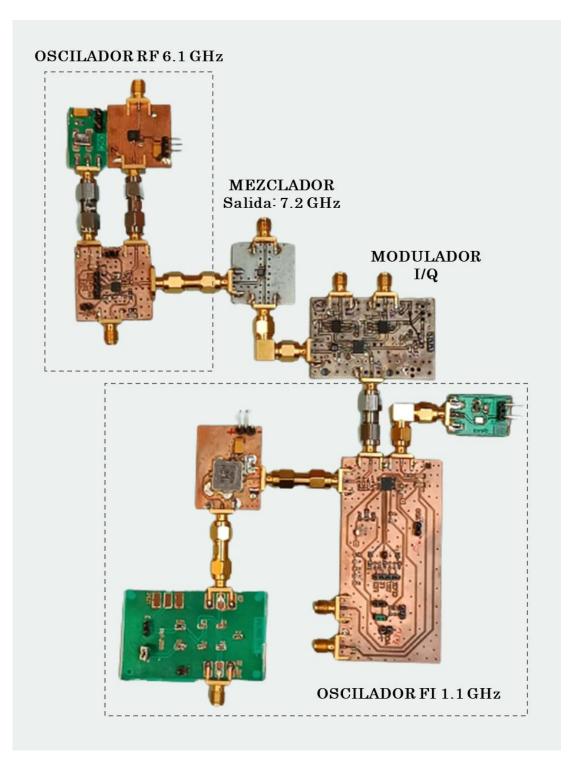

| 5.2 Integración del subsistema de enlace ascendente11             | 6   |

| 5.3 Conclusiones                                                  | 22  |

| 5.4 Referencias                                                   | 13  |

| Capítulo 6. Conclusiones y Trabajo Futuro12                       | 24  |

| Anexos. Trabajos Publicados                                       | 26  |

| Lista de Figuras12                                                | 27  |

| Lista de Tablas13                                                 | 32  |

# Capítulo 1

# Introducción

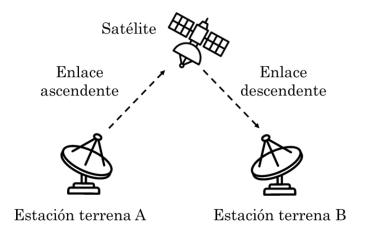

Un enlace de comunicaciones inalámbricas Tierra-Espacio-Tierra permite establecer y asegurar comunicación electrónica inalámbrica entre una estación terrena y satélites o vehículos espaciales, ubicados a grandes distancias, lejos de la superficie terrestre. Las comunicaciones son bidireccionales y se realizan mediante dos enlaces de transmisión, uno es el enlace ascendente Tierra-Espacio y el segundo es el enlace descendente Espacio-Tierra. El enlace ascendente es la ruta de transmisión de una señal de radiofrecuencia desde una estación terrena hacia un objeto en el espacio. El enlace descendente es la ruta de transmisión desde el espacio hacia una estación terrestre. Un esquema ilustrativo de los enlaces de comunicación mencionados se muestra en la Fig. 1.1. Por vía del enlace ascendente, un satélite o un vehículo espacial recibe señales de comunicación desde Tierra para el desarrollo de su misión espacial. El satélite o nave espacial, mediante el enlace descendente, responde a los mensajes recibidos desde Tierra o transmite la información que capta en el espacio, igualmente de acuerdo con la misión operativa. Las señales transmitidas desde el espacio viajan por el enlace descendente y son recibidas por estaciones terrenas que las distribuyen a los destinatarios finales.

En misiones espaciales de investigación espacial, los sistemas de comunicaciones inalámbricas emplean frecuencias de radio en la banda X (7.1 a 8.5 GHz) del espectro radioeléctrico, según asignación y regulación por la UIT [1]. La banda X asignada al servicio de investigación espacial

se divide en dos segmentos, la banda de 7.190 a 7.235 GHz se utiliza para enlaces de ascendentes, y la banda de 8.450 a 8.500 GHz para enlaces descendentes, en comunicaciones inalámbricas en el ambiente cercano a la tierra, cubriendo distancias de hasta 2 millones de km. Para distancias superiores a 2 millones de km, las bandas son 7.145 a 7.190 GHz para los enlaces ascendentes y 8.400 a 8.450 para los enlaces descendentes [2].

**Figura 1.1** Enlaces ascendente y descendente de un sistema de comunicaciones satelitales.

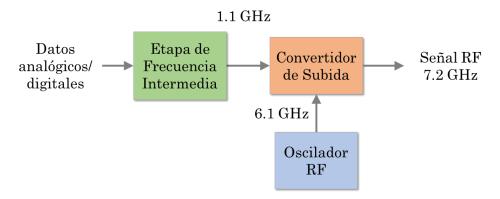

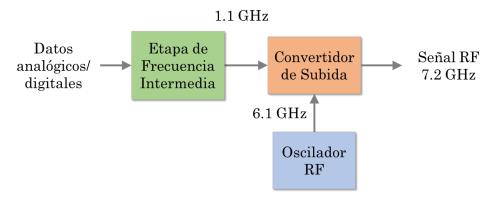

En el contexto general del trabajo de investigación y desarrollo de esquemas de comunicaciones inalámbricas en el INAOE, se trabaja en el desarrollo de esquemas prototipo de comunicaciones inalámbricas en las bandas L, S, X, K, Ka y ondas milimétricas, como plataforma experimental para el estudio de sistemas de comunicaciones terrestres y satelitales. En este marco de actividades, en este trabajo de tesis se describe el diseño y realización de un subsistema de enlace ascendente para comunicaciones inalámbricas en la banda X, con aplicación potencial en enlaces espaciales cercanas a la tierra. En esta propuesta, el enlace ascendente opera en la banda de 7.190-7.235 GHz. La configuración del

subsistema propuesto abarca el diseño y realización de una etapa de frecuencia intermedia, operando en una frecuencia de 1.1 GHz y de una etapa de conversión ascendente (conocida generalmente como convertidor "hacia arriba" o "up-conversion", por su terminología en el idioma inglés). La información transmitida hacia el espacio emplea una frecuencia portadora de 7.2 GHz.

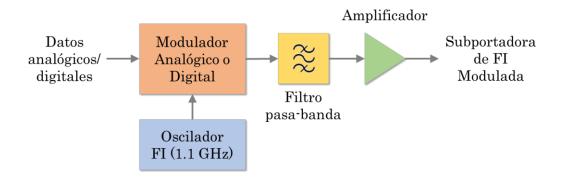

El primer componente del subsistema de enlace ascendente es la etapa de FI. La frecuencia de operación se ubica en la banda estandarizada de 0.95 a 1.45 GHz, la cual es ampliamente empleada en sistemas de comunicaciones satelitales. En esta tesis, la FI es de 1.1 GHz. La información de banda base que se transmite al espacio, modula la FI y se genera una señal modulada en algún formato analógico como modulación de amplitud (AM), frecuencia (FM), fase (PM) o en formatos digitales como OOK, FSK, PSK o sus variantes vectoriales BPSK, QPSK, QAM. La etapa de FI propuesta incluye un modulador en cuadratura (I/Q). La etapa de conversión ascendente, consiste de un oscilador local operando a 6.1 GHz y una etapa conversora de frecuencias, la cual traslada la FI hacia la frecuencia portadora en la banda X. La portadora de 7.2 GHz es transmitida conduciendo la información destinada a los objetos distantes en el espacio.

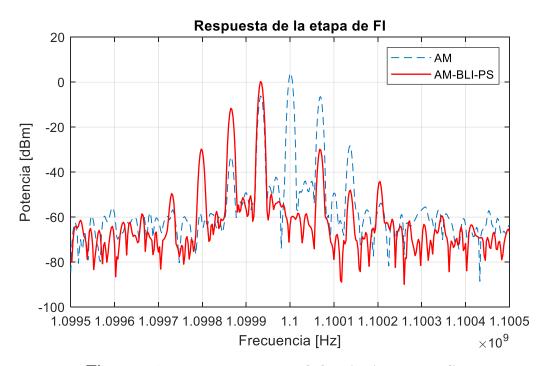

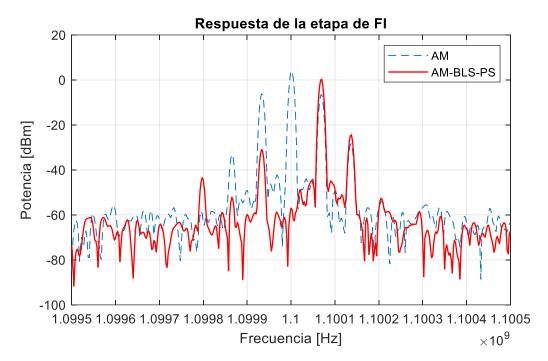

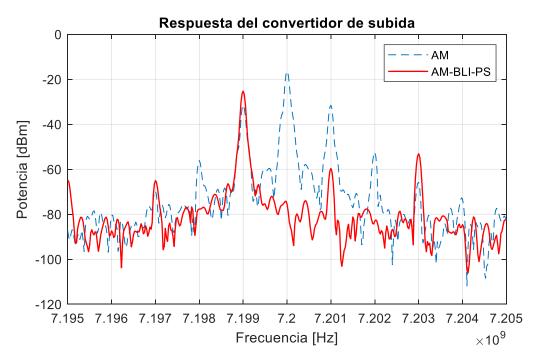

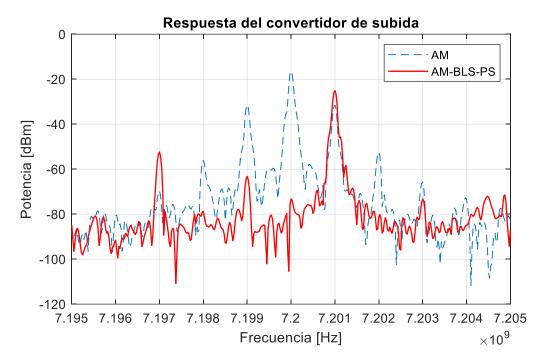

Para la configuración del subsistema de enlace ascendente, el desarrollo de tesis abarca el diseño, realización y caracterización de osciladores de 1.1 y 6.1 GHz, basándose en arquitecturas de circuitos en lazo de amarre de fase fraccionales (PLL fraccional) así como de un modulador de cuadratura para modulación con señales I/Q. En esta etapa de desarrollo, el modulador en cuadratura es empleado para generar, por una parte, modulación de amplitud (AM) clásica, la cual distribuye la información modulante en dos bandas laterales redundantes y concentra la mitad de la potencia en la presencia de la señal portadora. Este

esquema de modulación, ampliamente utilizado en esquemas de radiodifusión es ineficiente cuando los recursos de potencia y ancho de banda son limitados o deben optimizarse, como en el caso de las comunicaciones espaciales en la banda X. En esta tesis, se optimiza la modulación de amplitud, aprovechando el funcionamiento del modulador I/Q para generar un proceso de modulación de banda lateral única con supresión de portadora (AM-BLU-PS). Este tipo de modulación concentra la información en una sola banda lateral y no emplea potencia de portadora. De esta manera, la transmisión se optimiza, minimizando tanto el ancho de banda como la potencia requeridos en el enlace ascendente.

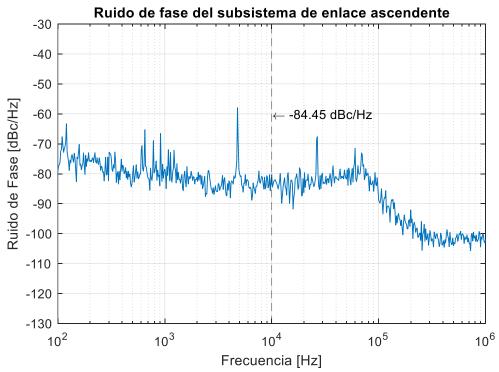

El desarrollo del subsistema de enlace ascendente requiere del diseño y realización de osciladores que presenten una gran estabilidad en la frecuencia generada, manteniendo desviaciones mínimas alrededor se la señal requerida, en el orden de algunas partes por millón. Además, las desviaciones de fase a corto plazo, efecto conocido como ruido de fase, también deben de ser mínimas. Adicionalmente, el espectro generado debe presentar únicamente la componente de la frecuencia requerida, sin presencia de señales armónicas, lo que da una medida de la pureza espectral. [3]. Los parámetros de estabilidad, ruido de fase y pureza espectral determinan el desempeño y calidad de un oscilador eficaz para comunicaciones inalámbricas de alto desempeño.

El subsistema de enlace ascendente en banda X requiere de una etapa de FI que premodule una subportadora con la información analógica o digital que requiera transmitirse. Por lo tanto, la sección de FI se diseña para contar con capacidad de modulación en cuadratura para la generación de modulación de amplitud en banda lateral única y portadora suprimida (AM-BLU-PS), y que puede convertirse en la base de esquemas de modulación digital más avanzados como los mencionados previamente

en este capítulo. La salida de FI alimenta la etapa de conversión ascendente mediante la mezcla de la señal de FI y el oscilador de 6.1 GHz para generar la frecuencia portadora de 7.2 GHz.

Otro componente esencial de los sistemas de comunicaciones inalámbricas es el mezclador, el cual traslada la señal de FI hacia una portadora de frecuencia más alta [4]. El proceso de mezcla es crítico ya que la traslación en frecuencias normalmente introduce frecuencias armónicas que deben minimizarse en potencia para evitar que contribuyan con distorsión y ruido en detrimento de la calidad de la comunicación.

El diseño, realización y caracterización de los diferentes elementos que constituyen e integran el subsistema de enlace ascendente se describen los capítulos subsecuentes de esta tesis. En el capítulo 5 se describe la integración y prueba del subsistema de enlace ascendente en banda X propuesto, mientras que en los documentos anexos se presentan las publicaciones realizadas a partir de los resultados obtenidos.

## 1.1 Planteamiento del Problema

En este trabajo, se documenta el diseño y la realización de un subsistema de enlace ascendente como componente principal de un esquema de comunicaciones inalámbricas en la banda X para comunicaciones satelitales y espaciales en un medio espacial cercano a la Tierra.

El subsistema consiste en una sección de FI, alrededor de 1.1 GHz y de una etapa de conversión ascendente de RF, donde una señal de 6.1 GHz se mezcla con la FI para generar la frecuencia portadora de 7.2 GHz

Para el diseño y desarrollo del subsistema propuesto, se estudian los elementos y funcionalidades de los esquemas de FI y RF con objeto de desarrollar experimentalmente el subsistema ascendente en banda X.

### 1.2 Justificación

El estudio y desarrollo de esquemas de comunicaciones inalámbricas en banda X tiene interés académico y científico en razón que dicha banda está asignada y regulada para comunicaciones satelitales y espaciales. El enlace ascendente tierra-satélite en banda X se configura con una sección de FI, la cual es premodulada con la información analógica o digital que se debe transmitir. La etapa de conversión ascendente traslada la FI hacia la frecuencia portadora en la banda X y esta última es transmitida hacia el espacio libre conduciendo la información destinada a los objetos distantes de la superficie terrestre.

El desarrollo del subsistema de enlace ascendente, comprendiendo la sección de FI con capacidad de modulación en cuadratura y la sección de conversión de subida, es el objetivo principal de esta tesis. El esquema de enlace ascendente representa un avance importante para implementar una plataforma experimental de comunicaciones inalámbricas en la banda X, esto promueve la generación de capacidades y la apropiación de tecnologías de RF que permitan el desarrollo de sistemas de comunicaciones inalámbricas terrestres y satelitales en el país.

## 1.3 Objetivos

## 1.3.1 Objetivo general

Diseño y realización de un subsistema de enlace ascendente de comunicaciones inalámbricas satelitales y espaciales en banda X (7.2 GHz).

## 1.3.2 Objetivos específicos

- Diseñar y realizar experimentalmente osciladores de FI y RF mediante técnicas de división fraccional que opere en esquema de lazo de amarre de fase (PLL).

- Integrar una sección de FI mediante el oscilador de FI y un modulador en cuadratura para una capacidad de modulación analógica y digital.

- Diseñar y realizar una etapa de conversión ascendente para trasladar la FI a una portadora de RF en la banda X (7.2 GHz).

## 1.4 Estructura del documento

Este trabajo de tesis presenta la siguiente organización de capítulos:

- 1. Introducción. Se presenta la descripción general del tema de investigación. Incluye el planteamiento del problema, la justificación, así como el objetivo general y los objetivos específicos.

- 2. Arquitectura general de un esquema de comunicaciones satelitales en banda X. Se describen los rangos de frecuencia y aplicaciones específicas de las comunicaciones en banda X. Además, se proporciona una descripción de la arquitectura general de un esquema transmisor-receptor de banda X y se describen los componentes que lo integran y sus funciones en el esquema.

- 3. Arquitectura del subsistema de enlace ascendente. Se presenta el propósito de la etapa de FI como herramienta en el procesamiento de señales en un esquema de comunicaciones y se describe su arquitectura específica. Además, se examinan específicamente los dos elementos clave de esta sección: el oscilador

basado en lazo de amarre de fase (PLL) programable y el modulador en cuadratura. Por otra parte, en la etapa de conversión de RF se presenta el proceso trasladar la FI a una frecuencia de 7.2 GHz empleando un mezclador de frecuencias.

- 4. Diseño y realización de la etapa de frecuencia intermedia (1.1 GHz). La sección de FI comprende el diseño y realización de un oscilador de FI en 1.1 GHz y de un circuito modulador de señales en cuadratura, además se detallan las consideraciones de diseño y selección de componentes de un PLL fraccional, así como su fabricación y pruebas de funcionamiento por etapas. El oscilador de FI se prueba empleando tres diferentes osciladores de referencia y se mide el espectro generado y el ruido de fase para cada oscilador de referencia. Una vez que el oscilador genera la FI, esta señal se modula con señales en cuadratura para generar un esquema de modulación de amplitud de banda lateral única y portadora suprimida (SSB-SC).

- 5. Convertidor de frecuencia hacia la banda X (7.2 GHz). En este capítulo se describe el diseño y realización de la etapa correspondiente al convertidor subida del enlace de comunicaciones ascendente. Se documenta el diseño y realización del oscilador de RF en 6.1 GHz. La mezcla de 6.1 GHZ con la FI de 1.1 GHz, genera el traslado de la FI a una banda de frecuencias alrededor de 7.2 GHz. El enlace de subida se caracteriza mostrando la capacidad de conversión de subida de la señal de FI modulada en modulación de amplitud en banda lateral única y portadora suprimida (AM-SSB-SC). Este formato hace eficiente la conversión de subida ya que optimiza el uso del ancho de banda alrededor de 7.2 GHz.

6. Conclusiones y trabajo futuro. Se presentan las principales contribuciones de la investigación relacionadas con el diseño, realización y desempeño del esquema de enlace ascendente para comunicaciones inalámbricas en la banda X, además, se sugieren propuestas y posibles vías para futuras investigaciones o extensiones del trabajo realizado.

## 1.5 Referencias

- [1] Unión Internacional de Telecomunicaciones (UIT), "Reglamento de radiocomunicaciones," pp. 149-153, Edición 2020, https://www.itu.int/en/publications/ITU-R/pages/publications.aspx?parent=R-REG-RR-2020&media=electronic

- [2] Davarian, F., Babuscia, A., Baker, J. M., Hodges, R., Landau, D., Lau, C., Lay, N., Angert, M., & Kuroda, V. (2020). Improving Small Satellite Communications in Deep Space—A Review of the Existing Systems and Technologies With Recommendations for Improvement. Part I: Direct to Earth Links and SmallSat Telecommunications Equipment. IEEE Aerospace and Electronic Systems Magazine, 35(7), 8–25. https://doi.org/10.1109/maes.2020.2980918

- [3] Westra, J., Verhoeven, C., & Van Roermund, A. (1999). Noise in oscillators. En Springer eBooks (pp. 69–82). https://doi.org/10.1007/978-1-4757-6117-7\_4

- [4] Marki, F., & Marki, C. (2010). *Mixer Basics Primer: A Tutorial for RF* & *Microwave Mixers*. Marki Microwave, Inc.

# Capítulo 2

# Arquitectura general de un esquema de comunicaciones satelitales en banda X

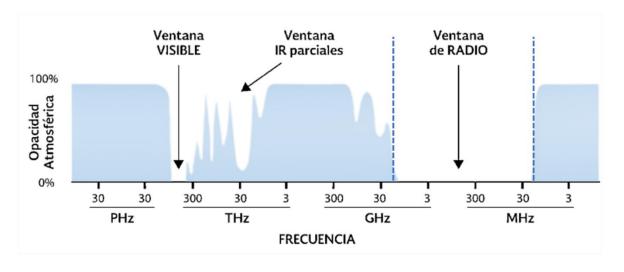

Las comunicaciones de radiofrecuencia terrestres, satelitales y espaciales transmiten información mediante ondas electromagnéticas, las cuales se propagan por la atmósfera o el espacio libre. El espectro electromagnético general se muestra en la Fig. 2.1.

La propagación de las ondas electromagnéticas en la atmósfera se ve afectada por la absorción y dispersión por la materia que la constituye. En consecuencia, la atmósfera es transparente en algunas bandas de frecuencia; en otras, se comportará como un medio opaco, y es una barrera para la propagación electromagnética [1].

Figura 2.1 Ventanas del espectro electromagnético.

Las comunicaciones de radiofrecuencia ocupan diferentes bandas de frecuencias, conocidas como el "espectro radioeléctrico", de acuerdo con el tipo de servicio asignado por la regulación internacional de servicios de radiocomunicaciones de la Unión Internacional de Telecomunicaciones (UIT) [2].

El espectro radioeléctrico (ventana de radio), señalado en la Figura 2.1., abarca frecuencias entre 30 MHz y 30 GHz. la banda de radio, que es un recurso limitado, está asignado a diferentes servicios, tales como transmisiones de radio y televisión, multiplicidad de comunicaciones terrestres, comunicaciones satelitales geoestacionarias, sistemas de posicionamiento global (GPS), satélites de orbita baja de observación de la Tierra, meteorología, aeronavegación, comunicaciones espaciales, etc. [1]. Las bandas de frecuencia para comunicaciones espaciales con fines de investigación, asignadas por la UIT, se enlistan en la Tabla 2.1 [2]. Estas bandas se dividen en aplicaciones del espacio profundo y aplicaciones cercanas a la Tierra [3].

Tabla 2.1Bandas de frecuencia asignadas para la investigación espacial.

|          | Bandas para satélites a más<br>de 2 millones de km de la<br>Tierra [MHz] |                       | Bandas para satélites a<br>menos de 2 millones de km de<br>la Tierra [MHz] |                       |

|----------|--------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------|-----------------------|

|          | Enlace<br>ascendente                                                     | Enlace<br>descendente | Enlace<br>ascendente                                                       | Enlace<br>descendente |

| Banda S  | 2110 - 2120                                                              | 2290 - 2300           | 2025 - 2110                                                                | 2200 - 2290           |

| Banda X  | 7145 - 7190                                                              | 8400 - 8450           | 7190 - 7235                                                                | 8450 - 8500           |

| Banda K  | _                                                                        | _                     | 22550 - 23150                                                              | 25500 - 27000         |

| Banda Ka | 34200 - 34700                                                            | 31800 - 32300         | _                                                                          | _                     |

Un enlace de comunicaciones Tierra-Espacio-Tierra, descrito en el capítulo anterior consiste de los enlaces ascendente y descendente. El enlace ascendente es la ruta de transmisión de una señal de radiofrecuencia desde una estación terrena a un satélite o nave espacial; el enlace descendente es la ruta de transmisión desde un satélite o nave espacial hacia una estación o receptor terrestre [4]. Como se estableció en el capítulo anterior, en esta tesis se aborda el diseño y realización de un subsistema de enlace ascendente con perspectiva de aplicación en comunicaciones satelitales y espaciales en la banda X.

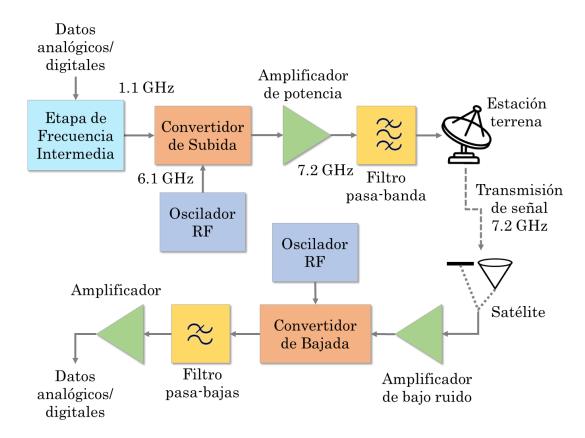

La Figura 2.2 muestra la arquitectura del enlace ascendente propuesto en este trabajo. El enlace ascendente opera en la banda de 7.190-7.235 GHz, la cual corresponde a aplicaciones de comunicaciones espaciales cercanas a la tierra. La información será transmitida hacia el espacio alrededor de una frecuencia central de 7.2 GHz. El primer componente del transmisor en la estación terrena es la etapa de FI operando en una frecuencia de 1.1 GHz. La información de banda base que se transmite al espacio, modula la FI y se genera una señal modulada en algún formato de modulación analógica, como modulación de amplitud (AM), frecuencia (FM), fase (PM) o bien en algún formato digital equivalente (OOK, FSK, PSK o sus variantes vectoriales como BPSK, QPSK, QAM), etc.)

El desarrollo de la etapa de FI incluye el diseño y realización de un oscilador de microondas en arquitectura de lazo de amarre de fase fraccional (fractional phase-locked loop, F-PLL), así como de un modulador en cuadratura (quadrature modulator, QM), el cual es el tema central de esta tesis y se describe en el capítulo 3.

Esta etapa entrega la FI premodulada en cuadratura al convertidor de subida que la eleva alrededor de la frecuencia de RF a 7.2 GHz.

posteriormente la señal se amplifica y se filtra para ser irradiada por una antena, típicamente parabólica, hacia el satélite.

Figura 2.2 Esquema de transmisión-recepción del enlace ascendente de comunicaciones satelitales en banda X.

En el receptor del satélite, la señal se recibe por medio de antenas planares o de tipo corneta [6]. Esta señal se amplifica y un circuito convertidor de bajada permite recuperar la FI premodulada. Después de la conversión de frecuencia, la señal se filtra y amplifica para proceder a un proceso de demodulación y recuperación de la información original enviada desde Tierra [5]. El circuito demodulador de FI está en proceso de desarrollo y fuera del alcance de esta tesis.

# 2.1 Elementos básicos de un enlace de radiofrecuencia

A continuación, se describirán los componentes principales del esquema de transmisión-recepción, incluyendo osciladores, amplificadores, mezcladores y filtros.

### 2.1.1 Osciladores

En los sistemas de comunicaciones terrestres y espaciales se emplean diversos tipos de osciladores para generar las señales portadoras de alta frecuencia. Estas señales presentan altos valores de estabilidad y pureza espectral. Estas características son críticas en las funciones de modulación, demodulación, sincronización y generación de señales de referencia [7].

Los principales tipos de osciladores en estas aplicaciones son los siguientes:

#### Osciladores de cristal:

Los osciladores a base de cristales de cuarzo aprovechan las propiedades piezoeléctricas del cuarzo, equivalentes a un circuito resonante para generar frecuencias de alta estabilidad. Son ampliamente utilizados ya que, además de su estabilidad, suelen ser de bajo costo y bajo ruido de fase. Los osciladores de cuarzo se utilizan para la generación de señales de reloj y como osciladores de referencia en esquemas de lazo de amarre de fase (PLL). La desventaja principal de los osciladores de cuarzo es que operan hasta frecuencias de 100 MHz. No es posible generar frecuencias de microondas mediante osciladores de cuarzo [8].

### - Osciladores controlados por voltaje (VCO):

Un VCO es un circuito generador de frecuencias en el cual un circuito resonante es modificado por medio de un voltaje de control. Este voltaje modifica fácilmente la capacitancia en el circuito resonante y el circuito oscilará en un intervalo relativamente amplio de frecuencias. Un VCO puede sintonizarse dinámicamente mediante variaciones de voltaje de control y de esta manera, permite generar frecuencias en las diferentes bandas que se utilizan en sistemas de comunicaciones inalámbricas terrestres, satelitales y espaciales. La principal desventaja de un VCO sintonizado en voltaje es su inestabilidad debida a variaciones de temperatura y voltaje. La frecuencia generada no es estable y presenta potencia alta en ruido de fase. Sin embargo, un VCO puede estabilizarse con muy alta eficiencia mediante un circuito en lazo de amarre de fase (PLL) [9].

#### - Osciladores en lazo de amarre de fase (PLL):

Un circuito PLL puede asociarse a un VCO con propósito de estabilizar la frecuencia generada. Un PLL opera mediante la comparación de fase entre dos señales de RF. Las señales que se comparan en fase son una señal de referencia con frecuencia  $f_1$  y la señal generada por el VCO de frecuencia  $f_2$ , dividida por un factor N que la aproxima a  $f_1$ . Las señales se comparan en fase y la diferencia genera un error de fase. El error de fase generado se convierte en un voltaje de control que estabiliza la frecuencia generada por el VCO. De esta manera, el VCO controlado por el circuito PLL permite la generación de señales de RF con alta estabilidad y ruido de fase mínimo [3]. En el capítulo 4 se describirá el diseño y realización del oscilador de FI, que constituye el tema

principal de esta tesis, basándose en un esquema de lazo de amarre de fase fraccional, para generar una FI de 1.1 GHz a partir de una frecuencia de referencia de 10 MHz. El oscilador de referencia es un oscilador de cristal de 10 MHz.

Un oscilador eficiente en sistemas de comunicaciones inalámbricas requiere cumplir con las siguientes características [10]:

- **Estabilidad.** Se requiere que las variaciones de frecuencia debidas a perturbaciones térmicas, mecánicas o eléctricas sean mínimas. la estabilidad se mide generalmente en partes por millón (ppm), expresadas por

$$Variación\ en\ Hz = \frac{f \cdot ppm}{10^6}$$

(2.1)

La estabilidad de un oscilador que genera una frecuencia central de 1 MHz será de 5 ppm cuando presente una variación máxima de 5 Hz alrededor de la frecuencia central.

- Pureza espectral. Esta característica describe el grado en que una señal presenta una frecuencia central única y sin componentes de ruido o señales armónicas no deseadas.

- Ruido de fase. Mide las fluctuaciones de fase a corto plazo de un oscilador y generalmente se expresa en decibeles por unidad de frecuencia desplazada desde la frecuencia portadora (dBc/Hz). Un gráfico de ruido de fase generado con un analizador de espectros muestra cómo la potencia del ruido de fase varía con el desplazamiento desde la frecuencia central.

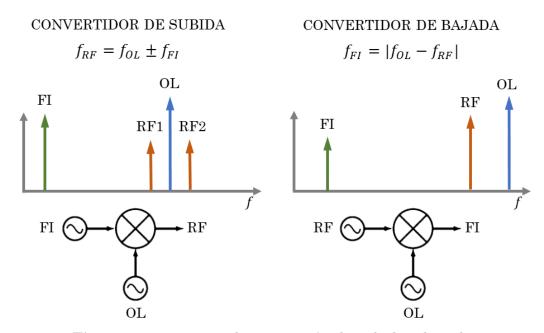

### 2.1.2 Mezcladores

Los circuitos mezcladores se emplean para multiplicar dos señales de frecuencias distintas, lo que permite generar la suma y la diferencia de las mismas. La suma genera un espectro alrededor de la frecuencia más alta, proceso conocido como traslación hacia arriba. Esto equivale a imprimir una señal de información de baja frecuencia alrededor de una frecuencia superior, la cual se convierte en la señal portadora. La diferencia de frecuencias da como resultado una señal de baja frecuencias, conocida como conversión de bajada, lo que permite extraer la información asociada a una señal portadora. [11].

Para realizar la multiplicación de señales, se aprovecha la no linealidad de componentes tales como diodos Schottky, transistores CMOS (semiconductor complementario de óxido metálico) o FET (transistor de efecto de campo) [12].

En el caso de los convertidores de subida, la señal en banda base o de FI se combina con la señal de un oscilador local para obtener una señal de RF:

$$f_{RF} = f_{OL} \pm f_{FI} \tag{2.2}$$

En el caso contrario, los convertidores de bajada combinan la señal de RF con la de un oscilador local para obtener una señal en banda base o de FI:

$$f_{FI} = |f_{OL} - f_{RF}| \tag{2.3}$$

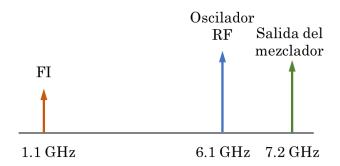

La Figura 2.3 muestra los espectros de frecuencia de ambos casos. Se puede observar que, para la conversión de subida, ambas frecuencias de suma y diferencia están disponibles en la salida del mezclador, como se indica en la Ecuación 2.2.

Este tipo de convertidor se conoce como convertidor doble banda lateral. Por otra parte, también es posible la conversión de subida de banda lateral única, en cuyo caso la suma o la diferencia de frecuencia se cancela dentro del mezclador. Este tipo de convertidores se denominan convertidores de subida de banda lateral única (BLU) o moduladores BLU [12].

Las señales convertidas pueden contener componentes no deseados y ruido, el cual será procesado posteriormente a través de filtros para obtener únicamente la frecuencia deseada.

Figura 2.3 Espectros de conversión de subida y bajada.

### 2.1 3 Filtros

En los sistemas de comunicación se emplean distintos tipos de filtros, ya sea para seleccionar rangos de frecuencia o para la eliminación de ruido o señales espurias no deseadas [13].

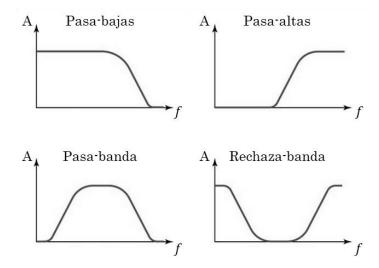

Las respuestas de los filtros que se observan en la Figura 2.4 son algunos de los más utilizados en los sistemas de comunicación y se describen a continuación:

- Filtros pasa-bajas (HPF). Permiten el paso de frecuencias más bajas que una frecuencia de corte seleccionada. Se emplean para remover ruidos de alta frecuencia u otras señales no deseadas.

- **Filtros pasa-altas (HPF).** Permiten el paso de frecuencias más altas que la frecuencia de corte. Se emplean para remover ruidos de baja frecuencia o señales de offset.

- Filtros pasa-banda (BPF). Permiten el paso de una banda de frecuencia específica mientras atenúan las frecuencias fuera de ese rango. Se emplean para separar señales, multiplexación de frecuencias y rechazo de interferencias.

- Filtros rechaza-banda o filtros Notch. Atenúan las frecuencias de una banda específica mientras que permite el paso de las frecuencias fuera de ese rango. Se emplean para suprimir interferencias o eliminar señales no deseadas en frecuencias específicas.

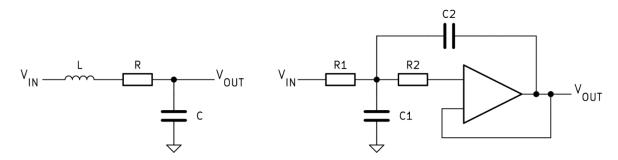

Figura 2.4 Tipos de filtros empleados en los sistemas de comunicación.

A frecuencias mayores a 1 MHz, los filtros mencionados se configuran con componentes pasivos como resistencias (R), inductores (L) y capacitores (C), en arreglos de circuitos RLC. Los filtros que operan en frecuencias hasta 100 MHz se diseñan y realizan con componentes RLC concentrados y operan con eficiencia. En este intervalo de frecuencias, también es posible diseñar y realizar filtros activos mediante amplificadores operacionales.

Los filtros activos son circuitos que utilizan un amplificador operacional como dispositivo activo en combinación con elementos RLC y proporcionan una ganancia en comparación con un filtro pasivo RLC. La Figura 2.5 muestra las configuraciones básicas de filtros pasivos y activos en régimen de baja frecuencia.

**Figura 2.5** Filtros de segundo orden: pasivo (izquierda) y activo (derecha).

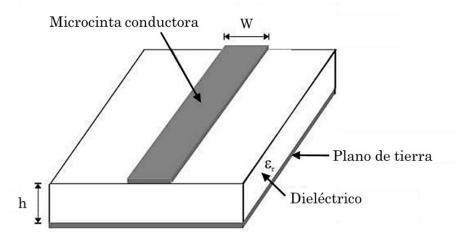

A frecuencias superiores a 500 MHz, los filtros se diseñan y construyen con circuitos de parámetros distribuidos y los elementos RLC son segmentos o tiras metálicas depositadas en substratos dieléctricos, como se ilustra en la Figura 2.6 [14]. De esta manera, los filtros de radiofrecuencia son estructuras de microcinta o guías de onda coplanares, las cuales aseguran un desempeño óptimo.

**Figura 2.6** Estructura de una microcinta con un ancho W, espesor h y una permitividad relativa  $\varepsilon_r$ .

## 2.1.4 Amplificadores

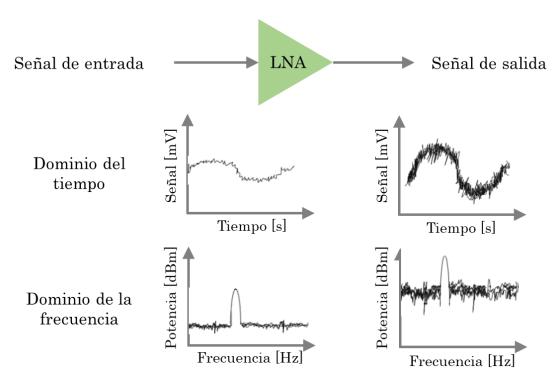

Los amplificadores de bajo ruido (LNA) y los amplificadores de potencia (PA) son ampliamente utilizados en los sistemas de comunicaciones.

El LNA está diseñado para amplificar señales débiles mientras introduce el menor ruido adicional posible. Por lo general, se usa en los receptores de comunicaciones para amplificar las señales entrantes de antenas u otras fuentes [15]. La Figura 2.7 ilustra este concepto en los dominios del tiempo y de la frecuencia.

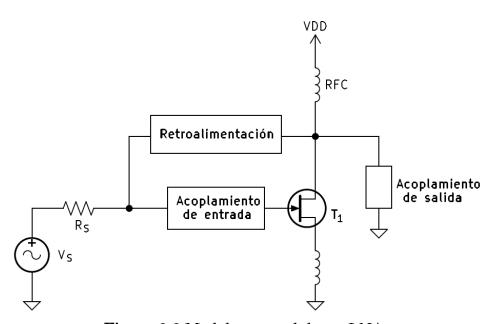

La Figura 2.8 muestra el diagrama del circuito general de un LNA construido alrededor de un transistor MOS (metal-óxido semiconductor) de canal N. RFC es la bobina de choque, cuyo valor es lo suficientemente grande como para asegurar una corriente continua a través del colector del transistor. Las señales de entrada y salida se presentan a través de redes de acoplamiento [16].

**Figura 2.7** Análisis conceptual del LNA y sus señales en dominios de tiempo y frecuencia con componentes de ganancia (deseada) y ruido (no deseado).

Figura 2.8 Modelo general de un LNA.

Por otra parte, los PA se emplean en los transmisores de un sistema de comunicaciones para amplificar las señales antes de que se transmitan a través de una antena. Éstos aumentan la potencia de la señal a niveles requeridos para las transmisiones de largo alcance [17].

La Figura 2.9 ilustra el diagrama general de un amplificador de potencia, donde  $R_L$  es la resistencia de carga y RFC es la bobina de choque. El filtro de salida puede incluir circuitos de sintonización armónica y modificador de ondas, acoplamiento de impedancias o cualquier otro circuito pasivo. El transistor  $T_1$  es mostrado como un transistor MOS de canal N [18].

Figura 2.9 Modelo general de un PA.

## 2.2 Conclusiones

Los conceptos presentados en este capítulo permiten conceptualizar y conocer el funcionamiento general de los elementos que integran a un sistema general de radiocomunicaciones en la banda X. Además, ubica a la etapa de FI dentro de este esquema y presenta las bases para el desarrollo de los siguientes capítulos, los cuales incluyen el diseño y

realización experimental de un oscilador en esquema de lazo de amarre de fase (PLL) empleado en la modulación de señales en cuadratura.

## 2.3 Referencias

- [1] Weeden, B. (2013). Radio Frequency Spectrum, Interference and Satellites. [Fact Sheet]. En Secure World Foundation. https://swfound.org/news/all-news/2013/06/swf-releases-new-fact-sheet-on-radio-frequency-spectrum-and-satellites

- [2] Unión Internacional de Telecomunicaciones (UIT), "Reglamento de radiocomunicaciones," pp. 149-153, Edición 2020, https://www.itu.int/en/publications/ITU-R/pages/publications.aspx?parent=R-REG-RR-2020&media=electronic

- [3] Davarian, F., Babuscia, A., Baker, J. M., Hodges, R., Landau, D., Lau, C., Lay, N., Angert, M., & Kuroda, V. (2020). Improving Small Satellite Communications in Deep Space—A Review of the Existing Systems and Technologies With Recommendations for Improvement. Part I: Direct to Earth Links and SmallSat Telecommunications Equipment. IEEE Aerospace and Electronic Systems Magazine, 35(7), 8–25. https://doi.org/10.1109/maes.2020.2980918

- [4] Maral, G., Bousquet, M., & Sun, Z. (2020). Satellite Communications

Systems: Systems, Techniques, and Technology (6a ed.). John Wiley & Sons.

- [5] Elbert, B. R. (2013). *Introduction to Satellite Communication* (3a ed.). Artech House.

- [6] Balanis, C. A. (2005). Antenna Theory: Analysis and Design. John Wiley & Sons.

- [7] Floyd, T. L. (2005). *Electronic Devices* (7ma ed.). Prentice Hall.

- [8] Crecraft, D. I., & Gergely, S. (2002). Analog Electronics. Circuits, Systems and Signal Processing. Elsevier Ltd. https://doi.org/10.1016/b978-0-7506-5095-3.x5000-4

- [9] Dai, L., & Harjani, R. (2003). Design of High-Performance CMOS Voltage-Controlled Oscillators. Springer. https://doi.org/10.1007/978-1-4615-1145-8

- [10] Chang, K. (2000). *RF and Microwave Wireless Systems*. Wiley-Interscience.

- [11] Steer, M. (2010). *Microwave and RF Design: A Systems Approach*. Scitech Pub Incorporated.

- [12] Marki, F., & Marki, C. (2010). *Mixer Basics Primer: A Tutorial for RF*& *Microwave Mixers*. Marki Microwave, Inc.

- [13] Chen, W. (2009). *Passive, Active, and Digital Filters* (2da ed). CRC Press.

- [14] Hong, J. G., & Lancaster, M. J. (2001). *Microstrip filters for RF/Microwave applications*. Wiley-Interscience.

- [15] Adsul, A. (2011). Design of Low Noise Amplifier for UWB Radio Receiver. International Journal of Engineering Science and Technology (IJEST), 3, 10.

- [16] Božanić, M., & Sinha, S. (2018). Millimeter-Wave low noise amplifiers. En Signals and communication technology. https://doi.org/10.1007/978-3-319-69020-9

- [17] Cripps, S. C. (2006). RF Power Amplifiers for Wireless Communications. Artech House Publishers.

- [18] Božanić, M., & Sinha, S. (2016). *Power amplifiers for the S-, C-, X-* and KU-bands. En Signals and communication technology. https://doi.org/10.1007/978-3-319-28376-0.

# Capítulo 3

# Arquitectura del subsistema de enlace ascendente en banda X

En este capítulo se presentan los diversos componentes que integran las dos etapas del subsistema de enlace ascendente desarrollado en el presente trabajo de tesis: la etapa de FI y la de conversión ascendente de RF hacia la banda X.

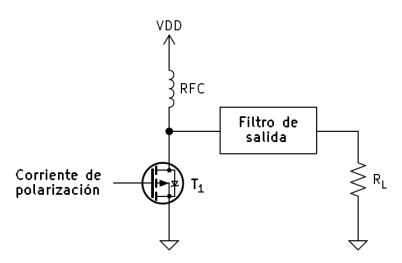

La integración de estas etapas se ilustra en la Figura 3.1, donde se observa el proceso por el cual el convertidor de subida traslada la subportadora modulada de 1.1 GHz a una señal de RF de 7.2 GHz, empleando un oscilador de 6.1 GHz.

Figura 3.1 Esquema general del subsistema de enlace ascendente

Es conveniente hacer notar que el subsistema desarrollado utiliza circuitos integrados comerciales. Sin embargo, el diseño de la arquitectura, su realización y prueba experimental requiere del estudio de las bases conceptuales y de la adquisición de los conocimientos para el

desarrollo tecnológico de circuitos y subsistemas de radiofrecuencia relativamente complejos. El desarrollo tecnológico de subsistemas de radiofrecuencia es un campo restringido en México y el aprendizaje y apropiación de estas tecnologías en el ámbito académico promueven la investigación y la formación de expertos en este campo. En el INAOE, es factible desarrollar tecnologías de radiofrecuencia con base en la disponibilidad de infraestructura especializada y de personal experto en el campo mencionado.

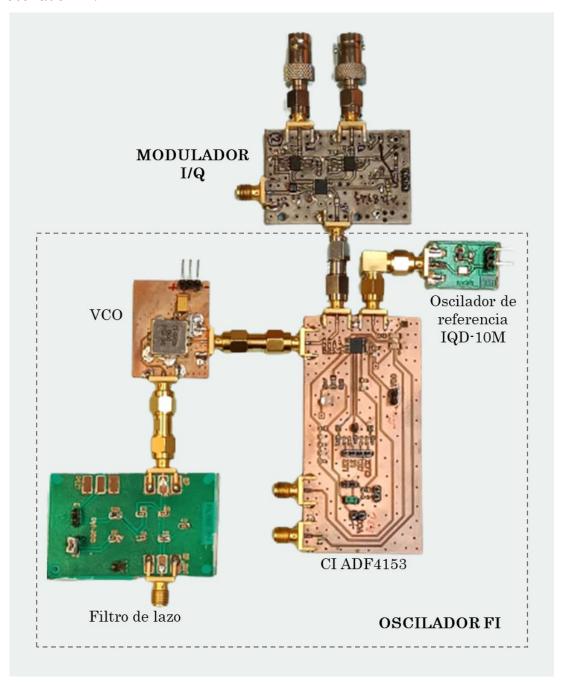

# 3.1 Etapa de FI

Como se mencionó en el capítulo anterior, la etapa de FI juega un papel vital en los sistemas de comunicaciones, ya que facilita la conversión de frecuencia permitiendo un procesamiento eficiente de la señal que se desea transmitir. El diagrama de bloques del esquema de FI se ilustra en la Figura 3.2.

**Figura 3.2** Esquema a bloques de la etapa de FI.

Como regla general, la selección de la FI supone que ésta sea de frecuencia superior a la máxima componente de frecuencia de la información que se desea transmitir. Las frecuencias intermedias más utilizadas son 10.7 MHz para transmisiones de video y TV, de 70 a 140

MHz en radioenlaces de comunicaciones de voz y datos y entre 950 y 1450 MHz en sistemas de comunicaciones satelitales [2]. Conforme a la temática de esta tesis, en este trabajo se propone generar y utilizar una frecuencia intermedia que aproveche componentes, módulos y subsistemas que operan en la banda de 950-1450 MHz, en el contexto de esquemas de comunicaciones satelitales. A partir de este último criterio, se propone una frecuencia intermedia de 1.1 GHz para el enlace de subida tierrasatélite en la banda X en una perspectiva potencial de comunicaciones satelitales y espaciales.

En las secciones siguientes se describen los principios teóricos de los elementos principales que integran la etapa de FI propuesta. El oscilador local se diseña y desarrolla en arquitectura de lazo de amarre de fase, basado en un circuito sintetizador fraccional programable. La etapa de FI comprende igualmente el desarrollo de un modulador de señales en cuadratura (I/Q).

# 3.1.1 Configuración de un oscilador en lazo de amarre de fase (PLL)

Un oscilador en lazo de amarre de fase (PLL) es un sistema retroalimentado que permite que un oscilador controlado por voltaje (VCO) genere una señal de radiofrecuencia de alta estabilidad, alta pureza espectral y ruido de fase mínimo, mediante la comparación de la fase de una señal de referencia y la señal de RF generada [3].

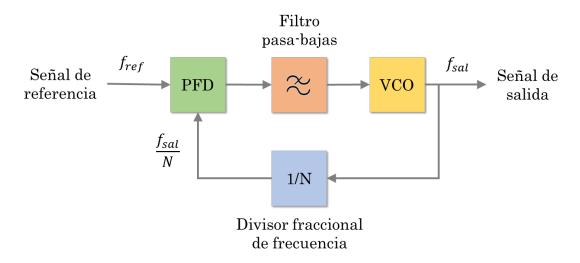

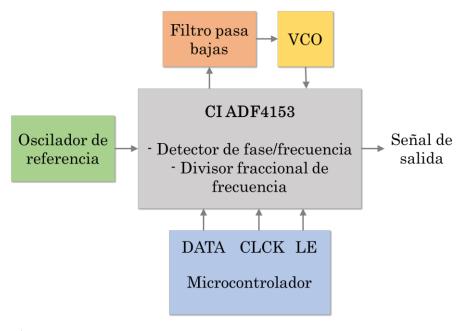

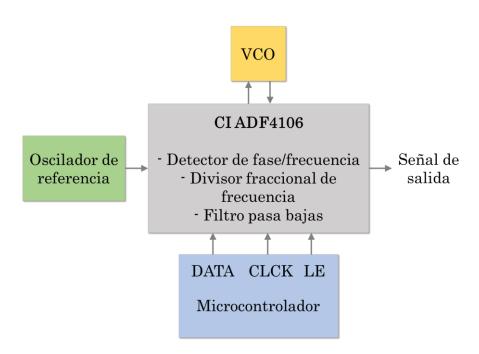

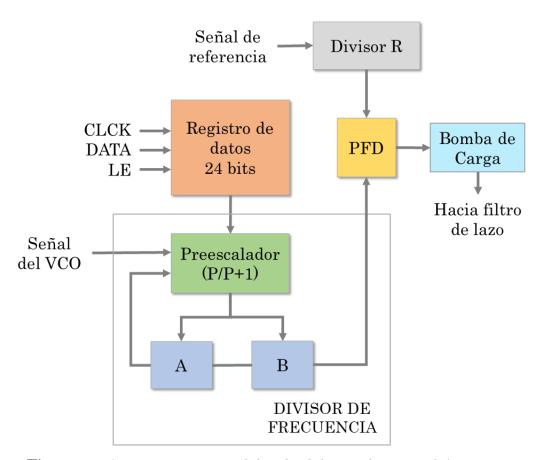

La Figura 3.3 muestra la topología básica de un oscilador PLL, el cual consiste en un detector de fase/ frecuencia (PFD), un filtro pasa-bajas, un VCO y un divisor de frecuencia, este último, en la trayectoria de retroalimentación del lazo [4].

Figura 3.3 Diagrama de bloques de un PLL.

Los elementos del oscilador PLL se describen a continuación:

- Detector de fase/frecuencia. Circuito comparador de las fases de dos señales que genera una señal de voltaje en proporción a la diferencia entre las fases. Las señales de entrada en un PFD son la señal de referencia con frecuencia  $f_{ref}$  y la señal de salida del oscilador controlado por voltaje (VCO). La señal del VCO se divide en frecuencia por un factor entero o fraccional para generar una señal con frecuencia  $f_{sal}/N$ , comparable a  $f_{ref}$ . El voltaje proporcional al error de fase se utiliza para controlar el voltaje de operación del VCO y de ese modo estabilizar la frecuencia generada.

- Filtro pasa-bajas. Elimina las componentes de alta frecuencia de la señal producida por el PFD y genera el voltaje de control del VCO para estabilizar la frecuencia de operación.

- Oscilador controlado por voltaje. Genera una señal oscilatoria cuya frecuencia es una función lineal de un voltaje de control.

- Divisor fraccional de frecuencia. Divide la frecuencia de la señal del VCO por un factor de división entero N o fraccional N.F.

Este factor es programado para generar diferentes frecuencias de salida.

Se dice que el PLL está amarrado o estabilizado cuando se cumple que

$$f_{sal} = N \cdot f_{ref} \tag{3.1}$$

Como se mencionó en el capítulo anterior, el VCO es sensible a perturbaciones térmicas, mecánicas o eléctricas. Cuando esto sucede, la frecuencia generada deriva ligeramente, en esta circunstancia, el PFD genera una señal de error y el PLL regresa a la condición de "amarre" o sintonía de la frecuencia de operación requerida.

A continuación, se describen algunos ejemplos de los elementos que integran un oscilador PLL.

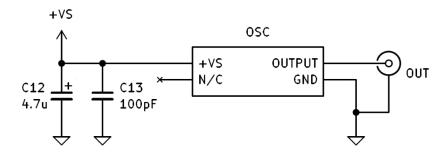

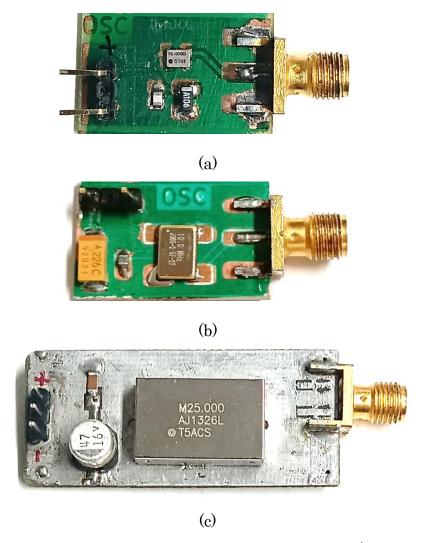

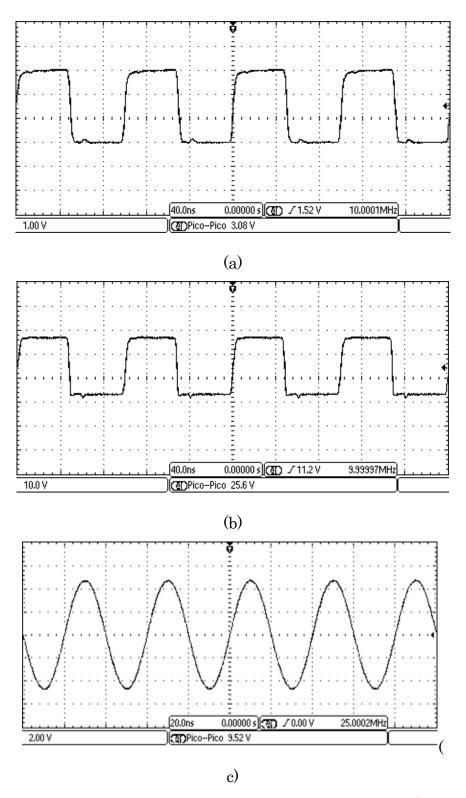

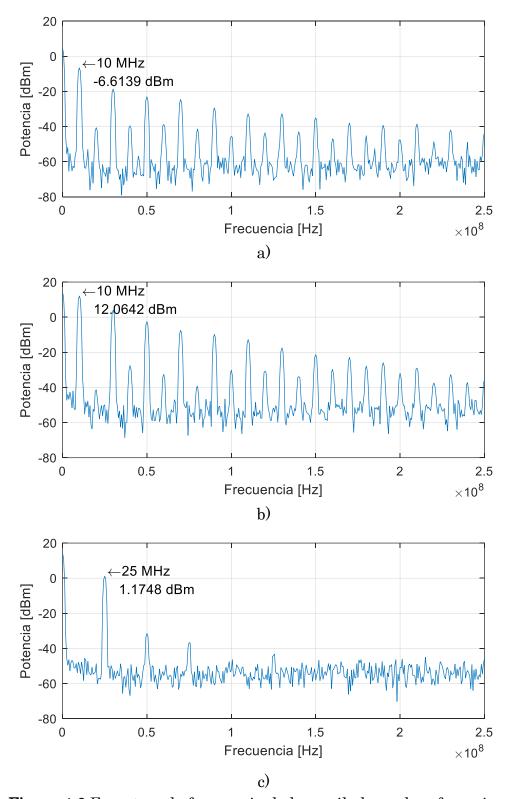

#### 3.1.1.1 Señal de referencia

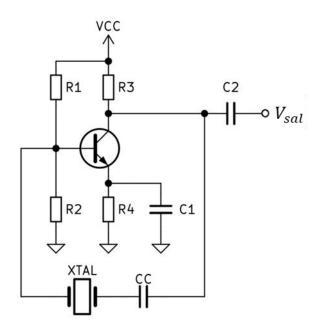

Los parámetros de estabilidad y ruido de fase del oscilador PLL dependen en gran medida de la estabilidad y calidad de la señal de referencia [4]. Como se mencionó en el capítulo anterior, los circuitos osciladores de cristal son los más empleados como generadores de señal de referencia debido a su gran estabilidad, bajo ruido de fase, bajo consumo de corriente y bajo costo.

Los osciladores de cristal aprovechan las propiedades piezoeléctricas de cristales de cuarzo, un material abundante en la naturaleza y de bajo costo [5]. Cuando se aplica al cristal una señal

periódica con frecuencia  $f_{ref}$ , cercana a su frecuencia de resonancia (la cual depende de sus dimensiones y del corte del cristal), un circuito oscilador genera una frecuencia de gran estabilidad [6].

La Figura 3.4 muestra un oscilador básico donde un cristal de cuarzo actúa como un circuito tanque resonante en serie.

Figura 3.4 Circuito oscilador controlado por un cristal de cuarzo.

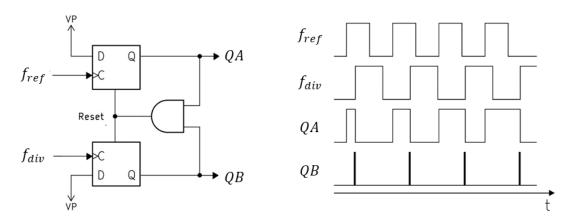

### 3.1.1.2 Detector de fase-frecuencia (PFD)

El PFD es un componente esencial en un PLL ya que permite detectar la diferencia de fase o frecuencia entre las señales de referencia y del VCO y la traduce en el voltaje de control que estabiliza la generación de frecuencia.

En la Figura 3.5 se muestra la unidad básica de un circuito detector de fase/frecuencia y consiste en dos "flip-flop" tipo D. En la misma figura se muestra el diagrama de tiempos de su funcionamiento básico, el cual se basa en la comparación de los flancos ascendente y descendente de las

señales de referencia  $(f_{ref})$  y de retroalimentación  $(f_{div} = f_{sal}/N)$  aplicadas a sus entradas de reloj (Clock) [7].

**Figura 3.5** Diagrama de un detector de fase-frecuencia y su comportamiento.

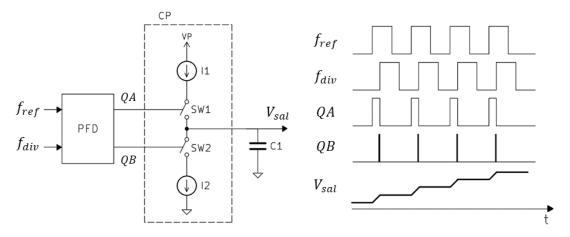

Dependiendo de las fases de las señales  $f_{ref}$  y  $f_{div}$ , la red lógica genera las salidas QA y QB. En el diagrama de tiempos, suponiendo que el estado inicial de las salidas es el nivel bajo (0), un flanco ascendente en la señal de referencia hace que la señal QA pase a estado alto (1). De igual manera, un flanco ascendente en la señal del VCO dividida,  $f_{div}$ , hace que la señal QB pase al estado alto. Cuando QA y QB se encuentran en nivel alto, la compuerta AND reinicia los flip-flops. Las salidas QA y QB permanecen en estado alto durante un tiempo  $\Delta T$ , el cual depende del retardo de propagación entre la salida de la compuerta AND y las salidas de los flip-flops. Los pulsos en las salidas QA y QB se traducen en la señal de control del VCO mediante el circuito de bombas de carga  $I_1$  e  $I_2$ , tal como se ilustra en la Fig. 3.6. Las bombas de carga, activadas por los pulsos en QA y QB, cargan o descargan un capacitor y el voltaje en sus terminales va a controlar el punto de operación del VCO. El circuito de

control se ilustra en la Figura 3.6. En éste, los interruptores  $SW_1$  y  $SW_2$  son activados por los niveles en QA y QB, respectivamente.

Este circuito operará en tres condiciones:

1. QA alto y QB bajo. Un pulso en QA activa  $SW_1$  durante  $\Delta T$  segundos, lo cual permite que la corriente  $I_1$  cargue al capacitor  $C_1$  mientras  $SW_2$  está desactivado. Por lo tanto, el voltaje de salida de la bomba de carga,  $V_{sal}$ , aumenta en una cantidad igual a

$$\Delta V_{sal} = \Delta T \frac{I_1}{C_1} \tag{3.2}$$

- 2. QB alto y QA bajo. El interruptor  $SW_2$  se activa, mientras que  $SW_1$  se desactiva, lo que hace que el capacitor se descargue y disminuya por tanto el voltaje de salida.

- 3. QA = QB. Los interruptores  $SW_1$  y  $SW_2$  se desactivan y el voltaje  $V_{sal}$  permanece constante

**Figura 3.6** Diagrama de un detector de fase-frecuencia con bomba de carga y su comportamiento.

Por lo tanto, se puede observar que el circuito de control produce un voltaje de salida en rampa escalonada, proporcional a las diferencias de fase de las señales de referencia y VCO dividida.

# 3.1.1.3 Oscilador controlado por voltaje (VCO)

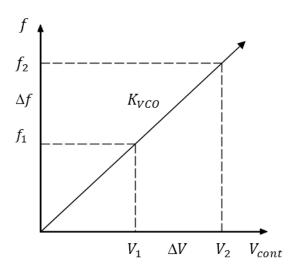

Un VCO es un circuito oscilador que genera una frecuencia en respuesta a un voltaje aplicado en su circuito resonante interno. En la Figura 3.7 se muestra la relación frecuencia/voltaje de un VCO. La frecuencia generada varía linealmente entre  $f_1$  y  $f_2$  a medida que el voltaje de control,  $V_{cont}$  varía entre  $V_1$  y  $V_2$  [7].

La sensibilidad del VCO,  $K_{VCO}$ , está determinada por la pendiente característica de la relación frecuencia-voltaje, expresada en Hz/V. Este parámetro está definido por la ecuación

$$K_{VCO} = \frac{f_2 - f_1}{V_2 - V_1} = \frac{\Delta f}{\Delta V} \tag{3.3}$$

donde  $\Delta f$  denota el cambio en la frecuencia y  $\Delta V$  el cambio en el voltaje.

**Figura 3.7** Respuesta ideal de un oscilador controlado por voltaje.

En un VCO ideal la frecuencia de salida es lineal con el voltaje de control. Por lo tanto, la frecuencia generada puede ser expresada por

$$fout = K_{VCO} \cdot V_{cont} + f_0 \tag{3.4}$$

donde  $f_0$  denota la frecuencia natural del VCO.

Los criterios de diseño de un PLL requieren asegurar que el intervalo de sintonía del VCO abarque la región lineal con propósitos de generar esquemas de modulación de frecuencia o fase eficientes en comunicaciones de alta frecuencia.

# 3.1.1.4 Filtro pasa-bajas

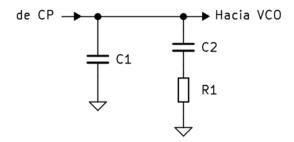

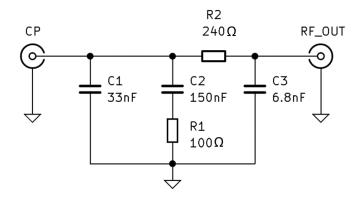

En un oscilador PLL, es común que el filtro de lazo sea un filtro pasa-bajas pasivo [9]. Los filtros pasa-bajas pueden ser de primer o segundo orden. La Figura 3.8 muestra la configuración de un filtro de segundo orden.

Figura 3.8 Filtro pasivo de segundo orden.

En el filtro pasivo, los componentes R1 y C2 determinan la respuesta en frecuencia. El capacitor de derivación C1 se emplea para evitar saltos de voltaje en el puerto de control del VCO debido a los cambios instantáneos en la salida de corriente de la bomba de carga [10].

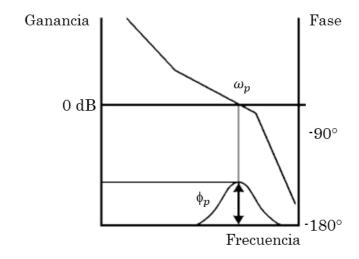

La Figura 3.9 ilustra los conceptos de ancho de banda del lazo,  $\omega_p$ , y margen de fase,  $\phi_p$  en un diagrama de Bode en un circuito PLL en lazo abierto. El ancho de banda  $\omega_p$  corresponde a la frecuencia a la cual la ganancia es unitaria (0 dB). El margen de fase está definido como la diferencia de fase existente entre 180° y la fase cuando la ganancia es unitaria. Un margen de fase menor de 90° asegura la estabilidad del PLL [10][11].

Figura 3.9 Diagrama de Bode de un PLL en lazo abierto.

En el dominio de Laplace, la función de transferencia de un filtro de segundo orden está dada por

$$Z(s) = \frac{1 + s \cdot C_2 \cdot R_1}{s \cdot (C_1 + C_2) \cdot \left(1 + s \cdot R_1 \frac{C_1 \cdot C_2}{C_1 + C_2}\right)}$$

(3.5)

Las constantes de tiempo que determinan los polos y ceros de la función de transferencia son

$$T_1 = R_1 \frac{C_1 \cdot C_2}{C_1 + C_2} \tag{3.6}$$

$$T_2 = R_1 \cdot C_2 \tag{3.7}$$

En términos del ancho de banda  $\omega_p$ , y del margen de fase,  $\phi_p$ , las constantes de tiempo son

$$T_1 = \frac{\sec \phi_p - \tan \phi_p}{\omega_p} \tag{3.8}$$

$$T_2 = \frac{1}{\omega_p^2 \cdot T_1} \tag{3.9}$$

Empleando las ecuaciones 3.6, 3.7, 3.8 y 3.9, se calculan los valores de los componentes C1, C2 y R1

$$C_{2} = \frac{T_{1}}{T_{2}} \cdot \frac{K_{\phi} \cdot K_{VCO}}{\omega_{p}^{2} \cdot N.F} \sqrt{\frac{1 + (\omega_{p} \cdot T_{2})^{2}}{1 + (\omega_{p} \cdot T_{1})^{2}}}$$

(3.10)

$$C_2 = C_1 \cdot \left(\frac{T_2}{T_1} - 1\right) \tag{3.11}$$

$$R1 = \frac{T_2}{C_2} \tag{3.12}$$

donde

$K_{\phi}=$  Constante del detector de fase/bomba de carga:  $I_{cp}/2\pi$ . Donde  $I_{cp}$  es la corriente de la bomba de carga.

$K_{VCO}$  = Sensibilidad del VCO (Ecuación 3.2).

$N.F = \frac{\text{Relación de división fraccional entre la frecuencia de salida del VCO y la frecuencia referencia: <math>f_{sal}/f_{ref}$ .

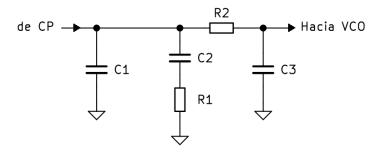

En las comunicaciones inalámbricas, las señales espurias y el ruido de conmutación que se generan en el divisor y la bomba de carga requieren limitarse a niveles mínimos [10]. Por lo tanto, en la síntesis de frecuencia es necesario optimizar el filtro de lazo, agregando una sección que rechace las señales laterales espurias. La adición de una resistencia en serie y un capacitor en derivación a la entrada del VCO asegura mayor

atenuación de las señales no deseadas. Esta configuración se conoce como filtro de lazo de tercer orden, como se ilustra en la Figura 3.10.

Figura 3.10 Esquema de un filtro de lazo pasivo de tercer orden.

En relación con los valores de los componentes adicionales, el producto de R2 y C3 debe ser aproximadamente 1/10 del producto de R1 y C2 [9]:

$$R_2 \cdot C_3 \cong \frac{R_1 \cdot C_2}{10} \tag{3.13}$$

A continuación, se describe el diseño de un filtro de lazo con ancho de banda de 100 kHz con las características mostradas en la Tabla 3.1.

**Tabla 3.1** Especificaciones de diseño de un filtro de lazo de tercer orden.

| Parámetro                               | Especificación      |  |

|-----------------------------------------|---------------------|--|

| Frecuencia de salida del VCO $f_{sal}$  | 1.1 GHz             |  |

| Frecuencia de referencia $f_{ref}$      | $10~\mathrm{MHz}$   |  |

| Ancho de banda BW                       | $25~\mathrm{kHz}$   |  |

| Margen de fase $\phi_p$                 | 45°                 |  |

| Constante del detector de fase $K_\phi$ | 2.5 mA/rad          |  |

| Sensibilidad del VCO $K_{VCO}$          | $78~\mathrm{MHz/V}$ |  |

Expresando los valores del margen de fase y del ancho de banda en radianes y radianes por segundo, respectivamente, se tiene que

$$\phi_p = 45^\circ \cdot \frac{\pi}{180^\circ} = 0.7854 \ rad$$

$$\omega_p = BW \cdot 2\pi = (25 \times 10^3)(2\pi) = 1.57 \times 10^5 \ rad/s$$

A partir de las ecuaciones 3.8 y 3.9 se calculan las constantes de tiempo  $T_1$  y  $T_2$ :

$$T1 = \frac{\sec \phi_p - \tan \phi_p}{\omega_p} = \frac{\sec(0.7854)}{628 \times 10^3} = 2.63 \,\mu s$$

$$T2 = \frac{1}{\omega_p^2 \cdot T_1} = \frac{1}{(628 \times 10^3)^2 (0.6592 \times 10^{-6})} = 15.39 \,\mu s$$

Posteriormente, se calculan los valores de C1, C2 y R1 con las ecuaciones 3.10-3.12, donde

$$N.F = \frac{f_{sal}}{f_{ref}} = \frac{1.1 \times 10^9}{10 \times 10^6} = 110$$

$$C_1 = \frac{T_1}{T_2} \cdot \frac{K_{\phi} \cdot K_{VCO}}{\omega_p^2 \cdot N.F} \sqrt{\frac{1 + (\omega_p \cdot T_2)^2}{1 + (\omega_p \cdot T_1)^2}}$$

$$= \frac{2.63 \times 10^{-6}}{15.39 \times 10^{-6}} \cdot \frac{(2.5 \times 10^{-3})(78 \times 10^6)}{(1.57 \times 10^5)^2(110)} \sqrt{\frac{1 + (1.57 \times 10^5 \cdot 15.39 \times 10^{-6})^2}{1 + (1.57 \times 10^5 \cdot 2.63 \times 10^{-6})^2}}$$

$$= 29.7 \, nF$$

$$C_2 = C_1 \cdot \left(\frac{T_2}{T_1} - 1\right) = 29.7 \times 10^{-9} \cdot \left(\frac{15.39 \times 10^{-6}}{2.63 \times 10^{-6}} - 1\right) = 143.6 \, nF$$

$$R_1 = \frac{T_2}{C_2} = \frac{15.39 \times 10^{-6}}{143.6 \times 10^{-9}} = 106.96 \, \Omega$$

Finalmente, se eligen los componentes R2 y C3 cumpliendo con la condición de la ecuación 3.12 y suponiendo que

$$R_2 = 240\Omega$$

$$C_3 \cong \frac{R_1 \cdot C_2}{10 \cdot R_2} = \frac{(106.96)(143.6 \times 10^{-9})}{(10)(240)} = 6.4 \, nF$$

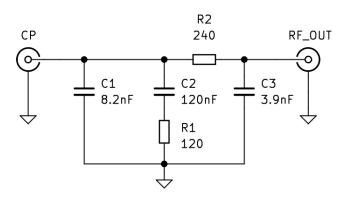

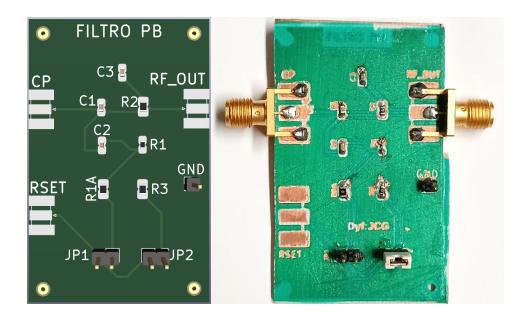

El filtro diseñado se muestra en la Figura 3.11, empleando los valores comerciales más cercanos a los valores calculados.

Figura 3.11 Filtro de lazo de tercer orden diseñado.

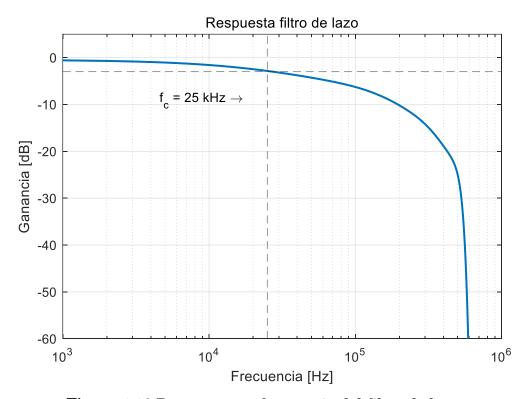

La respuesta simulada en lazo abierto del filtro se ilustra en la Figura 3.12. En ésta se observa que el ancho de banda del lazo se ubica en 25 kHz y el margen de fase es de 45°, comprobando así el correcto diseño del filtro.

Figura 3.12 Respuesta en lazo abierto del filtro diseñado

#### 3.1.1.5 Divisor de frecuencia

Un divisor de frecuencia es un circuito electrónico que permite escalar una señal con frecuencia  $f_1$  en una señal con frecuencia menor  $f_2$ . La relación de división (N) puede ser un valor entero o fraccional [12]. Distintas relaciones de división pueden ser logradas con diferentes arquitecturas como se describe a continuación.

#### 3.1.1.5.1 Divisor entero

La frecuencia sintetizada por un PLL que emplea divisores enteros es en general un múltiplo entero de la frecuencia de referencia  $f_{sal}=N\cdot f_{ref}.$

Una relación de división de número entero se logra de manera relativamente fácil con circuitos digitales en base binaria 2. Con circuitos biestables tipo "flip-flop", es factible realizar divisores de frecuencia con cocientes enteros  $2^n$ , con n entero.

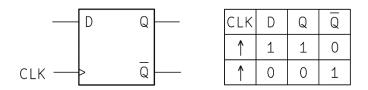

La Figura 3.13 ilustra el símbolo y la tabla de verdad del flip-flop tipo D, en el cual, la salida Q tendrá el mismo valor presente en la entrada de datos D en cada pulso ascendente de la señal de reloj CLK. Es decir, si D=1 y se aplica un pulso ascendente en la señal de reloj, el valor de Q se vuelve igual a 1 y  $\bar{Q}$  se vuelve igual a 0 [13].

Figura 3.13 Símbolo y tabla de verdad del flip-flop tipo D.

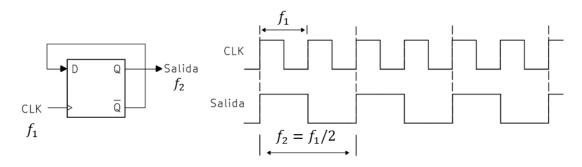

Una de las arquitecturas más comunes de divisores enteros de frecuencia se basa en contadores binarios que permiten programar la relación de división N [14]. La Figura 3.14 muestra un contador consistente en un flip-flop tipo D, que por su principio de funcionamiento es empleado como un divisor con relación de división de N=2. Aquí, la salida inversa  $\bar{Q}$  es conectada en un lazo de retroalimentación a la entrada D.

**Figura 3.14** Divisor por 2 con flip-flop tipo D y las señales de entrada y salida que muestran esta operación.

En el diagrama de tiempo se puede observar que los pulsos de la salida *Q* tienen una frecuencia igual a la mitad de la frecuencia de la señal de reloj de entrada, esto se presenta debido a que el flip-flop en esta configuración alterna de un estado al otro en cada ciclo de reloj.

Utilizando esta arquitectura, los flip-flops tipo D conectados en cascada permiten realizar división de frecuencias en distintos múltiplos enteros [14[15].

Una limitante crítica de los divisores de frecuencia de factores enteros en un PLL es que las frecuencias divididas son únicamente múltiplos de la frecuencia de referencia de entrada. En consecuencia, la resolución entre las frecuencias está limitada a  $f_{ref}$ . En la necesidad de resolver frecuencias con valores arbitrarios, se recurre al uso de divisores de frecuencia fraccionales. Estos divisores determinan la eficiencia de osciladores y sintetizadores de frecuencia en arquitecturas PLL en los

sistemas se comunicaciones inalámbricas preponderantes en la actualidad [16].

#### 3.1.1.5.2 Divisor fraccional

La frecuencia sintetizada por un PLL que emplea divisores fraccionales es en general un múltiplo no entero de la frecuencia de referencia:

$$f_{sal} = \left(N + \frac{k}{M}\right) \cdot f_{ref} \tag{3.14}$$

donde k y M son números enteros. La variable M es conocida por "módulo fraccionario" o "denominador fraccionario". El entero k toma cualquier valor entre 0 y M. El número fraccional (N + k/M) se identifica como N.F, donde el punto denota un punto decimal y N y F representan las partes enteras y fraccionarias, respectivamente [12].

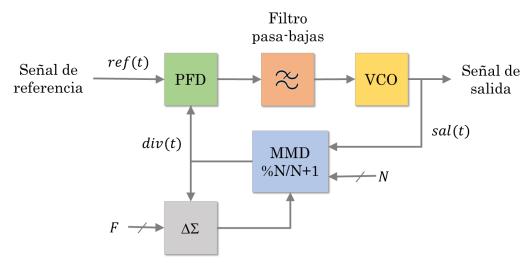

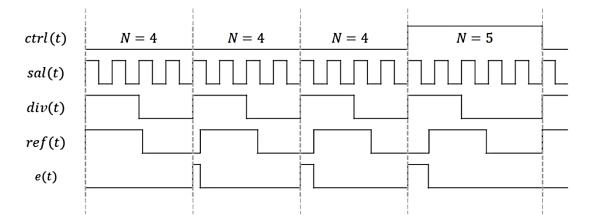

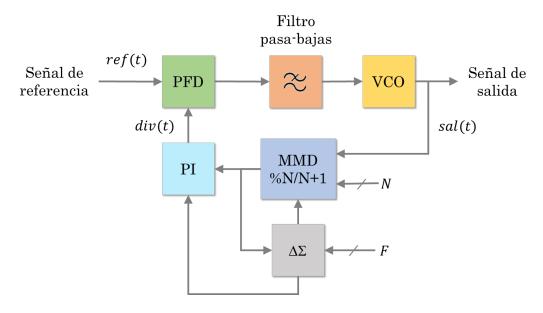

Las arquitecturas utilizadas por los divisores fraccionales se basan en los conceptos fundamentales de la división entera. En lugar de emplear un solo valor entero como divisor, se emplean dos valores: N y N+1, cuyo promedio a lo largo del tiempo representa el factor de división fraccional, como se explicará a en los siguientes párrafos. Este tipo de divisores son conocidos como divisores de módulo múltiple (MMD) cuyo control es realizado por un modulador  $\Delta\Sigma$  [17][18].

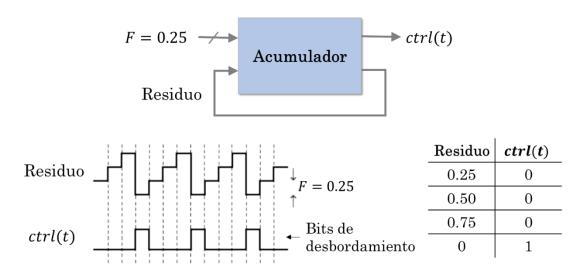

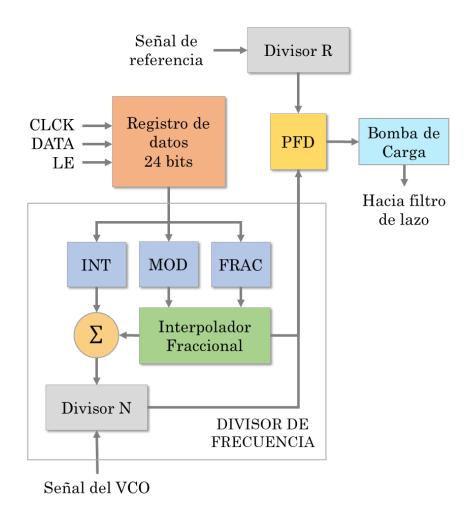

El diagrama de bloques de un PLL fraccional con modulador  $\Delta\Sigma$  se muestra en la Figura 3.15, donde N y F representan las palabras de programación para el factor de división fraccional N.F.

El modulador  $\Delta\Sigma$  de primer orden basa su funcionamiento en un acumulador digital, ilustrado en la Figura 3.16. Se muestra el ejemplo donde el valor de F=0.25 es acumulado en cada ciclo de reloj hasta producir un bit de "desbordamiento" en la salida, generando así la señal

de control, ctrl(t), para que el MMD cambie el factor de división de N a N+1.

Figura 3.16 Funcionamiento de un acumulador digital

Continuando con el ejemplo anterior, la Figura 3.17 ilustra el diagrama de tiempos de un MMD cuyos factores de división son alternados entre los valores 4 y 5. Se observa que la señal sal(t) es dividida por un factor de 4 durante 3 ciclos y por 5 durante un ciclo de manera repetitiva. El promedio de estos factores de división resulta en

$$N.F = \frac{4(3) + 5(1)}{4} = 4.25$$

**Figura 3.17** Diagrama de tiempos de las señales de un MMD, su comparación con una señal de referencia y el error que se genera.

Este método de división provoca una señal de error, e(t), debido a la diferencia de fase instantánea entre las señales de referencia y salida del divisor. Posteriormente, esta diferencia de fase se restablece al terminar el ciclo donde el factor de división es N+1. Sin embargo, como este error es periódico, crea señales espurias a la salida del PLL, lo que afecta su rendimiento y pureza espectral [18][19].

Para eliminar este error, se emplea un interpolador de fase (PI), el cual es esencial para alinear las fases de las señales que se generan en la alternación de los factores de división [19]. La integración de este bloque en el esquema de un oscilador PLL se muestra en la Figura 3.18.

Figura 3.18 Diagrama de bloques de un PLL fraccional que emplea un modulador  $\Delta\Sigma$  y un PI.

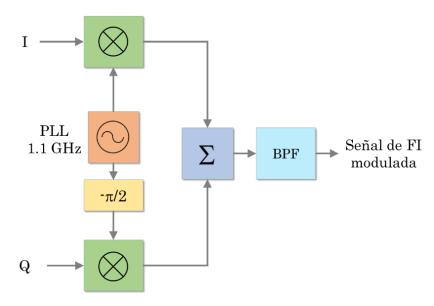

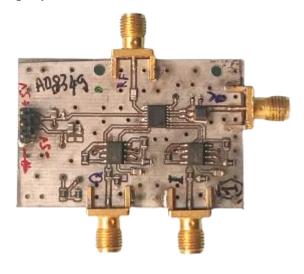

# 3.1.2 Modulador en cuadratura

El modulador en cuadratura, también llamado modulador I/Q, es ampliamente utilizado en radiocomunicaciones debido a que presenta un rendimiento mejorado en comparación con la clásica modulación en amplitud (AM), como se explica a continuación.

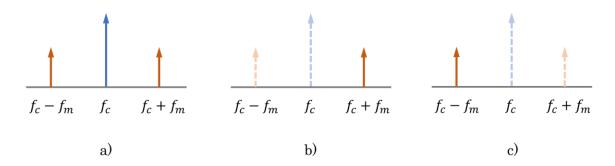

Los esquemas de AM clásicos presentan limitaciones en términos de eficiencia espectral y potencia. Su generación implica multiplicar una señal de información en banda base (voz, video, datos) con una señal portadora de más alta frecuencia. Esta multiplicación produce bandas laterales alrededor de la señal portadora, las cuales vuelven redundante la información transmitida ya que ambas son imágenes exactas entre sí.

Además, en este esquema de modulación la señal portadora no transmite información, pero sí concentra la mitad de la potencia disponible [20]. Por lo tanto, eliminar una de las bandas y la portadora genera modulación de amplitud de banda lateral única y portadora suprimida (AM-BLU-PS) [20][21].

La Figura 3.19 ilustra una comparación espectral de las modulaciones AM y AM-BLU-PS, siendo  $f_c$  la frecuencia de la señal portadora y  $f_m$  la frecuencia de la señal de información en banda base.

Figura 3.19 Espectros de frecuencia: a) AM clásica, b) AM-BLU-PS (superior), c) AM-BLU-PS (inferior).

Las principales ventajas de la modulación en BLU son las siguientes [20]:

- 1. Ahorro del 83% en potencia transmitida (66.7% por la eliminación de la señal portadora y 16.6% por la eliminación de una banda lateral).

- 2. El ancho de banda requerido se reduce al 50%, por lo tanto, se puede multiplexar el doble de canales en un mismo intervalo de frecuencia.

El proceso habitual para obtener AM-BLU-PS es mediante un modulador en cuadratura, el cual basa su funcionamiento en el procesamiento simultáneo de señales en fase (I) y en cuadratura (Q), las cuales son idénticas excepto que desfasadas 90° una respecto a la otra. De ahí la denominación señales en cuadratura [22].

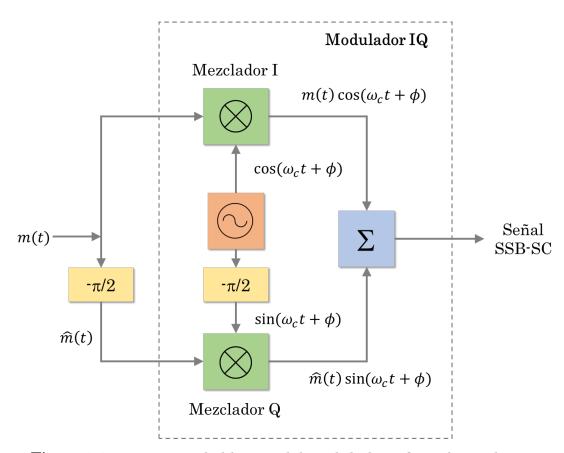

El esquema ilustrado en la Figura 3.20 muestra un modulador I/Q configurado para generar una señal AM-BLU-PS. Este modulador está integrado por un oscilador local, un bloque desfasador, dos mezcladores y una etapa de combinación de señales.

**Figura 3.20** Diagrama de bloques del modulador I/Q configurado para generar AM-BLU-PS.

En la mitad superior del esquema, la señal de mensaje, m(t), se multiplica por  $\cos(\omega_c t + \phi)$ , mientras que en la mitad inferior se generan y se multiplican las señales  $\widehat{m}(t)$  y  $\sin(\omega_c t + \phi)$ . Después,  $\widehat{m}(t)\sin(\omega_c t + \phi)$  y  $m(t)\cos(\omega_c t + \phi)$  se suman para producir la señal AM-BLU-PS [21][22].

La señal AM-BLU-PS resultante se expresa por

$$s_{SSR}(t) = m(t)\cos(\omega_c t + \phi) + \widehat{m}(t)\sin(\omega_c t + \phi)$$

(3.15)

Por otra parte, el modulador de cuadratura tiene la ventaja de que cualquier parámetro de la frecuencia portadora (amplitud, fase o frecuencia) puede manipularse simultáneamente para representar información, por lo que la estructura fundamental de un modulador en cuadratura forma también la base de los esquemas de modulación digital como la modulación por desplazamiento de fase en cuadratura (QPSK) y sus variantes [23].

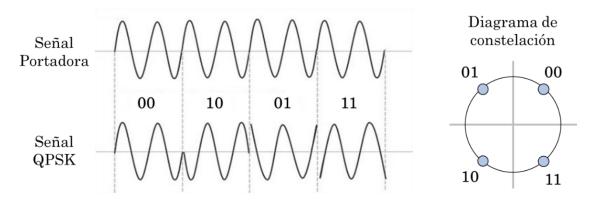

La modulación QPSK permite la codificación eficiente de datos digitales mediante el uso de cuatro cambios de fase diferentes de la señal portadora para representar dos bits de información por símbolo. En otras palabras, un símbolo de la modulación QPSK no representa un 1 o 0, sino que representa los valores 00, 01, 10, 11 dependiendo del cambio de fase como se muestra en la Figura 3.21. Los cuatro estados de salida tienen la misma amplitud y están separados 90°.

**Figura 3.21** Cambios de fase generados en la modulación QPSK y su correspondencia en símbolos digitales de dos bits.

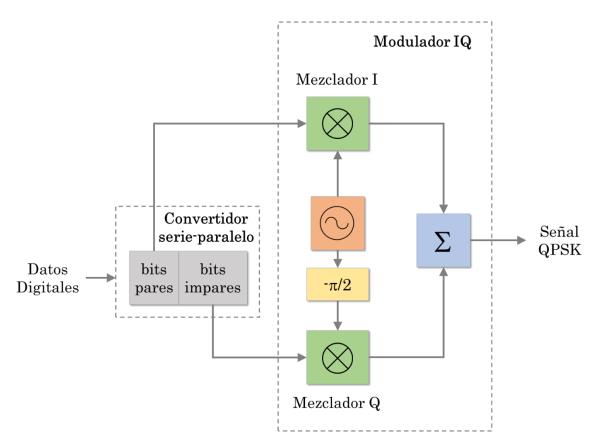

Las señales I/Q son fundamentales para controlar estos cambios de fase. La Figura 3.22 ilustra el modulador en cuadratura configurado para generar una señal QPSK. A la entrada del modulador I/Q, un convertidor serie/paralelo separa los bits de posición par hacia el mezclador I y los bits de posición impar al mezclador Q [23][24].

**Figura 3.22** Diagrama de bloques del modulador I/Q configurado para generar una señal QPSK.

Además de la modulación QPSK, otros esquemas de modulación, como la modulación de amplitud en cuadratura (QAM), pueden igualmente configurarse con un modulador de cuadratura (I/Q). Esta técnica de modulación, además de modificar la fase, modifica la amplitud de la señal portadora y permite transmitir múltiples bits de información por símbolo [25]. Logrando así que estos esquemas sean especialmente

empleados para aplicaciones que requieran altas tasas de velocidad de transmisión.

# 3.2 Etapa de conversión ascendente de RF

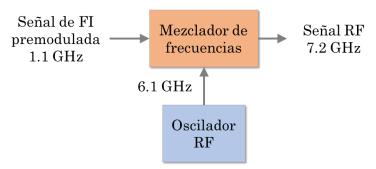

El traslado, o conversión ascendente (o de subida) de la señal de FI de 1.1 GHz a una señal de RF de 7.2 GHz se realiza mediante un mezclador de frecuencias y un oscilador de 6.1 GHz. El proceso de conversión de subida se ilustra por el diagrama a bloques en la Figura 3.23.

Figura 3.23 Esquema de la etapa de conversión de RF

# 3.2.1 Oscilador de RF

El oscilador de RF de 6.1 GHz basa su funcionamiento en la misma estructura de lazo de amarre de fase (PLL) presentada en la sección 3.11 de esta tesis.

El oscilador basado en PLL permite obtener una señal estable y precisa para el proceso de conversión ascendente.

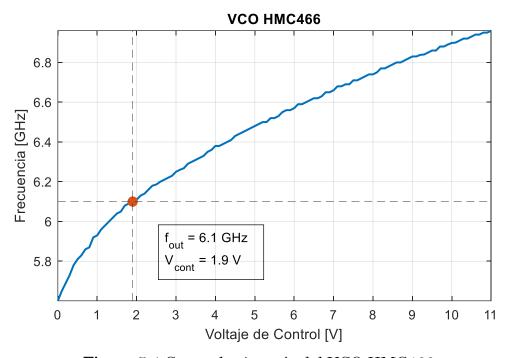

El oscilador para el convertidor ascendente utiliza un VCO y un PLL fraccional en frecuencias alrededor de los 6.1 GHz.

# 3.2.2 Mezclador de frecuencias

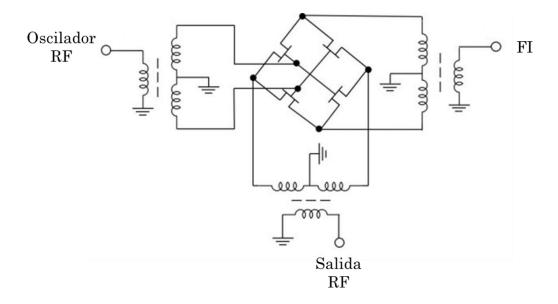

Como se mencionó en la sección 2.1.2, los circuitos mezcladores se emplean para multiplicar dos señales de frecuencias distintas, lo que permite generar la suma o la diferencia de éstas. La suma genera un espectro alrededor de la frecuencia más alta, proceso conocido como conversión de subida. La Figura 3.24 ilustra la conversión de subida.

**Figura 3.24** Espectro de la suma de la frecuencia del oscilador de RF con la señal de FI.

A diferencia de otros tipos de mezcladores (simples, balanceados) los mezcladores doblemente balanceados suprimen las señales de FI y del oscilador de RF, obteniendo a la salida únicamente la suma de sus frecuencias [26].

Un circuito mezclador que opera hasta 10 GHz se muestra en la Figura 3.25. En este mezclador se emplean transistores de efecto de campo (FET) en configuración diferencial, lo que permite la supresión de los armónicos productos de la mezcla [27].

Figura 3.25 Modulador doblemente balanceado.

# 3.3 Conclusiones

En este capítulo se presentaron las bases teóricas de los elementos principales de la etapa de FI y conversión de subida de frecuencias como tema de trabajo de esta tesis. El tema principal es el desarrollo de un subsistema de enlace ascendente para comunicaciones inalámbricas en banda X. El desarrollo de este tema requiere del diseño y realización de osciladores basados en PLL fraccionales y del desarrollo de un modulador de señales en cuadratura (I/Q). La etapa de FI consiste de un oscilador de FI en 1.1 GHz y del modulador I/Q. La FI modulada en AM-BLU-PS, es la señal de información que se eleva en frecuencia hacia una portadora de 7.2 GHz. El oscilador local para la conversión de subida opera en 6.1 GHz, señal que, al mezclarse con la FI, genera la portadora modulada en 7.2 GHz.

En este capítulo se han descrito los elementos constituyentes de un oscilador basado en PLL y las consideraciones de diseño de un oscilador

estable. Estas bases sustentan el diseño y desarrollo de los osciladores de FI (1.1 GHz) y oscilador local para la conversión de subida (6.1 GHz)

Por otra parte, se presentó el esquema de modulación en cuadratura, el cual aborda las deficiencias de la modulación clásica AM y desempeña un papel fundamental en diversos esquemas de comunicación, especialmente los que emplean la modulación digital. Además. estos esquemas en cuadratura sientan las bases para integrar esquemas más robustos de modulación como la QAM o la QPSK.

En la parte final del capítulo se describe el esquema de configuración de la conversión de subida de la FI hacia una portadora de 7.2 GHz. Los diseños y realizaciones del oscilador de FI, del modulador en cuadratura y del oscilador de 6.1 GHz se presentan en los siguientes capítulos. Las etapas de FI y oscilador local de 6.1 GHz permitirán la integración del subsistema convertidor de subida para generar una portadora de 7.2 GHz, modulada en AM-BLU-PS mediante el traslado de la FI modulada con el mismo formato.

# 3.4 Referencias

- [1] Lee, J., Seo, H., & Song, H. (1999). An integrated CDMA intermediate-frequency transceiver for wireless local loop. *IEEE Transactions on Consumer Electronics*, 45(2), 269-274, https://doi.org/10.1109/30.793408

- [2] Hall, B., & Taylor, W. (2017). X- and Ku-Band Small Form Factor Radio Design. Analog Devices. https://www.analog.com/media/en/technical-documentation/techarticles/X-and-Ku-Band-Small-Form-Factor-Radio-Design.pdf

- [3] Best, R. E. (2007). Phase Locked Loops: Design, Simulation, and Applications (6ta ed.). McGraw Hill Professional.

- [4] Egan, W. F. (2007). Phase-Lock Basics (2da ed.). Wiley-IEEE Press.

- [5] Steinem, C., & Janshoff, A. (2005). SENSORS / Piezoelectric Resonators. En Encyclopedia of Analytical Science (2da ed) (pp. 269–276). Elsevier Ltd. https://doi.org/10.1016/b0-12-369397-7/00556-2.

- [6] Floyd, T. L. (2005). Electronic Devices. Prentice Hall.

- [7] Razavi, B. (2012). RF Microelectronics (2da ed.). Prentice Hall.

- [8] Razavi, B. (2016). Design of Analog CMOS Integrated Circuits.McGraw-Hill Education.

- [9] Super PLL Application Guide (TC-AN20731-4/2002). (2002). Fujitsu Microelectronics America, Inc. http://mirror.unpad.ac.id/orari/library/library-sw-hw/community-broadcasting/fm-pll-transmitter/PLLapp.pdf

- [10] Kesse, W. O. (1996). An Analysis and Performance Evaluation of a Passive Filter Design Technique for Charge Pump Phase-Locked Loops (Application Note 1001). National Semiconductor. http://sss-mag.com/pdf/pllfil.pdf

- [11] Banerjee, D. (2017). *PLL Performance, Simulation, and Design* (5ta ed.). Dog Ear Publishing.

- [12] Skyworks Solutions. (2005). Basics of Dual Fractional-N Synthesizers/PLLs [Whitepaper]. https://www.skyworksinc.com/-/media/SkyWorks/Documents/Products/201-300/101463B.pdf

- [13] Vingron, S. P. (2012). Logic Circuit Design: Selected Methods.

Springer Science & Business Media.

- [14] Quemada, C., Bistue, G., & Adin, I. (2009). *Design Methodology for RF CMOS Phase locked loops*. Artech House Publishers.

- [15] Alvarado, U., Bistué, G., & Adín, I. (2011). Low power RF circuit design in standard CMOS technology. Springer Science & Business Media.

- [16] Suchitra, M., Geethashree, A., & Panchami, S. V. (2021). Review on Fractional-N Frequency Synthesizers. *International Journal of Innovative Science and Research Technology*, 6(2), 47-51, www.ijisrt.com.

- [17] Riley, T., Copeland, M., & Kwaśniewski, T. (1993). Delta-sigma modulation in fractional-N frequency synthesis. *IEEE Journal of Solid-state Circuits*, 28(5), 553–559. https://doi.org/10.1109/4.229400

- [18] Perrott, M. H., Trott, M., & Sodini, C. (2002). A modeling approach for Σ-Δ fractional-N frequency synthesizers allowing straightforward noise analysis. *IEEE Journal of Solid-state Circuits*, 37(8), 1028–1038. https://doi.org/10.1109/jssc.2002.800925

- [19] Elkholy, A., Saxena, S., Shu, G., Elshazly, A., & Hanumolu, P. K. (2018). Low-Jitter Multi-Output All-Digital Clock generator using DTC-Based open loop fractional dividers. *IEEE Journal of Solid-state Circuits*, 53(6), 1806–1817. https://doi.org/10.1109/jssc.2018.2817602

- [20] Sedha, R. (2014). Analog Communication. S. Chand Publishing.

- [21] Khan, A. (2005). Introduction to Electrical, Electronics and Communication Engineering. Firewall Media.

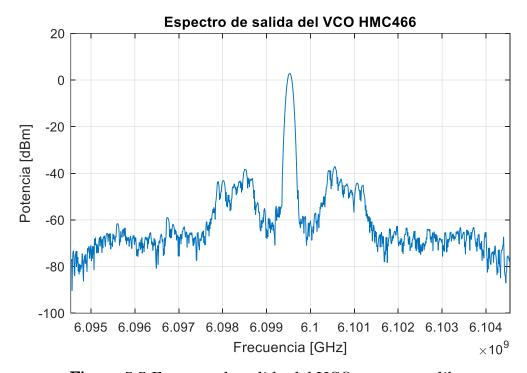

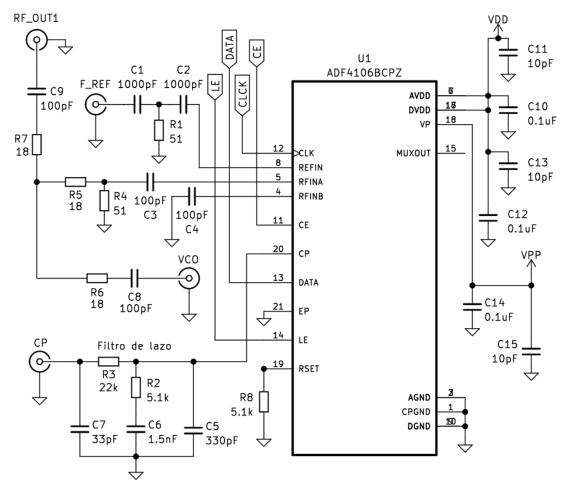

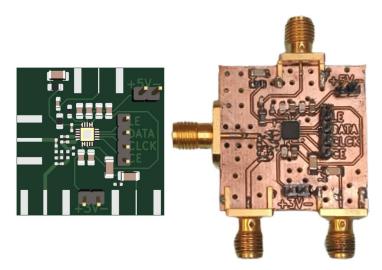

- [22] Alencar, M. S., & Da Rocha, V. C. (2005). *Communication Systems*. Springer Science & Business Media.