Medición de capacitancia dependiente de voltaje empleando un circuito para desacoplar estímulos de corriente continua y de baja frecuencia en un analizador de redes

por

Juan Pablo Sánchez Muñoz

Tesis sometida como requisito parcial para obtener el grado de

Maestro en Ciencias en la especialidad de Electrónica

en el

Instituto Nacional de Astrofísica, Óptica y Electrónica.

Agosto 2023 Tonantzintla, Puebla

Supervisada por:

**Dr. Reydezel Torres Torres**

**©INAOE 2023**

Derechos Reservados El autor otorga al INAOE el permiso de reproducir y distribuir copias de esta tesis en su totalidad o en partes mencionando la fuente.

## **RESUMEN**

En este trabajo es explicado el origen de los errores en la medición de la capacitancia obtenida de la caracterización de capacitores cerámicos multicapa a diferentes voltajes de polarización. Esto debido a que la capacitancia de algunos de estos dispositivos tiende a disminuir como consecuencia de una reducción en la densidad de dipolos eléctricos en el material dieléctrico cuando se aplica un voltaje. El principal problema en la caracterización está relacionado con la degradación de la calibración del equipo necesario para las mediciones eléctricas correspondientes. Dicha degradación es causada porque las características del circuito que desacopla los estímulos de voltajes de corriente directa y alterna presentan dependencia con el voltaje. Este circuito se conoce como T de polarización. Debido a esto, un nuevo circuito es propuesto y utilizado en este trabajo para evitar la modificación de los errores sistemáticos después un proceso de calibración. Esto permite la obtención del coeficiente de reflexión complejo de los capacitores cerámicos utilizando un analizador de redes vectorial, incluso cuando éste incluye una T de polarización interna que no está optimizada para caracterizaciones en baja frecuencia. La propuesta muestra funcionalidad para ser utilizada en la caracterización de capacitores del orden de microfaradios a una frecuencia mínima de 40 kHz. Además, los datos obtenidos de la capacitancia muestran correlación con los proporcionados en las hojas de datos de los fabricantes de los capacitores.

## **ABSTRACT**

In this work is explained the origin of the capacitance errors obtained during the characterization of multilayer ceramic capacitors with different bias voltages. This is due to some capacitors tend to decrease its capacitance because of a reduction of the electric dipoles within the dielectric material when a voltage is applied. The main problem with the characterization is related with the calibration degradation of the required equipment to perform the electric measurements. This degradation is caused because of the characteristics of the circuit that decouples the voltage stimuli of alternate and direct current present dependance with the voltage. This circuit is known as bias tee. Due to this, a new circuit is proposed and used in this work to avoid the modification of the systematic errors after a calibration process. This allows for obtaining of the complex reflection coefficient of the ceramic capacitors using a vector network analyzer, even when it includes an internal bias-tee that is not optimized for low frequency characterization. The proposal shows functionality to be used for characterization of order of microfarads capacitors at a 40 kHz minimum frequency. Besides, the capacitance data obtained shows correlation with the given by the datasheet of capacitors manufacturers.

## **AGRADECIMIENTOS**

Doy gracias a mi familia, a mi madre, padre y hermanos, por el apoyo, palabras y ánimo brindado en lo que va de mi vida y durante mis estudios.

A mis amigos, por las risas, los buenos momentos y por compartirme sus experiencias y conocimiento.

Al Instituto Nacional de Astrofísica Óptica y Electrónica por aceptarme en el programa de maestría y permitirme continuar mis estudios.

A mi asesor de tesis y profesores, por su tiempo, enseñanzas, paciencia y dedicación puesta en mi formación académica.

Al CONACHYT, por asignarme la beca con numero 1148284 y los apoyos financieros brindados durante mis estudios de maestría.

# **CONTENIDO**

| R | ESUMEN                                                                     | ا    |

|---|----------------------------------------------------------------------------|------|

| Α | BSTRACT                                                                    |      |

| С | APÍTULO I                                                                  | 1    |

|   | 1. Introducción                                                            | 1    |

|   | 1.1 Aplicación de los capacitores cerámicos                                | 2    |

|   | 1.2 Estructura de los capacitores MLCC                                     | 4    |

|   | 1.3 Características de alta frecuencia de un MLCC                          | 6    |

|   | 1.4 Dependencia de la capacitancia con la polarización                     | 8    |

|   | 1.5 Objetivo de este proyecto                                              | . 10 |

| С | APÍTULO II                                                                 | . 11 |

|   | 2. Métodos para la caracterización de capacitores                          | . 11 |

|   | 2.1 Medidores de impedancia                                                | . 11 |

|   | 2.2 Analizadores de redes, mediciones de 1 y 2 puertos                     | . 12 |

|   | 2.3 T de polarización, topologías y consideraciones                        | . 14 |

|   | 2.4 Interfaces populares para medición                                     | . 16 |

|   | 2.5 Resumen de capítulo                                                    | . 18 |

| С | APÍTULO III                                                                | . 19 |

|   | 3. Experimentos                                                            | . 19 |

|   | 3.1 Configuración del VNA                                                  | . 19 |

|   | 3.2 Estructuras de prueba y desincrustación                                | . 21 |

|   | 3.3 Dependencia de la T de polarización interna del VNA con $V_{\rm bias}$ | . 25 |

|   | 3.4 Diseño de la T de polarización externa                                 | . 27 |

|   | 3.5 Descripción de la T de polarización propuesta en esta tesis            | . 31 |

|    | 3.5.1 Diseño e implementación de la T externa                                 | . 31 |

|----|-------------------------------------------------------------------------------|------|

|    | 3.5.2 Verificación experimental del circuito propuesto                        | . 33 |

| C  | APÍTULO IV                                                                    | . 37 |

|    | 4. Resultados                                                                 | . 37 |

|    | 4.1 Curvas de $\Delta$ C contra $V_{\text{bias}}$ obtenidas experimentalmente | . 37 |

|    | 4.2 Ejemplo de aplicación                                                     | . 39 |

|    | 4.3 Consideraciones al reducir la reactancia                                  | . 42 |

|    | 4.4 Conclusiones de capítulo                                                  | . 45 |

| C  | APÍTULO V                                                                     | . 46 |

|    | 5. Resumen final y conclusiones                                               | . 46 |

|    | 5.1 Acerca del objeto de estudio de este trabajo                              | . 46 |

|    | 5.2 Medición de capacitores dependientes del voltaje con un VNA               | . 46 |

|    | 5.3 Propuesta de un circuito de polarización en este trabajo                  | . 47 |

|    | 5.4 Acerca de los resultados experimentales                                   | . 48 |

| G  | LOSARIO                                                                       | . 50 |

| 1Α | NEXOS                                                                         | . 51 |

|    | 1.1 Visualización y procesamiento de datos                                    | . 51 |

| LI | STA DE FIGURAS                                                                | . 54 |

| RI | FERENCIAS                                                                     | 57   |

## CAPÍTULO I

#### 1. Introducción

Actualmente, los capacitores cerámicos multicapa (MLCCs, por sus siglas en inglés) son ampliamente usados en una gran variedad de equipos electrónicos. Sus características de operación varían dependiendo de las condiciones en que son implementados; por ello, éstos han sido y siguen siendo estudiados con la finalidad de conocer su comportamiento y tomarlo en cuenta al momento de diseñar algún sistema electrónico.

En la literatura pueden encontrarse múltiples estudios que se han realizado para determinar las características de los MLCCs contra voltaje de polarización de corriente continua (CC). La motivación para realizar estos análisis es porque algunos MLCCs son presentan variaciones considerables en su capacitancia para rangos de voltaje dentro de los cuales son utilizados en la práctica. En este sentido, muchos trabajos están enfocados especialmente a la caracterización en altas frecuencias, por lo que se hacen suposiciones en el desarrollo de los métodos o procedimientos que sólo son válidas en el rango de los gigahertz. En contraparte, también existen metodologías para la obtención de propiedades de los MLCCs en bajas frecuencias (e.g., hasta algunos megahertz), los cuales presentan inconvenientes que son ampliamente discutidos en esta tesis.

Uno de los principales aspectos que se estudian en el proyecto que aquí se describe es la falta de idealidad de los circuitos de alimentación que se requieren para la medición con técnicas de radiofrecuencia (RF) de dispositivos bajo distintos voltajes de alimentación. En este respecto, el principio básico de operación de estos circuitos es el desacoplamiento de las señales de RF y los estímulos de corriente continua. Por la forma del circuito, se les conoce como Ts de polarización, y es como serán referidas a lo largo de este documento.

Para entrar en contexto, algunas Ts de polarización son optimizadas para la obtención de parámetros en altas frecuencias. Entonces, son implementadas con capacitores en serie e inductores en paralelo que presentan reactancia despreciable

en altas frecuencias, pero que pueden introducir errores críticos cuando se realiza una caracterización a bajas frecuencia. De hecho, el desconocimiento de las limitaciones de estas Ts puede llevar a una incorrecta interpretación de resultados, como la subestimación o sobre estimación del rendimiento de un dispositivo. Tomando esto en cuenta, en este proyecto se presenta la teoría que permite desarrollar un método experimental para la obtención de la capacitancia de MLCCs contra voltaje incluso a frecuencias de algunos kilohertz. Una de las ventajas de esto es que las mediciones correspondientes pueden hacerse con analizadores de redes vectoriales (VNAs, por sus siglas en inglés), que en principio tienen uso en el rango de las microondas. Sin embargo, mediante la T de polarización que aquí se propone, se demuestra que se puede extender el uso de este equipo a mediciones de baja frecuencia, lo que representa un avance en el estado del arte.

Este trabajo presenta algunas consideraciones que deben tomarse en cuenta durante una caracterización en bajas frecuencias; también se describe un método con el cual se puede concluir si pudieran existir errores durante ésta. Además, se presentan resultados de múltiples experimentos para una metodología tradicional. Finalmente, se muestran los resultados de aplicar el método propuesto.

### 1.1 Aplicación de los capacitores cerámicos

Los capacitores cerámicos, MLCCs, tienen varias aplicaciones en las diferentes partes de un circuito electrónico. Se usan en sistemas de comunicación para enlaces de alta velocidad, en redes de distribución de potencia (PDN, por sus siglas en inglés) o con la finalidad de lograr la integridad de señal durante la transmisión de datos entre circuitería de entrada/salida de un chip [1].

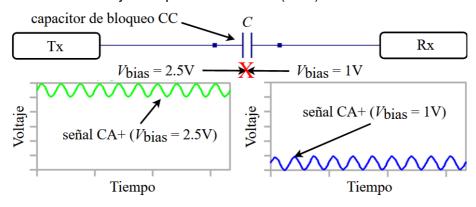

Entre las principales aplicaciones de un MLCC, se encuentra el acoplamiento capacitivo de diferentes etapas de un circuito que requieren de la transmisión de señales de CA (corriente alterna) entre ellas. Dicho acoplamiento se debe conseguir mientras se bloquean los niveles de voltaje de polarización CC, ya que circuitos en cascada pueden ser energizados con diferentes polarizaciones [2]. Entonces, de no realizarse este bloqueo pueden ocurrir daños al sobrepasarse niveles de voltaje

permitidos en algunas etapas. En esta aplicación, los MLCCs son conocidos como capacitores de bloqueo de CC y son usados en canales de comunicación de larga distancia y también para interconexiones tarjeta a tarjeta y chip a chip, donde el ancho de banda (BW, por sus siglas en inglés) está determinado por la capacitancia y los efectos parásitos del capacitor o la estructura en la cual se encuentra implementado [3]-[5]. La Fig. 1.1 muestra la representación de un capacitor de bloqueo CC conectado en serie entre un transmisor (Tx) y un receptor (Rx) que trabajan a distintos voltajes de polarización CC (Vbias).

Fig. 1.1 MLCC implementado como capacitor de bloqueo CC entre dos etapas,  $T_X$  y  $R_X$ , que operan a distintos voltajes de polarización de CC. Esto mientras se lleva a cabo la transmisión de una señal CA entre ellas.

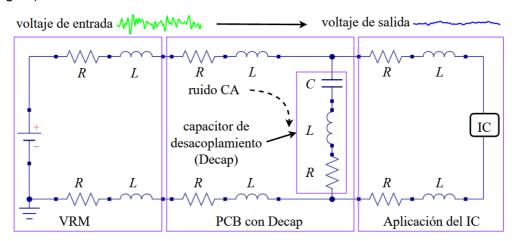

En otras aplicaciones, un MLCC también se puede usar como condensador de desacoplamiento (Decap, por sus siglas en inglés) para evitar que el ruido eléctrico de CA de la fuente de alimentación de CC llegue a los componentes conectados a ésta. El origen de este problema es que las interconexiones que llevan la alimentación a diferentes etapas de un circuito no exhiben corrientes constantes con el tiempo, ya que la demanda de energía por los dispositivos es fluctuante; por ejemplo, debido a la conmutación de transistores. Estas fluctuaciones de corriente originan caídas de voltaje en las interconexiones debido a que éstas exhiben inductancias considerables. Aquí es donde radica la importancia de diseñar circuitos que compensen la reactancia inductiva de la red de alimentación mediante ramas implementadas con MLCCs. De no llevarse a cabo esta compensación, puede ocurrir una degradación sustancial de la integridad de las señales, así como de la capacidad de accionamiento de los dispositivos. Esto es muy común en circuitos

integrados (ICs, por sus siglas en inglés), y puede perjudicar su fiabilidad y rendimiento [6], [7]. Dicho de manera simple, un MLCC sirve como reserva local de energía, reduciendo los niveles de fluctuaciones del voltaje en la fuente de alimentación CC y los rieles de potencia y proveyendo fuentes rápidas de corriente para los circuitos que se encuentran operando. Además, permiten realizar una compensación reactiva de los efectos parásitos en una PDN debidos, por ejemplo, a interconexiones en una placa de circuito impreso (PCB, por sus siglas en inglés) [8]-[11].

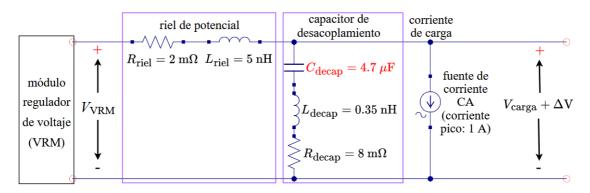

La Fig.1.2 muestra un diagrama de una PDN en la cual se utiliza un MLCC como decap para mitigar los efectos del ruido de CA y las fluctuaciones de voltaje en una fuente de CC. En este tipo de configuración, el capacitor es conectado en paralelo con la fuente de alimentación o modulo regulador de voltaje (VRM, por sus siglas en inglés).

Fig. 1.2 Circuito equivalente de una PDN, en la cual un MLCC es implementado como decap para evitar que el ruido AC afecte el desempeño de un circuito integrado.

### 1.2 Estructura de los capacitores MLCC

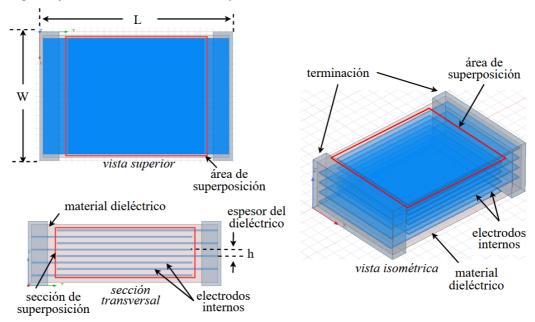

La Fig. 1.3 muestra la representación de un capacitor cerámico multicapa de dos terminales para montaje superficial. Un MLCC posee varios electrodos de material conductivo interdigitados y conectados a sus terminaciones, los cuales están separados por una capa de material dieléctrico de espesor "h". La vista superior de un MLCC en la Fig. 3 hace referencia al área efectiva "A" en la cual los electrodos

se superponen uno encima de otro, esta área y otros parámetros como el número de electrodos "n", el espesor "h" y la permitividad relativa del dieléctrico "k" determinan la capacitancia (*C*) y el voltaje nominal del capacitor [12]. "L" y "W" son la longitud y el ancho del MLCC respectivamente.

Fig. 1.3 Vistas superior, isométrica y sección transversal de la estructura de un capacitor cerámico de capas múltiples MLCC.

La capacitancia de un MLCC puede calcularse por la siguiente ecuación, donde  $\varepsilon_0$  es la permitividad del vacío:

$$C = \frac{\varepsilon_0 k A n}{h} \tag{1.1}$$

Los MLCCs pueden ser catalogados en diferentes clases dependiendo de sus características y comportamiento contra ciertos parámetros, por ejemplo, temperatura y voltaje de polarización CC [12]. En este respecto, los MLCCs Clase I, usan material paraeléctrico como dieléctrico y son conocidos como capacitores de compensación de temperatura, ya que su capacitancia es constante en su rango de temperatura de trabajo y no presentan dependencia con los voltajes de polarización CC. Una de sus desventajas es que debido a la baja permitividad de los materiales comerciales con estabilidad térmica las capacitancias correspondientes son pequeñas [13], [14].

Los MLCCs Clase II, utilizan material ferroeléctrico como dieléctrico, el cual posee una alta permitividad relativa; por ello, sus capacitancias son grandes incluso en empaquetados de volumen pequeño. En este caso, su capacitancia es variable con la temperatura y también presentan dependencia con los voltajes de polarización CC [14], [15].

#### 1.3 Características de alta frecuencia de un MLCC

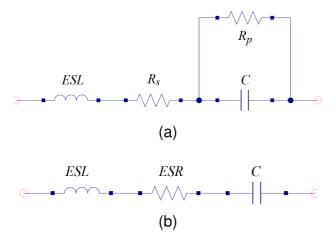

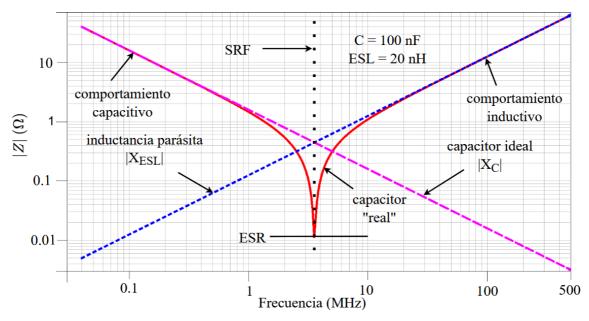

Como es de esperarse, los MLCCs distan de ser perfectos, sus características físicas como tamaño y geometría de construcción producen efectos parásitos (no deseados) que degradan su desempeño en altas frecuencias. Entonces, para representar las propiedades eléctricas de un dispositivo "real" se utilizan modelos de circuito equivalente (ECM, por sus siglas en inglés) que son válidos bajo ciertas condiciones como, temperatura, frecuencia, entre otros. La Fig.1.4 muestra dos modelos de un capacitor considerando los efectos parásitos en altas frecuencias.

Fig. 1.4 Modelos de circuito equivalente de un capacitor en altas frecuencias: a) modelo estándar, b) modelo simplificado.

Cada elemento en el modelo de circuito equivalente representa un fenómeno físico que ocurre en el dispositivo modelado. Así, en la Fig. 1.4(a), C es la capacitancia,  $R_{\rm S}$  es la pérdida por disipación de calor que puede ser expresada como factor de potencia o como factor de disipación (DF, por sus siglas en inglés),  $R_{\rm P}$  es la resistencia de aislamiento y ESL (*equivalent series inductance*, en inglés) es la inductancia de las terminales y los electrodos de material conductivo [16], [17].

En la Fig. 1.4(a),  $R_p$  representa la ruta de un flujo de corriente que pasa a través del dieléctrico del capacitor cuando se aplica un voltaje CC entre sus terminales. Esta corriente de fuga es debida a que ningún material es un aislante perfecto, en general, la resistencia de aislamiento ( $R_p$ ) es del orden de megaohms o más. La resistencia equivalente en serie (ESR, por sus siglas en inglés), en la Fig. 1.4(b), es la combinación de las resistencias  $R_s$  y  $R_p$ , y es la resistencia CA de un capacitor [16].

Fig. 1.5 Magnitud de la impedancia (|Z|) contra frecuencia a partir del modelo de un capacitor considerando los efectos parásitos.

En la Fig. 1.5, se muestra la curva de impedancia contra frecuencia del circuito equivalente de la Fig. 1.4(a), además se muestra la reactancia inductiva de ESL  $(X_{\text{ESL}} = \omega \text{ESL})$  y capacitiva de C  $(X_{\text{C}} = -1/\omega C)$ , siendo  $\omega = 2\pi f$  la frecuencia angular y f está dada en hertz. Notar que existe una frecuencia de auto resonancia (SRF, por sus siglas en inglés), en la cual la impedancia del capacitor se reduce al valor de ESR debido a que las contribuciones de las reactancias capacitiva e inductiva se cancelan entre ellas. En la práctica, SRF puede calcularse por la siguiente ecuación:

$$SRF = \frac{1}{2 * \pi * \sqrt{ESL * C}} \tag{1.2}$$

Para frecuencias mayores a SRF, el capacitor presenta un comportamiento inductivo debido a ESL; por ello, es deseable que los efectos parásitos sean lo más pequeños posible. Un punto importante por considerar es que los efectos parásitos no son exclusivos de un capacitor, otros elementos como inductores y resistores presentan estos efectos que degradan desempeño en altas frecuencias [17].

#### 1.4 Dependencia de la capacitancia con la polarización

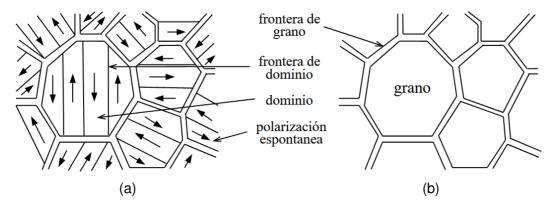

Los MLCC Clase II utilizan titanato de bario (BaTiO<sub>3</sub>) como principal material dieléctrico constitutivo, éste posee una baja conductividad e idealmente exhibe una estructura de dipolo eléctrico. Esta última característica, sin embargo, puede degradarse bajo condiciones de operación comunes. Esto se debe a que el BaTiO<sub>3</sub> es un material capaz de presentar diferentes configuraciones cristalinas (cúbica, tetragonal, ortorrómbica o romboédrica). La temperatura a la cual ocurre la transición de fase del BaTiO<sub>3</sub> de su forma tetragonal a cubica (aprox. 130°C), se conoce como temperatura de Curie (T<sub>c</sub>) [18], [19]. Para temperaturas mayores a T<sub>c</sub> el BaTiO<sub>3</sub> presenta una estructura cúbica y se comporta como material paraeléctrico, mientras que, para temperaturas menores a T<sub>c</sub>, éste tiene un comportamiento ferroeléctrico [19], [20].

Fig. 1.6 Formación de granos y dominios en Ba $TiO_3$ : a) considerando una estructura cristalina tetragonal y temperatura menor a  $T_C$ , b) estructura cúbica para temperaturas mayores a  $T_C$ . [19].

Continuado con la descripción del BaTiO<sub>3</sub>, está compuesto de granos o pequeños cristales con diferente orientación cristalina cada uno y separados por una superficie o frontera de grano. Esta separación, sin embargo, no es tal que impida la

interacción entre átomos de diferentes cristales, lo que origina una reacción no lineal a estímulos de campo eléctrico. Por otra parte, a temperatura ambiente (Ta = 25 °C) el BaTiO<sub>3</sub> exhibe una estructura cristalina tetragonal y presenta polarización espontanea (polarización en ausencia de un campo eléctrico externo) debido a la presencia de dipolos eléctricos permanentes. Algunos dipolos cercanos entre ellos tienden a alinearse hacia una dirección preferente generando una región conocida como dominio, la orientación de cada dominio es diferente y están separados por una frontera de dominio [19], [20].

La Fig. 1.6 muestra una representación de los dominios y granos formados en el BaTiO<sub>3</sub> considerando las estructuras cristalinas tetragonal y cúbica. Para una estructura cúbica sólo se forman granos ya que el material no presenta dipolos eléctricos que puedan agruparse para formar dominios.

Como se mencionó anteriormente, los MLCC Clase II utilizan BaTiO<sub>3</sub> como principal material dieléctrico. A pesar de que este puede lograr el almacenamiento de una alta densidad de energía, su permitividad es propensa a cambios debido al realineamiento de dipolos eléctricos en el mismo, produciendo variaciones en el desempeño de los capacitores [13], [19]-[21].

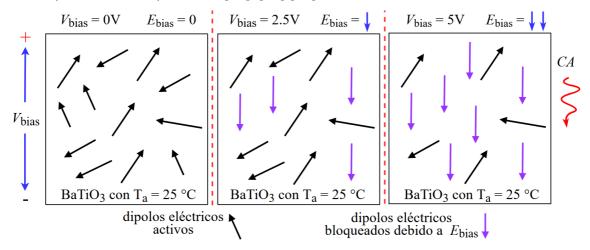

Fig. 1.7 Disminución en la densidad de dipolos activos en el BaTiO<sub>3</sub> que un campo eléctrico ECA puede polarizar debido a un incremento en intensidad de V<sub>bias</sub> y E<sub>bias</sub> [21].

La Fig. 1.7 muestra un ejemplo de la reorientación de los dipolos eléctricos en el BaTiO<sub>3</sub> bajo diferentes voltajes CC (V<sub>bias</sub>). Para este ejemplo, se supone una

temperatura ambiente  $T_a = 25$ °C. En el primer caso,  $V_{bias} = 0$  V, por lo que, el campo eléctrico producido por éste también es cero ( $E_{bias} = 0$ ) y el material sólo presenta polarización espontanea. Así, si un campo eléctrico originado por un voltaje de CA ( $E_{CA}$ ) es aplicado, éste puede polarizar fácilmente al material; es decir, los dipolos eléctricos dentro de éste se alinean con  $E_{CA}$ . Para el segundo y tercer caso,  $V_{bias} \neq 0$  V, por lo que algunos dipolos son polarizados y "bloqueados" por  $E_{bias}$ . Entonces, al aplicar un campo eléctrico adicional,  $E_{CA}$ , estos son difícilmente alterados. En este sentido, la densidad de dipolos que  $E_{CA}$  puede polarizar ha disminuido y con esto la permitividad y la capacitancia efectiva en un MLCC.

Es importante mencionar que no todos los MLCC Clase II tienen el mismo nivel de pérdida de capacitancia contra voltaje CC. Otro factor para considerar, por ejemplo, es el tamaño de grano en su dieléctrico, BaTiO<sub>3</sub>, que puede modificar sus características eléctricas [22]-[24].

#### 1.5 Objetivo de este proyecto

El objetivo de este proyecto es desarrollar un método experimental para la caracterización de capacitores cerámicos, MLCCs. Entonces, considerando que estos dispositivos presentan capacitancias del orden de microfaradios, se diseñará un circuito para estimularlos con voltajes de polarización CC en el rango comprendido entre 0 V y 25 V. Esta polarización debe aplicarse simultáneamente con la señal de CA de baja potencia que permite la medición del coeficiente de reflexión complejo (Γ) mediante el uso de un VNA. Debido a la baja reactancia que presentan los MLCCs, las mediciones deben realizarse a frecuencias en el límite inferior de operación del VNA que en este caso es de 40 kHz. Así, la metodología propuesta permitirá obtener curva del cambio en la capacitancia de un MLCC contra voltaje de polarización CC (*C-V*<sub>bias</sub>) de manera precisa.

## CAPÍTULO II

#### 2. Métodos para la caracterización de capacitores

En la literatura pueden encontrarse múltiples trabajos relacionados con la caracterización experimental de capacitores MLCC, algunos proponen métodos basados en el uso de un VNA como instrumento de medición, otros emplean medidores de impedancia LCR. En este capítulo se describen generalidades de estos métodos, algunas consideraciones referentes al diseño de una T de polarización y se presentan algunas interfaces de medición populares en un VNA para caracterizaciones de RF.

#### 2.1 Medidores de impedancia

Los medidores de impedancia LCR basan su funcionamiento en la medición de corriente y voltaje CA. Así, de las magnitudes correspondientes y la diferencia de fase entre éstos puede obtenerse la impedancia [25]. Es bien sabido que este equipo permite realizar caracterizaciones con diferentes voltajes de polarización CC; para esto, es necesario realizar una calibración previa y bajo las condiciones en que la medición se llevará a cabo, de manera que la medición corresponda al dispositivo bajo prueba y no incluya componentes del arreglo experimental [26], [27]. Con este propósito, también son requeridas estructuras de prueba (*test fixture*, en inglés) en la cual se coloca el dispositivo a caracterizar [26].

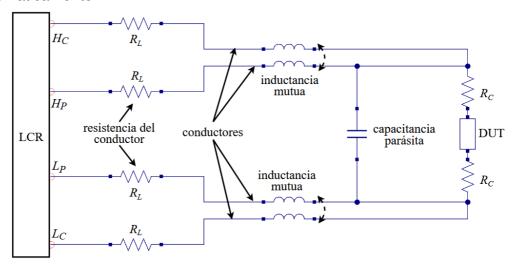

Muchos LCR utilizan el método de puente de balance automático como circuito de medición, el cual tiene cuatro terminales, Hc, HP, LP y LC (high current, high potential, low potential y low current, respectivamente y por sus siglas en inglés). Todas éstas son conectadas al objetivo de medición. Específicamente, mediante HC se aplica una señal de cierta amplitud y frecuencia, HP detecta el potencial alto, LP detecta el potencial bajo y LC detecta la corriente que fluye hacia el dispositivo bajo prueba (DUT, por sus siglas en inglés) [25].

Por otra parte, un LCR puede realizar una medición aplicando diferentes métodos o configuraciones (dos, tres, cuatro y cinco terminales); estas opciones deben ser

seleccionadas dependiendo de la impedancia del DUT y de la exactitud deseada para la medición, ya que cada caso presenta ventajas y desventajas [25], [26].

La Fig. 2.1 muestra el diagrama esquemático de un medidor LCR con una configuración de cuatro terminales. En esta configuración se identifican efectos parásitos debidos a las interconexiones desde el LCR hasta el DUT, los cuales pueden causar inexactitud en la medición y que deben ser removidos sistemáticamente.

Fig. 2.1 Esquema de un medidor LCR con una configuración de cuatro terminales mostrando efectos parásitos como resistencias de contacto (R<sub>C</sub>) y del conductor o inductancias y capacitancias entre estos [26].

### 2.2 Analizadores de redes, mediciones de 1 y 2 puertos

Un analizador de redes vectorial basa su funcionamiento en técnicas de reflectometría y realiza la medición de parámetros de dispersión o parámetros S [28]. Aunque un medidor LCR y un VNA tienen distintos principios de operación, ambos pueden utilizarse obtener la impedancia de un DUT ya que su desempeño es similar, al menos para una frecuencia de hasta 100 MHz [29].

Para caracterizaciones con diferentes voltajes de CC se requiere de una T de polarización que permita la aplicación de un voltaje CC y de una señal CA a un DUT de manera simultánea [30]. Generalmente, también se requiere de una estructura de prueba en la cual se coloca el DUT [31], así como un procesamiento de los datos

medidos empleando técnicas de calibración para compensar errores sistemáticos (debidos a no idealidades del VNA) en la medición. Esto último permite la remoción de los efectos correspondientes a los cables y conectores entre el VNA y la estructura de prueba [28].

Existen diferentes procedimientos de calibración para equipos de uno, dos o más puertos. Por ejemplo, una calibración Short-Open-Load (SOL, por sus siglas en inglés) de un puerto requiere de la medición de estándares de calibración como circuito abierto, corto circuito, y carga. La ubicación donde se conectan los estándares durante una calibración se conoce como plano de referencia [28].

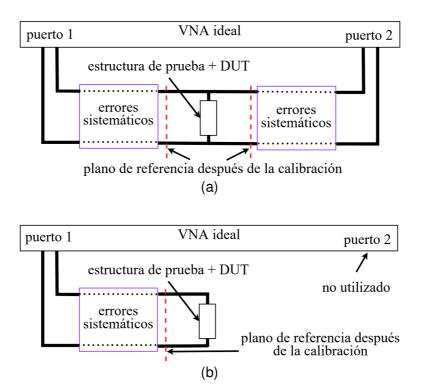

Un VNA puede realizar mediciones de 1 o 2 puertos para caracterizaciones de dispositivos de dos terminales [32]. Para una medición de dos puertos, el DUT se conecta con una configuración serie o paralelo, siendo esta ultima la preferida para la detección de impedancias del orden de miliohms [33], [34], [35]. La Fig. 2.2 muestra las configuraciones de un VNA para mediciones de 1 y 2 puertos.

Fig. 2.2. Esquema de un VNA con una configuración para mediciones: a) un puerto, y b) dos puertos con el DUT conectado en paralelo.

Una configuración para mediciones de un puerto permite que la estructura de prueba sea simple y pueda conectarse fácilmente al VNA; además, se reducen los errores introducidos por cables y conectores, ya que no se consideran los debidos al segundo puerto de medición.

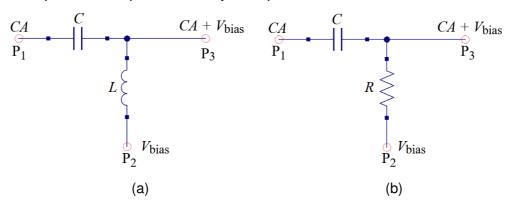

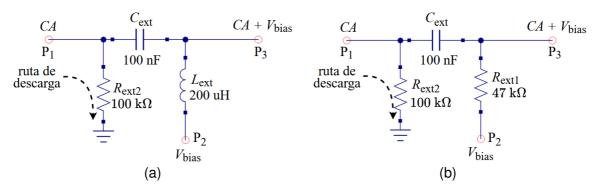

#### 2.3 T de polarización, topologías y consideraciones

Las T de polarización son circuitos eléctricos de tres puertos que permiten la aplicación de un voltaje CC y de una señal CA o de RF a un dispositivo de manera simultánea. Su diseño depende principalmente del rango de frecuencia en que planea utilizarse y de la corriente y voltaje que se pretenda manejar [36]. La Fig. 2.3 muestra dos topologías básicas de una T de polarización. La nomenclatura P<sub>1</sub>, P<sub>2</sub>, y P<sub>3</sub> corresponde a los puertos 1, 2, y 3 respectivamente.

Fig. 2.3 Topologías básicas de una T de polarización basada en circuitos: a) LC, y b) RC [36].

En la Fig. 2.3, el capacitor, *C*, permite el acoplamiento de una señal *CA* entre P<sub>1</sub> y P<sub>3</sub>, y al mismo tiempo impide que el voltaje de *CC* conectado a P<sub>2</sub> llegue a P<sub>1</sub>. Por otro lado, el resistor, *R*, y el inductor, *L*, proveen una ruta de corriente *CC* desde P<sub>2</sub> hasta P<sub>3</sub>, e impiden que la señal *CA* en P<sub>1</sub> llegue a P<sub>2</sub>. El uso de un resistor o inductor depende de la corriente *CC* que se maneja. Para corrientes grandes, mayores a 10 mA, es preferible utilizar un inductor [36].

Las principales especificaciones de RF de una T de polarización con una topología como en la Fig. 2.3 son:

- **S**<sub>11</sub> o pérdidas por retorno (*return losses*, en inglés), son las pérdidas debidas a reflexiones en P<sub>1</sub>.

- **S**<sub>31</sub> o pérdidas por inserción (*insertion losses*, en inglés), indican las pérdidas en la transmisión de señales entre P<sub>3</sub> y P<sub>1</sub>.

- **S**<sub>21</sub> o aislamiento (*isolation*, en inglés), es el aislamiento entre P<sub>2</sub> y P<sub>1</sub>; éste debe mantenerse muy bajo para evitar transmisión no deseada de señales entre los puertos 2 y 1 [37], [30].

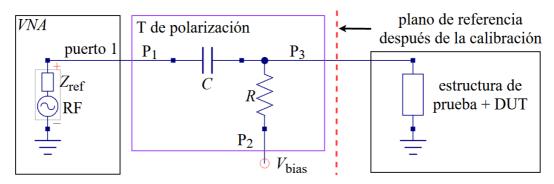

La Fig. 2.4 muestra una posible configuracion para caracterizaciones utilizado un VNA y una T de polarización. P<sub>1</sub> se conecta con el VNA o instrumento de medición, P<sub>2</sub> con a la fuente de voltaje CC y P<sub>3</sub> con la estructura de prueba y el DUT.

Fig. 2.4 Posible configuración para mediciones de un puerto utilizando un VNA y una T de polarización.

Los valores de R, C y L determinan la magnitud de  $S_{11}$ ,  $S_{21}$ ,  $S_{31}$  y de la frecuencia a la cual se puede utilizar una T de polarización sin degradar el desempeño del sistema en el que se implementa. La impedancia de un capacitor debe ser menor a 50  $\Omega$  para evitar reflexiones en  $P_1$  y lograr la transmisión de la señal CA hacia  $P_3$  [36]. Por otro lado, las impedancias de R y L deben ser lo más grandes posible para conseguir un gran aislamiento entre  $P_1$  y  $P_2$ . En general se requieren valores grandes de L y C para evitar introducir errores de gran magnitud en la ruta de señal CA, especialmente para frecuencias de operación bajas [38].

Algunas T de polarización pueden tener características de RF que son dependientes del voltaje CC. Esto debido a que son construidas con capacitores cerámicos Clase II. En este aspecto, los errores en la ruta de señal CA introducidos por la T cambian

con el voltaje de CC. Esto puede degradar la calibración del equipo de medición, lo cual representa un impacto negativo, especialmente en bajas frecuencias donde la impedancia de un capacitor es mayor [36].

Los errores debidos a una T de polarización pueden ser compensados por una calibración del equipo de medición, incluso si éstos son grandes. Sin embargo, es preferible que estos errores sean pequeños para evitar una disminución del rango dinámico (Dynamic Range, en inglés) del equipo. Los errores que ocurren después del proceso de calibración no son compensados [39]. Por ello, un sistema de medición con una T de polarización dependiente del voltaje de CC puede requerir de una calibración para y a cada voltaje de CC considerado, aunque esto es impráctico para calibraciones que utilizan estándares como corto circuito [36].

Algunos VNAs implementan un capacitor de bloqueo CC es sus puertos de medición. Conectar una T de polarización a éstos puede formar un divisor capacitivo, por lo que, al aplicar un voltaje de CC a través de la T, una fracción de éste puede llegar al puerto del VNA lo cual es un problema. Para evitarlo, algunas T de polarización implementan resistencias conectadas entre el puerto de señal CA (P<sub>1</sub>) y la terminal negativa de la fuente CC. Éstas sirven como elementos de protección y son especialmente útiles en aplicaciones que demandan una gran magnitud de corriente [39].

Es necesario considerar que debido a que ningún componente es ideal, sus efectos parásitos deberían ser tomados en cuenta durante el diseño de una T de polarización. Especialmente si se planea utilizar en un amplio rango de frecuencias [40].

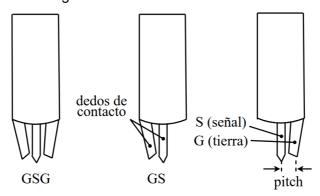

## 2.4 Interfaces populares para medición

Durante una caracterización de RF con un VNA, el DUT y el equipo de medición deben conectarse de manera que se permita la transmisión de señales entre éstos con una baja pérdida. Para este propósito, pueden utilizarse diferentes interfaces de medición, entre ellas existe la interfaz coaxial y la interfaz con puntas de prueba [41].

Al usar una interfaz coaxial, generalmente el DUT se monta en una estructura de prueba que permite conectarlo fácilmente al equipo de medición y provee una buena estabilidad mecánica. Sin embargo, el impacto de los efectos parásitos debidos a las interconexiones entre la interfaz coaxial y el DUT deben considerarse, especialmente si éste no está destinado a implementarse con dicha configuración de interconexiones. En este sentido, es necesario un proceso de desincrustación (de-embedding, en inglés) que remueve la contribución de los efectos parásitos de la medición y permite obtener solo los parámetros del DUT [41].

Por otra parte, una interfaz con puntas de prueba permite la caracterización de dispositivos "en oblea" (on-wafer, en inglés) sin la necesidad de montarlos en estructuras de prueba o empaquetarlos, lo cual reduce el tiempo de diseño, fabricación y prueba de estos, siendo esta, una interfaz adecuada para pruebas de prototipos. Una punta de prueba puede tener múltiples dedos de contacto (contact fingers, en inglés) los cuales están separados por un paso (pitch, en inglés) o distancia que se mide de centro a centro. Además, los dedos de contacto también cuentan con diferentes arreglos de configuraciones [42], [43]. Una representación de esto se muestra en la Fig. 2.5.

Fig. 2.5 Interfaz para mediciones con puntas de prueba y configuraciones GSG, GS, y SG en los dedos de contacto [43].

En una configuración tierra-señal-tierra (GSG, por sus siglas en inglés), el doble contacto hacia tierra proporciona un mejor blindaje electromagnético para la ruta de señal. Los dedos de contacto más cortos tienen un mejor desempeño en altas frecuencias [42]. El uso de puntas con configuraciones GSG o GS dependen de las necesidades del experimento que se lleva a cabo.

#### 2.5 Resumen de capítulo

Se han revisado las principales características de dos de los equipos más utilizados para obtener impedancias utilizando técnicas de radiofrecuencia: el LCR y el VNA. Ambos aparatos requieren de instrumentación adicional que permita la medición de dispositivos bajo diferentes voltajes de alimentación, una T de polarización. Se ha mencionado que tanto los efectos introducidos por esta T, como los errores sistemáticos asociados con las interfaces de medición deben considerarse para obtener mediciones realistas y precisas de los componentes. De hecho, también se mencionaron las dos interfaces más populares para interconectar un dispositivo a caracterizar con el equipo de medición; dependiendo del rango de frecuencias de interés, puede directamente utilizarse una interfaz coaxial o puntas de prueba si es importante minimizar los efectos parásitos. Con respecto a la T de polarización, como se verá en el siguiente capítulo, aquí se propone un circuito que permite la reducción de los efectos parásitos asociados con mediciones de baja frecuencia.

## CAPÍTULO III

#### 3. Experimentos

En este capítulo se describe el arreglo experimental basado en un sistema de medición de parámetros *S*. Debido a los problemas existentes en los equipos de medición comerciales enfocados en aplicaciones en el rango de las microondas, también se describe una de las contribuciones de este trabajo de tesis que permite la solución para el caso de mediciones de capacitores a una frecuencia mínima de 40 kilohertz.

Específicamente, a continuación, se presentan diagramas que ilustran las conexiones del arreglo experimental, así como la definición de los parámetros principales para la operación del VNA que se utilizó como instrumento de medición. Además, se muestran las estructuras de prueba implementadas para la medición del DUT y para el proceso de desincrustación. Del mismo modo y como ya se mencionó, se presenta la topología, el diseño y características principales de RF de la T de polarización usada para la caracterización de MLCCs Clase II.

### 3.1 Configuración del VNA

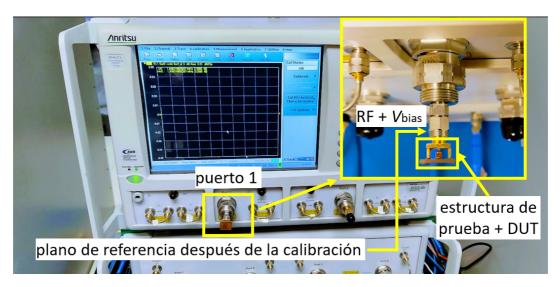

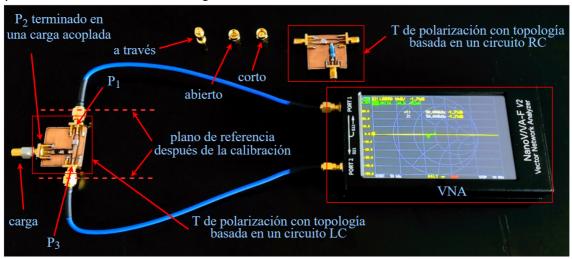

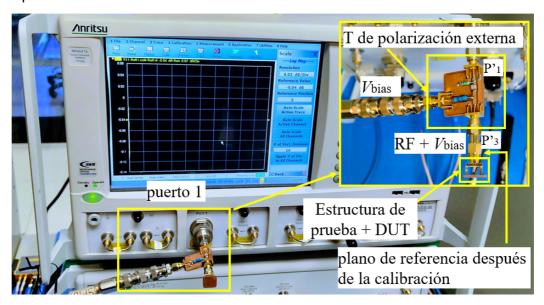

Para la caracterización de los MLCCs, se utilizó un VNA Anritsu con número de parte MS4647A-70 y con dos puertos de medición. El límite inferior de frecuencia en que el VNA puede operar es de 40 kHz. Además, éste incorpora una T de polarización interna, lo cual permite la caracterización de dispositivos mientras se les aplican voltajes de CC ( $V_{\rm bias}$ ) de hasta 40 V. El nivel de potencia de la señal RF del VNA para la caracterización se estableció en -10 dBm, mientras que el valor del ancho de banda de frecuencia intermedia (IFBW, por sus siglas en inglés) se configuró en 100 Hz. Estos dos últimos parámetros son definidos en base a la obtención de una relación señal a ruido que permita la medición de las impedancias asociadas con los dispositivos sin cambios significativos entre mediciones. La Fig. 3.1 muestra una fotografía del VNA durante la medición de un DUT (MLCC) y su estructura de prueba.

Fig. 3.1 Configuración para mediciones de un puerto utilizando un VNA con una T de polarización interna (no mostrada).

Para la caracterización se optó por utilizar una interfaz coaxial y un solo puerto del equipo para reducir las interconexiones con el DUT. El VNA se calibró con un procedimiento SOL mientras se mantenía el voltaje de polarización en  $V_{\text{bias}} = 0\text{V}$ . Con este propósito, se utilizó un calibrador Anritsu con numero de parte TOSLKF50A-40. Éste incluye estándares de calibración abierto, corto, carga y a través (thru, en inglés). Con la calibración, el plano de medición se estableció al final del puerto del VNA, después de la T de polarización interna.

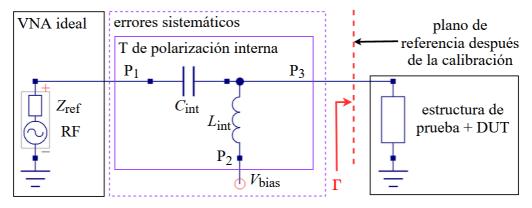

Fig. 3.2 Circuito simplificado de configuración para mediciones de un puerto utilizando un VNA y una T de polarización interna. La T contribuye con los errores sistemáticos del VNA.

La Fig. 3.2 muestra un circuito simplificado de la configuracion para mediciones de la Fig. 3.1. Los errores sistemáticos en la Fig. 3.2 corresponden a imperfecciones en el VNA, cables, conectores, discontinuidades y dispositivos en la ruta de señal

de RF que contribuyen con efectos fuera del DUT y que se repiten en todas las mediciones. En este sentido, los efectos introducidos por la T de polarización también deben ser considerados.

#### 3.2 Estructuras de prueba y desincrustación

Antes de comenzar con la descripción de los datos experimentales, es importante mencionar que, en la configuración de un puerto, un VNA no mide directamente la impedancia del DUT, sino el cociente entre la onda electromagnética que se refleja y la que se aplica a éste durante una medición. Este parámetro es un número complejo ya que proporciona información acerca de la magnitud y fase de la reflexión, es dependiente de la frecuencia y se le conoce como coeficiente de reflexión (Γ); matemáticamente, puede expresarse como:

$$\Gamma = \frac{b}{a} \tag{3.1}$$

donde b representa a la onda reflejada y a la onda incidente. Debe remarcarse también que  $\Gamma$  es dependiente de la impedancia de referencia ( $Z_{ref}$ ) definida por el equipo de medición y que es conocida por el usuario; entonces, otra manera de escribir (3.1) es:

$$\Gamma = \frac{Z_{DUT} - Z_{ref}}{Z_{DUT} + Z_{ref}}$$

(3.2)

donde  $Z_{DUT}$  es la impedancia del DUT que se está midiendo y  $Z_{ref}$  es comúnmente definida con una magnitud real y constante de 50  $\Omega$ , como en el caso de los experimentos que aquí se describen. Así, para esta  $Z_{ref}$ , si  $Z_{DUT}$  fuera una carga de 50  $\Omega$ , no existiría reflexión y resulta en  $\Gamma=0$ .

Convenientemente, (3.2) puede resolverse para obtener  $Z_{DUT}$  a partir de  $\Gamma$  utilizando:

$$Z_{DUT} = Z_{ref} \frac{1+\Gamma}{1-\Gamma}$$

(3.3)

Entonces, conociendo la impedancia de referencia del equipo y las mediciones, es posible determinar experimentalmente Z<sub>DUT</sub>.

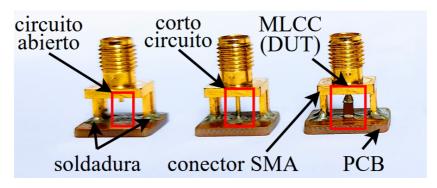

En la Fig. 3.2, el coeficiente de reflexión, Γ, obtenido de una medición con el VNA, no incluye información de los errores sistemáticos, ya que éstos fueron compensados durante la calibración. Por esta razón, Γ sólo proporciona información del DUT y la estructura de prueba. Con el fin de obtener sólo los parámetros correspondientes al DUT, se utilizó un proceso adicional que se conoce como desincrustación SO (*Short-Open*, por sus siglas en inglés), lo que requiere estructuras prueba terminadas en circuito abierto y corto circuito, pero basadas directamente en el prototipo [44]. Estas estructuras fueron implementadas con un conector coaxial subminiatura tipo A, (SMA, por sus siglas en inglés) y una pequeña PCB como se muestra en la Fig. 3.3.

Fig. 3.3 Estructuras de prueba implementadas con un conector SMA, terminadas en circuito abierto, corto circuito y con un dispositivo bajo prueba.

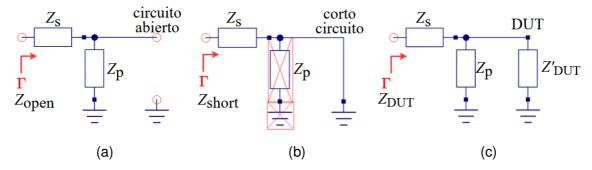

Las estructuras de prueba pueden ser representadas por circuitos equivalentes como se muestra en la Fig. 3.4. A través de mediciones, el VNA proporciona información de cada una de éstas en términos de  $\Gamma$  y utilizando la expresión (3.3),  $\Gamma$  puede ser representado en términos de impedancia. En los circuitos equivalentes

Fig. 3.4 Circuitos equivalentes de las estructuras de prueba terminadas en: a) circuito abierto, b) corto circuito y c) un dispositivo bajo prueba.

de la Fig. 3.4, Zs representa una inductancia debido al lazo de corriente que sigue la señal CA, Z<sub>P</sub> representa una capacitancia entre el conductor central del conector coaxial y sus terminales de tierra y es cortocircuitada para una medición de un corto circuito (Fig.3.4(b)). Z'<sub>DUT</sub>, es la impedancia del DUT solamente.

Si se define  $Z_{open}$  como la impedancia de la estructura de prueba terminada en circuito abierto,  $Z_{short}$  igual a la impedancia de la estructura terminada en corto circuito y  $Z_{DUT}$  como la impedancia de la estructura terminada en un DUT, podemos obtener la impedancia del DUT mediante la siguiente expresión:

$$Z'_{DUT} = \frac{1}{\frac{1}{Z_{DUT} - Z_{short}} - \frac{1}{Z_{open} - Z_{short}}}$$

(3.4)

la cual considera la conexión en serie y paralelo de los efectos parásitos. Finalmente, debido a que los efectos parásitos inherentes a un capacitor empaquetado comercialmente son despreciables en el rango de frecuencia considerado en este trabajo (40 kHz a 750 kHz), la capacitancia del DUT se calcula de:

$$C \approx \frac{1}{\omega Im\{Z'_{DUT}\}}$$

(3.5)

Una vez definidas las condiciones de medición y características de las estructuras de prueba, se procede a describir los dispositivos utilizados en los experimentos. La Tabla 3.1 muestra las principales características y nombres designados para los MLCCs aquí considerados. Nótese que se menciona el parámetro  $\Delta C$ , que indica qué tanto cambia la capacitancia para cierto voltaje de polarización,  $V_{\text{bias}}$ , con respecto a la capacitancia obtenida para  $V_{\text{bias}} = 0 \text{ V}$ .

Tabla 3.1. Principales características de los MLCCs medidos.

| Nombre                 | Proveedor    | Capacitancia                   | $\Delta C$              | Clase |

|------------------------|--------------|--------------------------------|-------------------------|-------|

| del                    |              | nominal con                    | con $V_{\text{bias}} =$ |       |

| dispositivo            |              | $V_{\text{bias}} = 0V (\mu F)$ | 25V (%)                 |       |

| C <sub>0.1µF</sub>     | TDK [45]     | 0.1                            | 0                       | I     |

| $C_{ m 1.0 \mu F}$     | Kemet [46]   | 1.0                            | -26                     | II    |

| $C_{ m 1.5 \mu F}$     | Murata [47]  | 1.5                            | <del>-</del> 39         | II    |

| $C_{2.2\mu 	extsf{F}}$ | Samsung [48] | 2.2                            | <del>-</del> 73         | II    |

| $C_{4.7\mu 	extsf{F}}$ | Samsung [49] | 4.7                            | -83                     | II    |

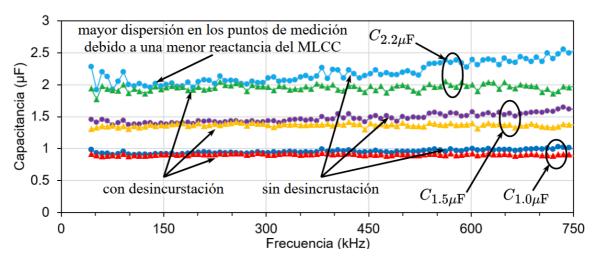

La Fig. 3.5 muestra el resultado de mediciones con y sin proceso de desincrustación para tres de los MLCCs. Es notable que la desincrustación tiene un mayor impacto en frecuencias más altas y para MLCCs de gran capacitancia. Ya que, en estas condiciones, los MLCCs presentan impedancias pequeñas, que son comparables con las introducidas por algunos efectos parásitos y por lo cual éstos tienen un mayor impacto. Por ello, es preferible obtener la capacitancia de mediciones en baja frecuencia para evitar las contribuciones de estos efectos. Además, la exactitud de la medición de una impedancia pequeña depende de la razón señal a ruido del VNA (SNR, por sus siglas en inglés). Así, ya que la capacitancia se calcula de la expresión (3.5), un pequeño error en la medición de Z'DUT debido a impedancias pequeñas produce una gran variación en el resultado de la capacitancia calculada.

Fig. 3.5 Curvas de capacitancia con y sin proceso de desincrustación para diferentes dispositivos medidos con  $V_{bias} = 0V$ .

Debe resaltarse que las impedancias  $Z_{open}$  y  $Z_{short}$  son obtenidas de la medición de un circuito abierto y un corto circuito, respectivamente. Debido a esto, la diferencia entre éstas es muy grande. Por lo anterior, la expresión (3.4) para calcular la impedancia del DUT, puede reducirse a:

$$Z'_{DUT} = Z_{DUT} - Z_{short}$$

(3.6)

y obtener el mismo resultado. En otras palabras, la contribución de la estructura terminada en circuito abierto puede despreciarse en el proceso de desincrustación, al menos para frecuencias de hasta 750 KHz.

#### 3.3 Dependencia de la T de polarización interna del VNA con $V_{\rm bias}$

Para las primeras caracterizaciones de los MLCCs contra  $V_{\text{bias}}$  se utilizó un VNA (ver Fig. 3.1) que incluye una T de polarización interna. La aplicación de  $V_{\text{bias}}$  se realizó con una fuente de voltaje Keithley con número de parte 2230-30-1. Ésta permite la aplicación de voltajes CC de hasta 30 V.

Durante la caracterización de los MLCCs contra  $V_{\text{bias}}$  se obtuvo un comportamiento inesperado de la T de polarización. Ésta exhibe características dependientes con  $V_{\text{bias}}$ . Lo cual indica que está construida con MLCCs Clase II. En tal caso, el capacitor  $C_{\text{int}}$  en la Fig. 3.2 es dependiente de la polarización. Como se mencionó anteriormente, cuando una T cambia sus propiedades eléctricas con la aplicación de un voltaje CC, también cambian los errores sistemáticos introducidos por ésta en la ruta de señal de RF. Esto produce una degradación de la calibración y afecta el resultado de las mediciones, especialmente en bajas frecuencias (ver sección 2.3).

Para mostrar la dependencia de la T de polarización con un voltaje CC primero se realizó una calibración SOL del VNA con  $V_{\text{bias}} = 0$  V. Después, se caracterizó al DUT,  $C_{1.0\mu\text{F}}$ , con diferentes valores de  $V_{\text{bias}}$  incrementándolo en pasos de 1 V en un rango de 0 V hasta 25 V. La estructura terminada en corto circuito se midió con  $V_{\text{bias}} = 0$  V, pero inmediatamente después de haber aplicado cada  $V_{\text{bias}}$  al DUT.

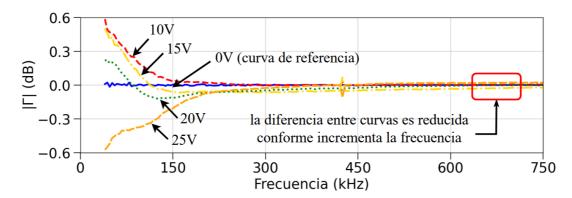

La Fig. 3.6 muestra el coeficiente de reflexión de la estructura terminada en corto circuito. Debido a su reflectividad, se espera que  $|\Gamma| \approx 0$  dB (i.e., una terminación completamente reflejante). Esto se cumple para una medición realizada después de haber aplicado 0 V al DUT (curva de referencia). Sin embargo, éste no es el caso para las mediciones posteriores a la aplicación de otros voltajes. Notar que la diferencia entre la curva de referencia y las otras curvas es mayor a frecuencias más bajas. Por otro lado, que  $|\Gamma|$  sea positivo en algunos casos, no representa algún cambio físico en la estructura terminada en corto circuito, más bien, es atribuible a la degradación de la calibración debido a la dependencia de la T de polarización con  $V_{\rm bias}$ .

Fig. 3.6 Coeficiente de reflexión de la estructura de prueba terminada en corto circuito obtenido de mediciones realizadas con  $V_{\text{bias}} = 0$  V, pero justo después de haber aplicado un voltaje CC al dispositivo  $C_{1.0\mu\text{F}}$  con la T interna del VNA.

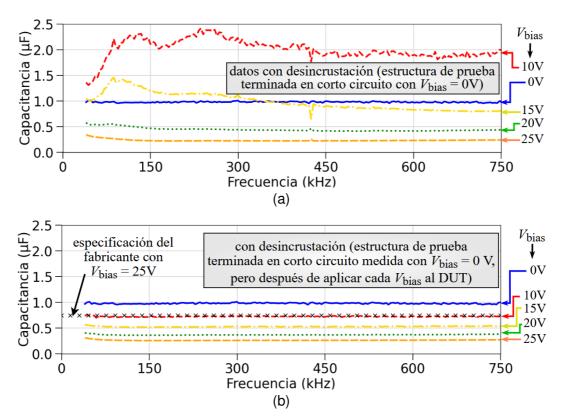

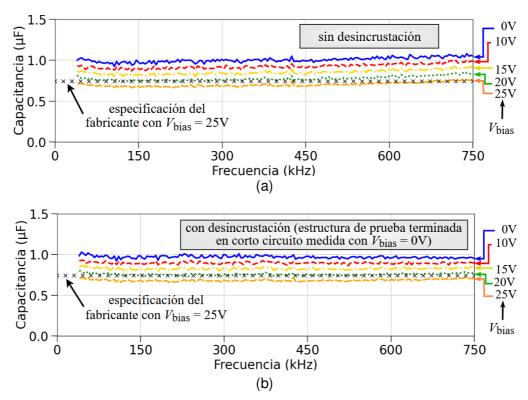

En la Fig. 3.7(a) se muestra el resultado de las mediciones para el capacitor Clase II,  $C_{1.0\mu\text{F}}$ , con algunos valores de  $V_{\text{bias}}$ . Se espera una disminución en la capacitancia efectiva de este conforme  $V_{\text{bias}}$  es mayor. Sin embargo, podemos notar que las curvas de la capacitancia no siguen el comportamiento esperado. Esto es debido, nuevamente, a la degradación la calibración. Esta degradación permanece aún después de configurar  $V_{\text{bias}} = 0 \text{ V}$  y se debe a un fenómeno de histéresis que existe en el dieléctrico de algunos capacitores MLCCs; en este caso, del capacitor  $C_{\text{int}}$  con que la T interna del VNA está construida (ver Fig. 3.2).

Se podría suponer que la medición de la estructura de prueba terminada en corto circuito, "captura efectivamente" los errores introducidos por la dependencia de la T con  $V_{\text{bias}}$ . Haciendo esta consideración, sería posible realizar un proceso de desincrustación para remover estos errores de los datos obtenidos para  $C_{1.0\mu\text{F}}$ . La Fig. 3.7(b) muestra el resultado de este procedimiento. Observar que, aunque las curvas de capacitancia tienen una mejora considerable y siguen el comportamiento esperado para un capacitor Clase II, la variación de la capacitancia excede, por mucho, lo especificado por el fabricante. Esto se debe a que los errores sistemáticos ocurren en  $C_{\text{int}}$ , antes del plano de referencia (ver Fig. 3.2). Además, la estructura terminada en corto circuito no se me mide exactamente en las mismas condiciones que el DUT, ya que no es posible medir un corto circuito mientras se aplica un voltaje CC.

Fig. 3.7 Curvas de capacitancia de  $C_{1.0\mu F}$  obtenidas a través de mediciones con diferentes  $V_{\text{bias}}$  aplicados con la T de polarización interna del VNA: a) desincrustación con estructura de prueba terminada en corto circuito y medida con  $V_{\text{bias}} = 0$  V, b) desincrustación con la estructura de prueba terminada en corto circuito medida justo después de haber aplicado  $V_{\text{bias}}$  al DUT.

#### 3.4 Diseño de la T de polarización externa

Se realizaron dos diseños de Ts de polarización con topologías basadas en circuitos *RC* y *LC*. Esto con el fin de reducir los errores en las mediciones debido a la dependencia de la T interna del VNA con *V*<sub>bias</sub>. Ambas Ts fueron caracterizadas en un rango de frecuencia de 50 kHz a 1 MHz. Éstas muestran algunas diferencias en su desempeño, especialmente en los parámetros de aislamiento y pérdidas por inserción. La Fig. 3.8 muestra su topología.

Se pueden obtener magnitudes grandes de capacitancia e inductancia implementando múltiples capacitores en paralelo e inductores en serie. Esto mejora el desempeño de una T de polarización en bajas frecuencias. En la Fig. 3.8,  $C_{\rm ext}$  es un capacitor MLCC Clase I, por lo que, su capacitancia nominal, 100 nF, es estable

contra temperatura y voltaje de polarización.  $L_{\rm ext}$  está compuesta de dos inductores en serie con una inductancia de 100  $\mu$ H cada uno.  $R_{\rm ext1}$  tiene una resistencia nominal de 47  $k\Omega$ , mientras que  $R_{\rm ext2}$ , tiene un valor de 100  $k\Omega$ .

Fig. 3.8 Topologías de T de polarización implementadas para la caracterización de capacitores cerámicos MLCC. Basada en un circuito: a) LC, b) RC.

La Fig. 3.9 muestra la configuración utilizada para la caracterización de las T de polarización. Esto se llevó a cabo con una VNA portátil de dos puertos, el cual es de bajo costo. Éste fue calibrado con sus estándares de calibración abierto, corto, carga y a través. La impedancia de referencia de los parámetros S obtenidos es de 50  $\Omega$ . Para caracterizar las T, primero, P<sub>1</sub> y P<sub>3</sub> se conectaron al VNA, mientras que P<sub>2</sub> se terminó en una carga acoplada de 50  $\Omega$ , con esto se obtuvieron los parámetros  $S_{11}$  y  $S_{31}$  de la T. Después, para obtener  $S_{21}$ , P<sub>1</sub> y P<sub>2</sub> se conectaron al VNA mientras que P<sub>3</sub> se terminó en una carga de 50  $\Omega$ .

Fig. 3.9 Configuración para la caracterización de las Ts de polarización utilizando un VNA portátil de dos puertos.

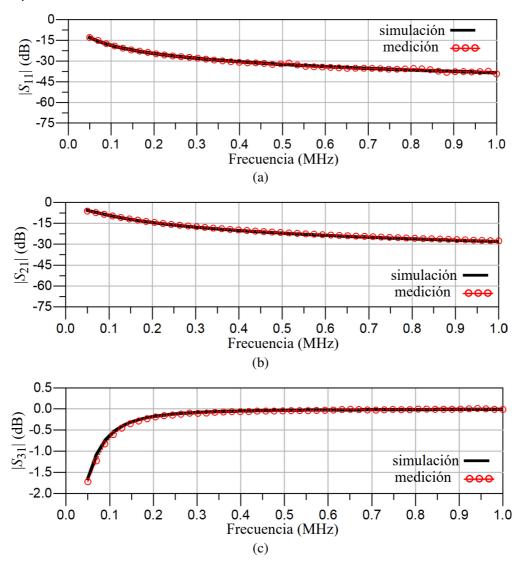

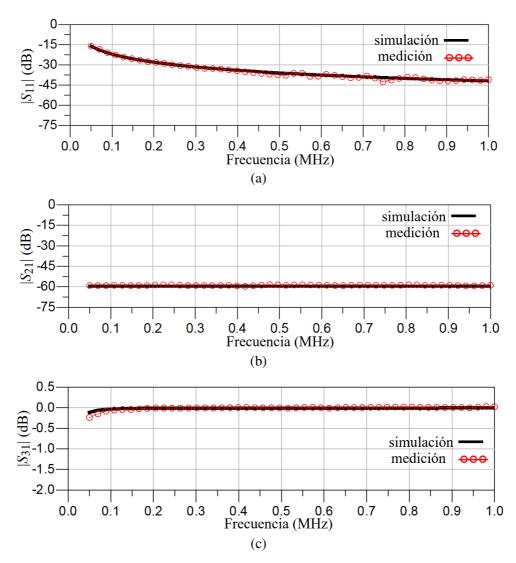

También se realizaron simulaciones de los circuitos de la Fig. 3.8 y los resultados de estas se compararon con los obtenidos de la caracterización en RF de las Ts. Las figuras 3.10 y 3.11 muestran los parámetros S de las mediciones y simulaciones de una T de polarización con una topología basada en un circuito LC y RC respectivamente. Como referencia, las simulaciones se hicieron en un programa tipo SPICE considerando los componentes de la red eléctrica.

De las figuras 3.10 y 3.11 se puede notar que todos los parámetros obtenidos a través de mediciones tienen gran correlación con los obtenidos de simulaciones. Al comparar el parámetro de reflexión ( $S_{11}$ ) en las figuras 3.10(a) y 3.11(a) se puede observar que éstos son muy similares. Este parámetro depende principalmente del valor de capacitancia de  $C_{\rm ext}$ , que es el mismo para ambas T de polarización. Por otro lado,  $S_{11}$  disminuye su magnitud (menor reflexión) conforme incrementa la frecuencia de operación. Esto se debe a que la impedancia del capacitor  $C_{\rm ext}$  disminuye de acuerdo con la expresión  $|Z_{\rm C}| \approx 1/\omega C$ .

Haciendo una comparación entre las figuras 3.10(b) y 3.11(b) se puede notar que los parámetros de aislamiento ( $S_{21}$ ) son diferentes. Una T con topología como la mostrada en la Fig. 3.8(a), presenta un incremento en el aislamiento,  $S_{21}$ , conforme la frecuencia de operación es mayor. Dicho comportamiento se debe a que la impedancia del inductor,  $L_{\text{ext}}$ , aumenta con la frecuencia según la expresión  $|Z_L| \approx \omega L$ . Por otro lado, en la Fig. 3.11(b) el parámetro de aislamiento es grande (alrededor de -60 dB) y contante, debido a que la impedancia del resistor  $R_{\text{ext1}}$  (Fig. 3.8(b)) idealmente, no depende de la frecuencia según la expresión  $|Z_R| \approx R$ . Como se mencionó anteriormente, una impedancia mayor proporciona un aislamiento mayor. Al comparar las figuras 3.10(c) y 3.11(c) se puede notar que la T de polarización basada en un circuito RC (Fig. 3.8(b)) presenta menos pérdidas por inserción ( $S_{31}$ ) especialmente a más bajas frecuencias.

En resumen, en una T de polarización: i) una capacitancia grande presenta una impedancia pequeña mejorando el parámetro de reflexión, ii) una impedancia mayor debida a un resistor o inductor mejora el parámetro de aislamiento, y iii), el uso de

un resistor permite que el aislamiento sea grande, aun en bajas frecuencias, con lo cual se disminuyen las pérdidas por inserción.

Considerando el análisis que se acaba de describir, en este trabajo es utilizada la T basada en un circuito *RC* (Fig. 3.8(b)). Esto debido a que presenta mejores características de aislamiento y menos pérdidas por inserción, especialmente en el rango de frecuencia de interés de 40 kHz a 750 kHz. Hay que mencionar que la demanda de corriente CC no representa un problema, esta es de baja magnitud ya que depende solamente del MLCC a caracterizar.

Fig. 3.10 Comparación entre parámetros S obtenidos de una simulación y mediciones de una T de polarización con una topología como la mostrada en la Fig.3.8(a): a) perdidas por retorno, b) aislamiento y c) perdidas por inserción.

Fig. 3.11 Comparación entre parámetros S obtenidos de una simulación y mediciones de una T de polarización con una topología como la mostrada en la Fig.3.8(b): a) pérdidas por retorno, b) aislamiento y c) pérdidas por inserción.

# 3.5 Descripción de la T de polarización propuesta en esta tesis 3.5.1 Diseño e implementación de la T externa

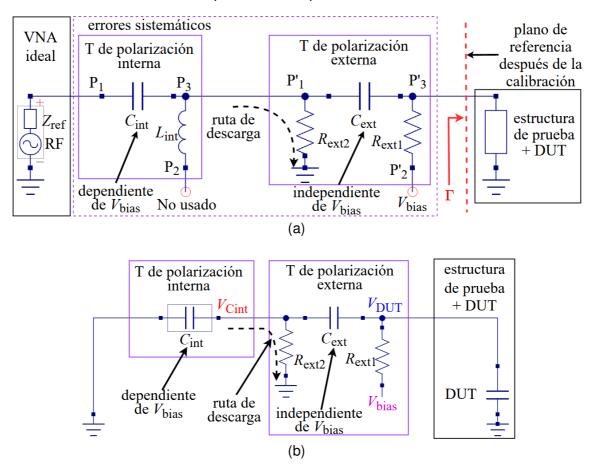

La Fig. 3.12(a) muestra el circuito simplificado de la configuración usada para mediciones de un puerto implementando una T de polarización externa. Ya que ambas Ts, la interna y externa, modifican las características de la ruta de señal RF, éstas se consideran como fuente de errores sistemáticos.

La Fig. 3.12(b) muestra un circuito equivalente de la Fig. 3.12(a), pero sólo se consideran algunos elementos para un análisis transitorio al cambiar el valor de  $V_{\rm bias}$ . En este caso, la señal de RF generada por el VNA es muy pequeña, por lo que puede despreciarse.  $L_{\rm int}$  tampoco es considerado, ya que permanece como un circuito abierto, mientras que la contribución de los efectos parásitos debidos a la estructura de prueba también es despreciada. En otras palabras, el DUT se considera como un elemento puramente capacitivo.

Fig. 3.12 Circuito de configuración para mediciones de un puerto implementando una T externa: (a) considerando características en RF, (b) circuito equivalente considerando solo algunos elementos para un análisis transitorio.

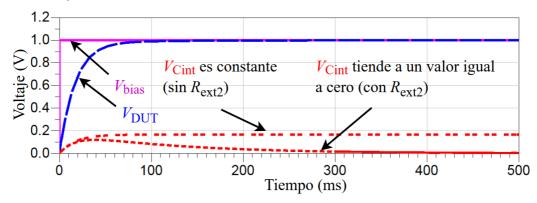

Un punto clave descubierto durante el desarrollo de este trabajo y que determina el diseño final del circuito propuesto es que en la Fig. 3.12(b), sin la presencia de  $R_{\rm ext2}$ ,  $C_{\rm int}$  y  $C_{\rm ext}$  quedarían conectados con una configuración en serie, formado un divisor de voltaje capacitivo. La inconveniencia de este hecho es que, al aplicar un voltaje,

$V_{\text{bias}}$ , una fracción de éste se mantendría entre las terminales de  $C_{\text{int}}$ . Entonces, ya que  $C_{\text{int}}$  es sensible al voltaje que se la aplica, esto causaría una variación de su magnitud que a su vez degradaría la calibración del VNA. En consecuencia, sin resolver este problema poco serviría usar una T externa independiente de  $V_{\text{bias}}$ . Por esta razón, el resistor,  $R_{\text{ext2}}$ , es agregado considerando que la T interna del VNA permanece conectada y sirve como ruta de descarga del capacitor de  $C_{\text{int}}$ . Convenientemente,  $R_{\text{ext2}}$  impide que exista un voltaje grande entre las terminales de  $C_{\text{int}}$  y evita la degradación de la calibración.

La Fig. 3.13 muestra el resultado de la simulación de un análisis transitorio del circuito en la Fig. 3.12(b) al cambiar  $V_{\text{bias}}$ . Se presentan los casos sin implementar e implementando al resistor  $R_{\text{ext2}}$  en la T de polarización externa. Para la simulación, el valor de  $C_{\text{int}}$  tiene una capacitancia de 1.0  $\mu\text{F}$  y el DUT de 0.2  $\mu\text{F}$ .  $V_{\text{bias}}$  se considera como un escalón unitario.  $V_{\text{Cint}}$  y  $V_{\text{DUT}}$  son los voltajes del capacitor  $C_{\text{int}}$  y del DUT respectivamente.

Fig. 3.13 Resultado de un análisis transitorio del circuito presentado en la Fig. 3.12(b). Se compara el voltaje en  $C_{int}$  como respuesta a la aplicación de  $V_{bias}$  para los casos en que se implementa o no al resistor  $R_{ext2}$ .

#### 3.5.2 Verificación experimental del circuito propuesto

La Fig. 3.14 muestra una fotografía de la configuración para mediciones utilizando un VNA con la T de polarización externa diseñada y fabricada como parte de este proyecto de tesis. Con dicha configuración, se realizó nuevamente una caracterización para los dispositivos listados en la Tabla 3.1. Primero, se llevó a cabo una calibración SOL en el puerto P'3 de la T externa, por lo que el plano de referencia se sitúa al final de dicho puerto. Después de eso, se realizó la medición

de las estructuras de prueba terminadas en corto circuito y en circuito abierto únicamente con  $V_{\text{bias}} = 0 \text{ V}$ , y en la medición del DUT con  $V_{\text{bias}}$  desde 0 V hasta 25 V en pasos de 1 V.

Fig. 3.14 Configuración para mediciones de un puerto utilizando un VNA y una T de polarización externa. El plano de referencia se sitúa al final del puerto  $P'_3$  de la T.

Algunos resultados de la caracterización de  $C_{1.0\mu F}$  realizadas con el procedimiento descrito anteriormente se muestran en la Fig. 3.15. En esta se puede notar que la capacitancia obtenida experimentalmente disminuye conforme incrementa  $V_{\text{bias}}$ , lo cual es un comportamiento esperado para un capacitor Clase II. En este caso, si bien la variación de la capacitancia no es igual con lo especificado por el fabricante para  $V_{\text{bias}} = 25$  V, esta es muy parecida, aún sin proceso de desincrustación. Además, al comparar estos resultados con los presentados en la Fig.3.7(a) es notable que existe una diferencia y mejora considerable. La principal diferencia entre los datos con y sin desincrustación, en la Fig. 3.15, es un aplanamiento de las curvas en las frecuencias más altas para los datos con desincrustación.

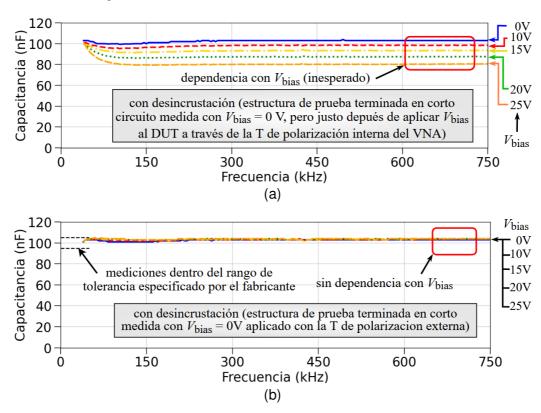

La Fig. 3.16(a) muestra los datos obtenidos de caracterizar el dispositivo  $C_{0.1\mu F}$  con diferentes  $V_{\text{bias}}$  aplicados a través de la T de polarización interna del VNA. Para esto se utilizó con una configuración como la que se muestra en la Fig. 3.1. Para la desincrustación, la estructura terminada en corto circuito fue medida con  $V_{\text{bias}} = 0$  V, pero inmediatamente después de aplicar  $V_{\text{bias}}$  al DUT.  $C_{0.1\mu F}$  es un capacitor Clase

I, por lo que su capacitancia es estable contra voltaje de polarización y temperatura. Sin embargo, los resultados mostrados en la Fig. 3.16(a) presentan una variación de la capacitancia. Este comportamiento es debido a la dependencia de la T interna del VNA con  $V_{\text{bias}}$  y, por lo tanto, puede considerarse como prueba de dicha dependencia.

Fig. 3.15 Curvas de capacitancia de  $C_{1.0\mu F}$  obtenidas a través de mediciones con diferentes  $V_{\text{bias}}$  aplicados con la T de polarización externa a) sin desincrustación, b) con desincrustación. La estructura de prueba terminada en corto circuito fue medida con  $V_{\text{bias}} = 0 \text{ V}$ .

La Fig. 3.16(b) muestra el resultado de caracterizar a  $C_{0.1\mu F}$  aplicando  $V_{\text{bias}}$  a través de la T de polarización externa. Es posible notar que no existe una variación en el resultado, aun si  $V_{\text{bias}}$  cambia. Esto confirma que el uso de la T de polarización externa (independiente de  $V_{\text{bias}}$ ) es útil para reducir los errores debidos a la T interna del VNA (dependiente de  $V_{\text{bias}}$ ). De esto, también se puede concluir que de no tomar en cuenta la dependencia de algunas T con  $V_{\text{bias}}$ , o al desconocer este efecto, erróneamente se podría atribuir a una dependencia de los MLCCs con  $V_{\text{bias}}$ . Sin

embargo, como se explica en este capítulo, estas variaciones son realmente debidas a una degradación de la calibración.

Fig. 3.16 Curvas de capacitancia de  $C_{0.1\mu F}$  obtenidas a través de mediciones con diferentes  $V_{\text{bias}}$  aplicados: a) con la T de polarización interna del VNA, b) a través de la T externa. Para la desincrustación la estructura de prueba terminada en corto circuito fue medida con  $V_{\text{bias}} = 0V$ .

## CAPÍTULO IV

#### 4. Resultados

En este capítulo se presentan resultados de la caracterización de múltiples MLCCs con diferentes capacitancias nominales y al aplicar un voltaje  $V_{\rm bias}$ . Además, se muestra un ejemplo en el cual un MLCC se utiliza para realizar compensación reactiva en una red de distribución de potencia, PDN. Este ejemplo demuestra cómo la variación en la capacitancia de un MLCC, debido a  $V_{\rm bias}$ , puede degradar sustancialmente el comportamiento de los circuitos comparando su desempeño con el considerado en la etapa de diseño. Esto da una idea general del por qué es importante la precisa determinación de dicha variación.

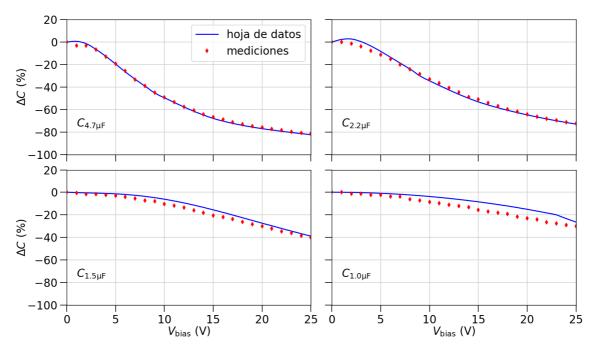

#### 4.1 Curvas de $\Delta C$ contra $V_{\text{bias}}$ obtenidas experimentalmente

Primeramente, se presentan los resultados de aplicar la metodología de caracterización propuesta y descrita en el Capítulo III, que demuestran la pertinencia

Fig. 4.1 Comparación del parámetro de variación de capacitancia contra  $V_{\text{bias}}$  para los MLCCs considerados en el Capítulo 3. Estas curvas fueron obtenidas experimentalmente y se comparan con las proporcionadas por los fabricantes. Los MLCCs fueron caracterizados aplicando  $V_{\text{bias}}$  desde 0 V hasta 25 V en pasos de 1 V a través de la T de polarización externa.

del uso de la T de polarización durante las mediciones eléctricas. En la Fig. 4.1 se muestran las curvas del parámetro que cuantifica la variación de la capacitancia ( $\Delta C$ ) contra  $V_{\text{bias}}$  (ver definición en la ecuación (4.1)). Estas curvas fueron obtenidas experimentalmente para diferentes MLCCs a partir de las mediciones del coeficiente de reflexión contra frecuencia. Nótese en estos resultados que las curvas tienen concordancia con los datos proporcionados en las hojas de especificación de los fabricantes. Cabe resaltar que éstos no mencionan la forma en que obtienen sus datos experimentales; de hecho, alguno de ellos indica que se empleó equipo de medición de impedancia sin abundar en detalles de la manera en que se polarizaron los capacitores. En contraparte, en este trabajo se está demostrando la factibilidad del uso de un VNA comercial, incluso con T de polarización interna y no optimizada para su uso en el rango de los kilohertz para caracterizar capacitancias de magnitud considerable, siempre y cuando se conecte en el puerto de salida la T de polarización diseñada en el Capítulo III.

Continuando con la descripción de los resultados, para realizar las mediciones, por favor referirse a la configuración mostrada en la Fig. 3.13. En este caso, el voltaje de alimentación  $V_{\text{bias}}$  fue aplicado a través de la T de polarización externa desde 0V hasta 25V en incrementos de 1V.

Con el propósito de cuantificar el cambio de capacitancia de un MLCC ante un estímulo de voltaje, se definió el parámetro  $\Delta C$ , que matemáticamente se calcula de la siguiente expresión:

$$\Delta C = \left(\frac{C_{bias}}{C_0} - 1\right) \times 100 \tag{4.1}$$

donde,  $C_{\text{bias}}$  es la capacitancia obtenida al aplicar algún voltaje de polarización,  $V_{\text{bias}}$ , y  $C_0$  es la capacitancia obtenida al aplicar  $V_{\text{bias}} = 0 \text{ V}$ .

Aunque la información proporcionada por los fabricantes es limitada, para el caso de los MLCCs,  $C_{4.7\mu F}$  y  $C_{2.2\mu F}$ , en la hoja de especificaciones se indica que sus capacitancias fueron obtenidas mediante equipo LCR y una frecuencia de 1 kHz, sin mencionar la manera en que se aplicaron los voltajes de corriente continua durante el proceso de medición. En este respecto, la ventaja de obtener las

capacitancias a frecuencias de kilohertz tiene que ver con el hecho de que al aumentar la frecuencia la reactancia capacitiva se ve significativamente reducida y la incertidumbre en su determinación experimental se ve incrementada. Cabe mencionar entonces que, aunque en este trabajo se realizó una caracterización a partir de una frecuencia de 40 kHz, la cual es mayor a la que se emplea en el caso de un LCR, los datos de capacitancia contra frecuencia no exhiben ruido considerable. Aunado a esto, nótese en la Fig. 4.1 que existe correlación entre los puntos de los datos obtenidos de las mediciones con los proporcionados por la hoja de datos de cada fabricante. Con estos resultados, es posible afirmar que el uso de la T de polarización externa permite la caracterización de MLCCs de manera precisa y aplicando diferentes  $V_{\text{bias}}$ . Además, los errores debidos a la dependencia de la T interna con  $V_{\text{bias}}$  se reducen de manera significativa.

#### 4.2 Ejemplo de aplicación

Para poner en evidencia la importancia de conocer de manera precisa la capacitancia de un MLCC bajo diferentes voltajes de polarización, se desarrolla un ejemplo en el cual el dispositivo  $C_{4.7\mu F}$ , caracterizado en este trabajo, se utiliza como parte de una etapa de una PDN. La Fig. 4.2 muestra el circuito equivalente de ésta. El módulo regulador de voltaje, VRM, idealmente proporciona un voltaje de CC a una carga a través de una interconexión sin pérdidas ni efectos reactivos. En este caso, para representar la demanda de energía variante en el tiempo que se presenta bajo condiciones prácticas, la carga es considerada como una fuente de corriente CA, cuya función es precisamente inducir una corriente variable en la red de alimentación. En la realidad, para conectar el VRM con la carga se requiere de cables o conductores eléctricos que introducen efectos parásitos en la ruta de voltaje; en una PDN, esta ruta es comúnmente conocida como riel de potencia. Específicamente, los efectos parásitos dominantes en este riel son representados por un inductor y un resistor,  $L_{\text{riel}}$  y  $R_{\text{riel}}$ , respectivamente; mientras que como se ha dicho, la fuente de CA simula una carga que demanda una corriente no constante en el tiempo. Esta corriente puede deberse, por ejemplo, a transistores en un procesador que operan a diferentes frecuencias. Así, para el análisis de la PDN en este ejemplo, se considera una corriente máxima pico de 1 A. Finalmente, el dispositivo  $C_{4.7\mu F}$  es implementado como decap, por lo que está conectado en paralelo con el VRM. Debido a que ningún elemento es perfecto,  $C_{4.7\mu F}$  también introduce efectos parásitos. Éstos son representados por un inductor,  $L_{decap}$ , y un resistor,  $R_{decap}$ .

Fig. 4.2 Circuito equivalente de una etapa en una PDN utilizando al dispositivo  $C_{4.7\mu F}$  como capacitor de desacoplamiento.

En la Fig. 4.2,  $\Delta V$ , es el voltaje pico a pico o variaciones que se producen en el voltaje total de la carga.  $V_{\text{carga}}$ , corresponde al voltaje CC en la carga. El voltaje total de la carga ( $V_{\text{carga}} + \Delta V$ ) debe mantenerse constante, ya que una variación considerable de éste puede afectar la fiabilidad y rendimiento de la misma carga. Idealmente, el VRM proporciona un voltaje de CC,  $V_{\text{VRM}}$ , a la carga, por lo que ( $V_{\text{carga}} + \Delta V$ ) =  $V_{\text{VRM}}$ . Esto debería cumplirse, sin importar la corriente que la carga demandara. Sin embargo, debido a los efectos parásitos en el riel de potencia siempre existirá una caída de tensión en la red. Entonces, como se verá a continuación, una demanda de corriente variable produce variaciones en el voltaje total de la carga.

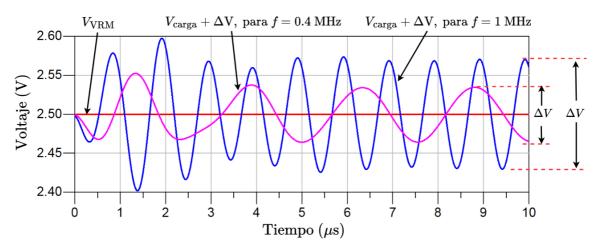

La Fig. 4.3 muestra resultados obtenidos de una simulación de un análisis transitorio del circuito en la Fig. 4.2 con  $V_{VRM} = 2.5$  V. Se presenta la variación del voltaje total de la carga, ( $V_{carga} + \Delta V$ ), para dos casos operando a frecuencias de 0.4 MHz y 1 MHz. De los resultados, es notable que el voltaje total en la carga no corresponde solamente a un voltaje de CC, sino que éste varia con el tiempo. Además,  $\Delta V$  o la variación de voltaje presenta diferentes amplitudes para cada frecuencia

considerada. En realidad,  $\Delta V$  tiene una tendencia a incrementar conforme aumenta la frecuencia de operación. Esto se debe a que, la reactancia de  $L_{\text{riel}}$  incrementa con la frecuencia, lo cual produce una mayor caída de voltaje en la carga. Lo anterior representa limitantes en cuanto a la frecuencia máxima de operación del circuito, ya que, el sobrepasar la tolerancia de voltaje de la carga (por ejemplo, un IC) ésta puede dañarse.

Fig. 4.3 Simulación de un análisis transitorio del circuito en la Fig. 4.2. Se muestran los resultados para la carga operando a frecuencias de 0.4 MHz y 1 MHz.

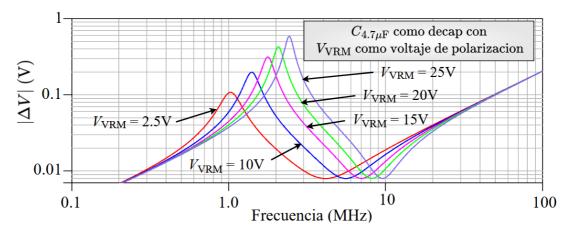

La Fig. 4.4 muestra el resultado de una simulación en el domino de la frecuencia (simulación de CA) del circuito de la Fig. 4.2, pero con  $V_{\rm VRM}$  con diferentes voltajes. Como se mencionó anteriormente, debido al efecto de  $L_{\rm riel}$ , al aumentar la frecuencia de operación (f) de la carga,  $\Delta V$  sería cada vez mayor. Sin embargo, incluyendo un capacitor de compensación en paralelo este problema se puede resolver. Notar, por ejemplo, en la Fig. 4.4 que el capacitor de desacoplamiento,  $C_{4.7\mu\rm F}$ , realiza una compensación reactiva de  $L_{\rm riel}$  e impide que  $\Delta V$  incremente constantemente con la frecuencia. Desafortunadamente, debido a que  $C_{4.7\mu\rm F}$  presenta una capacitancia dependiente del voltaje polarización (ver Fig. 4.1), la compensación que  $C_{4.7\mu\rm F}$  realiza para  $L_{\rm riel}$  es diferente en cada valor de  $V_{\rm VRM}$ . Así, para un valor de  $V_{\rm VRM} = 2.5$  V, el  $\Delta V$  máximo es de alrededor de 0.1 V y se presenta a una frecuencia de operación de 1 MHz. Mientras que, para  $V_{\rm VRM} = 10$  V, el  $\Delta V$  máximo es de alrededor de 0.2 V, a una frecuencia de 1.5 MHz. En general, conforme  $V_{\rm VRM}$  aumenta,  $C_{4.7\mu\rm F}$  presenta una disminución en su capacitancia. Esto se traduce en una menor

compensación reactiva para  $L_{\text{riel}}$  y provoca que exista un  $\Delta V$  máximo de mayor magnitud para frecuencias de operación mayores.

Fig. 4.4 Simulación CA del circuito en la Fig. 4.2. Se puede observar el comportamiento de  $\Delta V$  conforme la carga incrementa su frecuencia de operación y para diferentes voltajes de  $V_{VRM}$ .

De acuerdo con la discusión anterior, conocer el comportamiento de  $C_{4.7\mu F}$  para diferentes voltajes de polarización, permite determinar cuál será el desempeño de un circuito bajo ciertas condiciones, por ejemplo, polarización y frecuencias diferentes. A su vez, esto permite concluir si el diseño de una PDN cumple con las características o tolerancias requeridas en cuanto a desempeño y si éstas se encuentran dentro lo esperado. Del mismo modo, desconocer o ignorar las características de  $C_{4.7\mu F}$  puede originar diseños deficientes de algún sistema.

Es importante mencionar que los dispositivos listados en la Tabla 3.1 presentan una tolerancia con relación a su capacitancia nominal. Esta tolerancia es independiente de la variación de la capacitancia con el voltaje de polarización, por lo que, en realidad, la capacitancia que especifica el fabricante puede variar más de lo esperado. En circuitos eléctricos de gran densidad de componentes, esto puede considerarse como un efecto adverso, especialmente para diseños que no admiten grandes tolerancias.

#### 4.3 Consideraciones al reducir la reactancia

Existen consideraciones importantes que deben tomarse en cuenta durante la caracterización de capacitores que exhiben una reactancia pequeña, ya sea por la

frecuencia en que se realiza la caracterización o por la magnitud de su capacitancia. La reactancia capacitiva,  $X_{C}$ , corresponde a la parte imaginaria de  $Z'_{DUT}$  obtenida de la caracterización de los MLCCs. Así, esta reactancia puede calcularse de la siguiente la expresión:

$$X_C = \operatorname{Im}(Z'_{DUT}) = \frac{1}{\omega C} \tag{4.1}$$

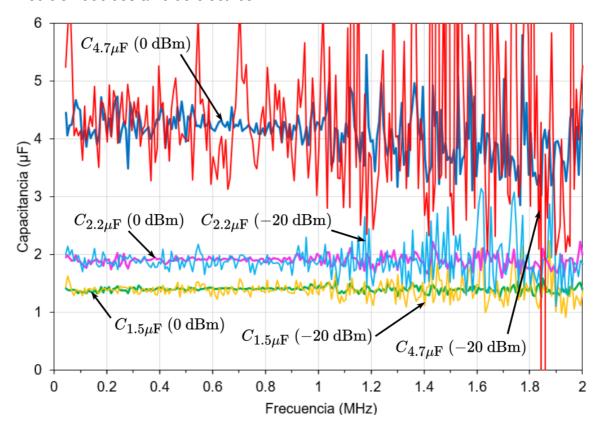

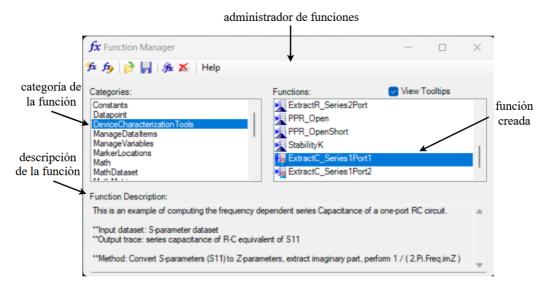

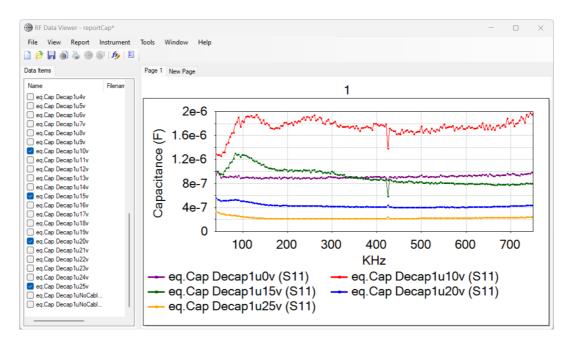

donde *C* es la capacitancia del capacitor.