# Generadores de números aleatorios y su aplicación para cifrar y autenticar datos digitales

por

# José David Rodríguez Muñoz

Tesis sometida como requisito parcial para obtener el grado de:

# MAESTRO EN CIENCIAS EN LA ESPECIALIDAD DE ELECTRÓNICA

por el

# Instituto Nacional de Astrofísica, Óptica y Electrónica

Noviembre 2024 Tonantzintla, Puebla

Supervisada por:

# Dr. Esteban Tlelo Cuautle

Investigador Titular del INAOE

y

# Dr. Luis Gerardo de la Fraga

Departamento de Computación, Cinvestav

### **©INAOE 2024**

Derechos Reservados El autor otorga al INAOE el permiso de reproducir y distribuir copias de esta tesis en su totalidad o en partes mencionando la fuente.

A mi familia y amigos, quienes siempre me han apoyado.

# Resumen

Actualmente, el mundo ha experimentado un incremento en el número de dispositivos electrónicos conectados a las redes inalámbricas. Por esta razón, los investigadores buscan desarrollar algoritmos criptográficos más robustos que garanticen privacidad y seguridad en el proceso de comunicación. Un componente con aplicaciones generales en el campo de la criptografía es el generador de números aleatorios (RNG), el cual proporciona una secuencia de números sin patrón predecible que se emplean en algoritmos de cifrado y autenticación de datos. Sin embargo, el reto actual consiste en garantizar la mejor aleatoriedad de las secuencias, la cual es medida mediante pruebas estadísticas como las NIST y TestU01. Una opción en el diseño de estos generadores es el uso de sistemas caóticos de tiempo continuo y discreto, debido a las propiedades de estos modelos matemáticos. Estos sistemas tienen como ventaja un bajo consumo de elementos de hardware digital que pueden describirse en Verilog y llevarse a layout para su fabricación en tecnologías de circuitos integrados CMOS. Por otra parte, son fáciles de codificar en un lenguaje de programación de alto nivel, como Python, para diversas aplicaciones en sistemas embebidos. Debido a lo anterior, en esta tesis se diseñan generadores de números pseudoaleatorios (PRNGs) basados en sistemas caóticos, los cuales se sintetizan en un arreglo de compuertas programables en campo (FPGA) usando aritmética de 64-bit y también se implementan en una Raspberry Pi. Además, se verifica la aleatoriedad de las secuencias generadas por cada PRNG y se aplican en un sistema de comunicación con etapas de cifrado y de autenticación de datos mediante un algoritmo de función hash, que permite generar etiquetas para corroborar la integridad de la información que se envía o almacena, como imágenes en tono de grises, imágenes RGB v texto. En el caso del sistema sintetizado en la FPGA, la comunicación se realiza entre la FPGA y una computadora utilizando el protocolo RS232. Por otro lado, en el sistema implementado en Raspberry Pi se emplea el protocolo de comunicación MQTT entre tres de estos dispositivos.

# **Abstract**

Nowadays, there has been a significant increase in the number of electronic devices connected to wireless networks. As a result, researchers are seeking to develop more robust cryptographic algorithms that ensure privacy and security in the communication process. A component with general applications in cryptography is the Random Number Generator (RNG). This generator produces a sequence of numbers without a predictable pattern, and it can be used in encryption and data authentication algorithms. However, the current challenge is how to ensure the best possible randomness of the binary sequences, which can be measured by statistical tests such as NIST and TestU01. Due to the properties of these mathematical models, continuous and discrete-time chaotic systems are an option in the design of these generators. These systems offer the advantage of low consumption of digital hardware elements, which could be described using Verilog and are suitable for manufacturing in CMOS integrated circuit technologies. Moreover, they are easy to code in a high-level programming language, such as Python, for various applications in embedded systems. Due to the above, in this thesis, Pseudo-Random Number Generators (PRNGs) based on chaotic systems are designed and synthesized in a Field-Programmable Gate Array (FPGA) using 64-bit arithmetic and also implemented on a Raspberry Pi. In addition, the randomness of the sequences generated by each PRNG is verified and applied in encryption and authentication stages using a hash function algorithm, which allows the generating of authentication tags for the information that is sent or stored, such as grayscale images, RGB images, and text. In the case of the chaos-based system synthesized in the FPGA, the communication occurs between the FP-GA and a computer using the RS232 protocol. On the other hand, in the system implemented in Raspberry Pi the communication uses the MQTT communication protocol among three of these devices.

# **Agradecimientos**

Quiero comenzar expresando mi agradecimiento a Dios por permitirme trabajar en este proyecto y por concederme la sabiduría para llevarlo a cabo. Mi agradecimiento más sincero para mi madre Inés Gabriela Muñoz González, mi padre Hermilo Rodríguez García y mis hermanos Josué Daniel y Uzziel Abisai, quienes me brindaron su apoyo incondicional durante todo el desarrollo de esta tesis.

Agradezco a mis dos asesores por su invaluable guía, por la constante enseñanza y por resolver cada una de mis dudas a lo largo del proyecto. Su apoyo y orientación han sido fundamentales para esta tesis.

Al CONAHCYT México, por otorgarme la beca que me permitió llevar a cabo mis estudios de maestría en el INAOE.

Por último, agradezco a mis amigos y compañeros, quienes compartieron su tiempo, conocimiento y amistad.

Muchas gracias a todos.

# Índice general

| Re | esum   | en                                                        | Ш  |

|----|--------|-----------------------------------------------------------|----|

| Αŀ | ostrac | ct                                                        | IV |

| Αç | grade  | ecimientos                                                | ٧  |

| ĺn | dice ( | general                                                   | IX |

| 1. | Intro  | oducción                                                  | 1  |

|    | 1.1.   | Concepto y características del caos                       | 1  |

|    | 1.2.   | Análisis de sistemas caóticos                             | 2  |

|    | 1.3.   | Generadores de números aleatorios                         | 5  |

|    | 1.4.   | Cifrado y autenticación de mensajes                       | 8  |

|    | 1.5.   | Acerca de la FPGA y la Raspberry Pi 3                     | 10 |

|    | 1.6.   | Hipótesis                                                 | 11 |

|    | 1.7.   | Objetivos                                                 | 11 |

|    |        | 1.7.1. Objetivo general                                   | 11 |

|    |        | 1.7.2. Objetivos específicos                              | 11 |

|    | 1.8.   | Organización de la tesis                                  | 12 |

| 2. | Sist   | remas caóticos                                            | 13 |

|    | 2.1.   | Descripción de los sistemas caóticos                      | 13 |

|    |        | 2.1.1. Mapas caóticos                                     | 13 |

|    |        | 2.1.2. Mapa caótico 2D de Sprott                          | 14 |

|    |        | 2.1.2.1. Simulación de las series temporales y atractores | 15 |

|    |      |         | 2.1.2.2.  | Exponentes de Lyapunov y dimensión fractal           | 16 |

|----|------|---------|-----------|------------------------------------------------------|----|

|    |      | 2.1.3.  | Sistema   | s caóticos en tiempo continuo                        | 17 |

|    |      | 2.1.4.  | Sistema   | caótico 3D basado en un memristor                    | 18 |

|    |      |         | 2.1.4.1.  | Puntos de equilibrio y valores propios               | 19 |

|    |      |         | 2.1.4.2.  | Simulación de las series temporales y atractores     | 19 |

|    |      |         | 2.1.4.3.  | Exponentes de Lyapunov y dimensión Kaplan-Yorke      | 20 |

|    |      | 2.1.5.  | Sistema   | caótico 4D                                           | 21 |

|    |      |         | 2.1.5.1.  | Puntos de equilibrio                                 | 22 |

|    |      |         | 2.1.5.2.  | Simulación de las series temporales y atractores     | 22 |

|    |      |         | 2.1.5.3.  | Exponentes de Lyapunov y dimensión Kaplan-Yorke      | 23 |

| 3. | Des  | cripció | n y sínte | sis de sistemas caóticos y PRNGs en FPGAs            | 25 |

|    |      | •       | -         | re la aritmética de computadora                      | 26 |

|    | 3.2. | Descri  | pciones o | de sistemas caóticos                                 | 27 |

|    |      | 3.2.1.  | Descripo  | sión del sistema 3D basado en un memristor           | 27 |

|    |      |         | 3.2.1.1.  | Análisis de amplitudes para el formato de punto fijo | 27 |

|    |      |         | 3.2.1.2.  | Descripción del sistema mediante bloques digitales   | 28 |

|    |      |         | 3.2.1.3.  | Simulación del sistema en Verilog                    | 34 |

|    |      |         | 3.2.1.4.  | Resultados experimentales                            | 34 |

|    |      | 3.2.2.  | Descripo  | ción hardware del mapa caótico 2D                    | 34 |

|    |      |         | 3.2.2.1.  | Análisis de amplitudes para el formato de punto fijo | 34 |

|    |      |         | 3.2.2.2.  | Descripción del sistema mediante bloques digitales   | 35 |

|    |      |         | 3.2.2.3.  | Simulación del sistema en Verilog                    | 39 |

|    |      |         | 3.2.2.4.  | Resultados experimentales                            | 39 |

|    |      | 3.2.3.  | Descripo  | ción del sistema caótico en 4D                       | 40 |

|    |      |         | 3.2.3.1.  | Análisis de amplitudes para el formato de punto fijo | 40 |

|    |      |         | 3.2.3.2.  | Descripción del sistema mediante bloques digitales   | 40 |

|    |      |         | 3.2.3.3.  | Simulación del sistema en Verilog                    | 43 |

|    |      |         | 3.2.3.4.  | Resultados experimentales                            | 43 |

|    | 3.3. | Síntes  | is en FPC | GA de los sistemas caóticos                          | 43 |

|    | 2 /  | Dicoño  | do DDNI   | Co a partir do cictomas agáticas                     | 15 |

|    | 3.5. | Prueba  | as estadísticas NIST de aleatoriedad                                        | 47 |

|----|------|---------|-----------------------------------------------------------------------------|----|

| 4. | PRN  | IGs bas | sados en caos y sus aplicaciones en criptografía                            | 50 |

|    | 4.1. | Sistem  | nas de cifrado y autenticación utilizando PRNGs para comunicaciones seguras | 51 |

|    |      | 4.1.1.  | Esquemas de cifrado                                                         | 51 |

|    |      | 4.1.2.  | Etapas para autenticar mensajes                                             | 53 |

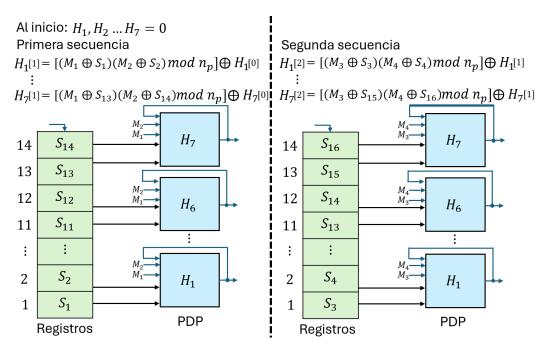

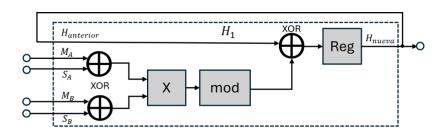

|    |      |         | 4.1.2.1. Función de hash basada en el producto pseudo punto                 | 54 |

|    |      | 4.1.3.  | Esquema de cifrado y autenticación general                                  | 55 |

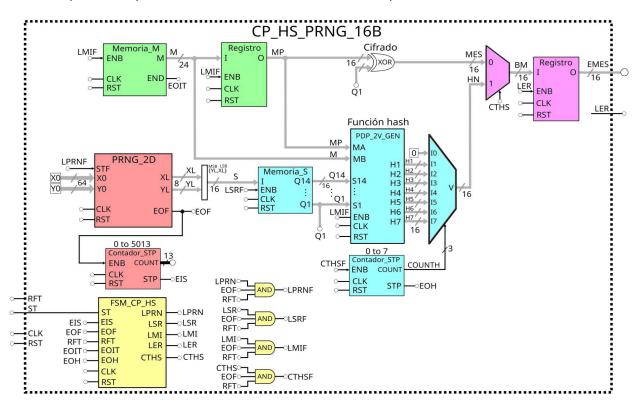

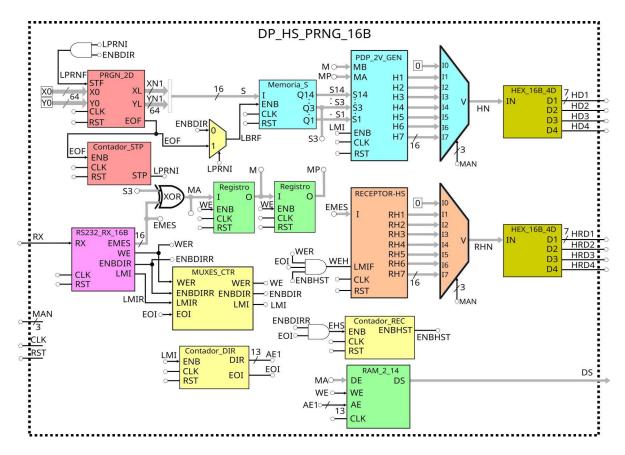

|    |      | 4.1.4.  | Esquema de cifrado y autenticación en FPGA                                  | 56 |

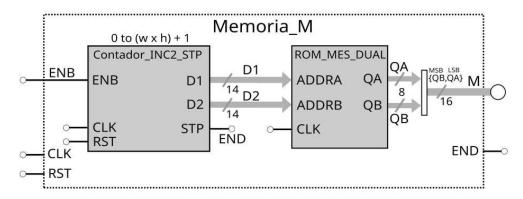

|    |      |         | 4.1.4.1. Bloque para almacenar el mensaje                                   | 58 |

|    |      |         | 4.1.4.2. Bloque de función de hash                                          | 59 |

|    |      |         | 4.1.4.3. Bloque de control                                                  | 62 |

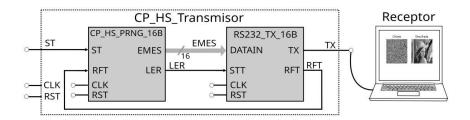

|    |      |         | 4.1.4.4. Transmisor y receptor con etapa RS232                              | 63 |

|    | 4.2. | Result  | ados del esquema de cifrado y autenticación en FPGA                         | 64 |

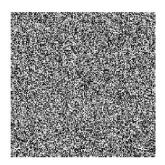

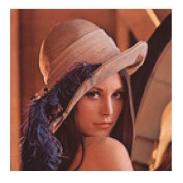

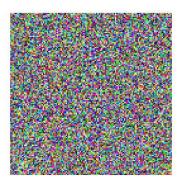

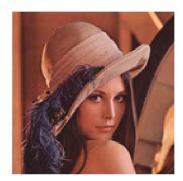

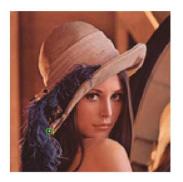

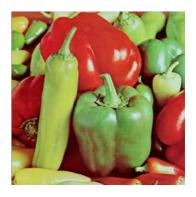

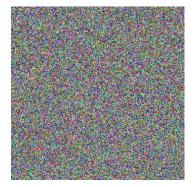

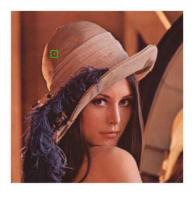

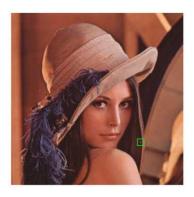

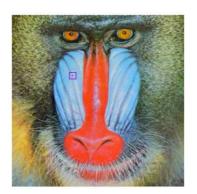

|    |      | 4.2.1.  | Cifrado y autenticación de imágenes a escala de grises                      | 65 |

|    |      | 4.2.2.  | Cifrado y autenticación de imágenes RGB                                     | 67 |

|    |      | 4.2.3.  | Cifrado y autenticación de texto                                            | 68 |

|    |      | 4.2.4.  | Consumo de recursos en la FPGA                                              | 69 |

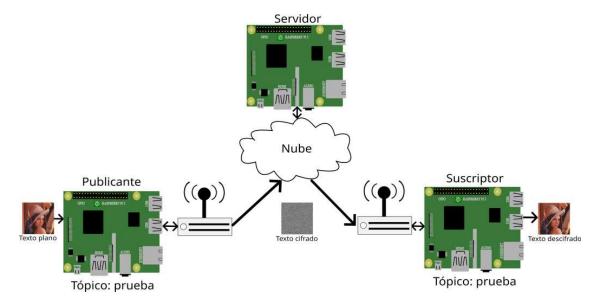

| 5. | Esq  | uema c  | le cifrado y autenticación bajo el protocolo MQTT en Raspberry Pi           | 71 |

|    | 5.1. | Introdu | ucción                                                                      | 71 |

|    | 5.2. | Diseño  | o de los PRNGs en Python                                                    | 7  |

|    | 5.3. | Prueba  | as estadísticas NIST                                                        | 73 |

|    | 5.4. | Sistem  | na de cifrado y autenticación de mensajes por protocolo MQTT                | 73 |

|    |      | 5.4.1.  | Etapa de cifrado y descifrado                                               | 75 |

|    |      | 5.4.2.  | Etapa de autenticación mediante la función de hash PDP                      | 76 |

|    | 5.5. | Result  | ados del esquema de cifrado y autenticación en Raspberry                    | 78 |

|    |      | 5.5.1.  | Cifrado y autenticación de imágenes RGB                                     | 78 |

|    |      | 5.5.2.  | Cifrado y autenticación de imágenes a escala de grises                      | 80 |

| 6. | Con  | clusior | nes                                                                         | 81 |

|    | 6 1  | Trahai  | o futuro                                                                    | 81 |

| Índice de figuras | 86 |

|-------------------|----|

| Índice de tablas  | 88 |

| Bibliografía      | 88 |

# Capítulo 1

# Introducción

# 1.1. Concepto y características del caos

El comportamiento caótico, un tema de interés en los recientes años, está presente en sistemas naturales y sociales, como en el clima, el fluido de un líquido, el crecimiento de una población, las epidemias, o incluso en una crisis financiera [1]. La definición de la palabra caos ha ido evolucionando a lo largo de la historia y hoy en día sugiere el desorden de algo [2]. En el contexto riguroso de las matemáticas y la física, el caos se define como el comportamiento determinista, acotado y aperiódico de un sistema dinámico, cuya característica principal es la alta sensibilidad a las condiciones iniciales [3]. Los modelos matemáticos que tienen este comportamiento emplean términos o funciones no lineales, y una primera clasificación para esta dinámica se basa en el tipo de ecuaciones utilizadas, las cuales pueden ser descripciones en tiempo continuo o discreto. Los sistemas que se modelan por ecuaciones diferenciales ordinarias en tiempo continuo, son llamados sistemas caóticos. Hoy en día, los sistemas caóticos están representados mediante ecuaciones diferenciales de orden entero o incluso de orden fraccionario. Por otro lado, los sistemas que generan caos y que se modelan por ecuaciones en tiempo discreto, son conocidos como mapas caóticos y usan ecuaciones de diferencias para su representación [4]. Un punto importante acerca de los modelos matemáticos, es que un sistema no lineal no garantiza el comportamiento caótico. Para presentarlo, el sistema debe tener al menos un exponente de Lyapunov positivo [5].

Como los modelos caóticos describen sistemas deterministas, la evolución temporal de sus variables de estado sigue una regla determinada por las condiciones iniciales y los parámetros

del sistema. Sin embargo, la alta sensibilidad a las condiciones iniciales provoca que, ante pequeños cambios en las condiciones, se obtengan trayectorias muy diferentes entre sí a medida que aumenta el tiempo. Además, en un espacio de fases, estas trayectorias se mantienen en una región delimitada conocida como atractor extraño, siempre y cuando las condiciones iniciales estén dentro de un rango válido de valores [6].

Dependiendo del análisis de los modelos matemáticos que describen a los sistemas caóticos, existe una clasificación que se basa en la definición del tipo de atractor, que puede ser autoexitado u oculto. En el primer caso, un atractor autoexcitado tiene una cuenca de atracción ligada a un punto de equilibrio inestable, mientras que un atractor oculto tiene una cuenca de atracción que no se cruza en la vecindad de algún punto de equilibrio [7]. Por tal motivo, los puntos de equilibrio y los valores propios de los modelos matemáticos asociados a los atractores autoexitados, se pueden encontrar mediante cálculos manuales. Por otro lado, los modelos matemáticos de los atractores ocultos, son difíciles de resolver y requieren de un procedimiento computacional avanzado para identificar y estimar los puntos de equilibrio y su dinámica en general [8].

Uno de los primeros científicos en trabajar con el caos fue Edward Norton Lorenz, quien en 1963 descubrió el comportamiento caótico mientras desarrollaba un modelo para predicción climática. Lorenz popularizó el concepto de efecto mariposa, que explica la sensibilidad de los sistemas caóticos a las condiciones iniciales [6]. El trabajo de Lorenz revolucionó el concepto del caos y sentó las bases para el desarrollo de la teoría del caos.

# 1.2. Análisis de sistemas caóticos

Los sistemas dinámicos en tiempo continuo, como los caóticos, están descritos por ecuaciones diferenciales ordinarias, cuya solución analítica o exacta no es posible de lograr en muchos casos. Por tal motivo, estos modelos se resuelven utilizando métodos numéricos que aproximan la solución a un problema de valor inicial de la forma  $\dot{\vec{x}}=f(x_1,x_2,\ldots,x_n,t)$ , donde  $\vec{x}=[x_1,x_2,\ldots,x_n]$ . Estos métodos resultan relativamente fáciles de implementar en una computadora. Básicamente, los métodos numéricos transforman las ecuaciones diferenciales ordinarias en un sistema de ecuaciones discretas iterativas, las cuales permiten calcular los valores futuros de las variables de estado a partir de valores pasados (o actuales) [9]. Sin embargo, cada método numérico requiere de un análisis para estimar el error que puede generar y el valor apropiado del tamaño de paso

de integración, para asegurar convergencia de la solución.

En la literatura existen varios métodos numéricos, categorizados como métodos de un solo paso o multi pasos, y en ambos casos pueden ser explícitos o implícitos [10]. Cada uno de ellos ofrece diferentes niveles de aproximación con la solución exacta, tiempo de cómputo y región de estabilidad. El más usado y considerado simple de programar en software o un entorno digital, es conocido con el nombre de Euler hacia adelante (Forward Euler). Este método, de un solo paso y explícito, aproxima la solución de un sistema de ecuaciones diferenciales ordinarias utilizando un bajo número de cálculos. Por ello, su tiempo de procesamiento en una computadora o sistema embebido es el de menor duración. Además, cuando se desea un diseño electrónico, el método de Euler hacia adelante requiere el menor consumo de recursos lógicos usando dispositivos como el arreglo de compuertas programables en el campo (FPGA) [11]. Sin embargo, su desventaja es que la solución aproximada arroja un mayor error comparado con otros métodos de mayor orden o de múltiples pasos, como la familia de métodos Adams Bashforth y Runge Kutta. Si la solución requiere de una mejor aproximación, el método de Runge Kutta de orden 4, es una de las opciones más utilizadas, aunque toma un mayor tiempo de procesamiento computacional. No obstante, la elección de uno u otro método numérico depende de la aplicación que se esté buscando.

La solución a un sistema de ecuaciones diferenciales ordinarias, aplicando métodos numéricos explícitos, requerirá de valores pasados, los cuales dependen del orden polinomial. Por ejemplo, la tabla 1.1 muestra las ecuaciones iterativas para los métodos explícitos de Euler hacia adelante (FE), Adams Bashforth de orden 4 (AB4) y Runge Kutta de orden 4 (RK4). Se puede apreciar que el método FE requiere de un solo valor pasado descrito por  $y_i$ , mientras que el método AB4 requiere de 4 valores previos, descritos por:  $y_{i-3}$ ,  $y_{i-2}$ ,  $y_{i-1}$ , y  $y_i$ . Por su parte, el método RK4 depende de un solo valor pasado descrito por  $y_i$ , sin embargo, evalúa 4 valores que son promediados por la expresión:  $\frac{1}{6}$  ( $k_1 + 2k_2 + 2k_3 + k_4$ ).

La selección de un tamaño de paso de integración h adecuado asegura la estabilidad del método numérico. Una forma para estimar dicho valor, consiste en analizar los valores propios del sistema dinámico, aunque este criterio podría no cumplirse en algunos problemas no lineales [12]. De esta manera, una vez estimado el paso de integración, se obtienen series temporales asociadas a cada variable de estado del sistema, y con ellas se efectúan estudios para determinar la posibilidad de generar secuencias binarias aleatorias.

El caos se puede evaluar haciendo uso de técnicas o herramientas matemáticas que ayudan a

Tabla 1.1: Métodos numéricos y sus ecuaciones iterativas [9].

| Método numérico | Ecuación iterativa                                                 |

|-----------------|--------------------------------------------------------------------|

| FE              | $y_{i+1} = y_i + hf(x_i, y_i)$                                     |

| AB4             | $y_{i+1} = y_i + h\left(\frac{55}{24}f(x_i, y_i)\right)$           |

|                 | $-\frac{59}{24}f(x_{i-1},y_{i-1})$                                 |

|                 | $+\frac{37}{24}f(x_{i-2},y_{i-2})$                                 |

|                 | $-\frac{9}{24}f(x_{i-3},y_{i-3})$                                  |

| RK4             | $y_{i+1} = y_i + \frac{1}{6}h\left(k_1 + 2k_2 + 2k_3 + k_4\right)$ |

|                 | $k_1 = f(x_i, y_i)$                                                |

|                 | $k_2 = f\left(x_i + \frac{1}{2}h, y_i + \frac{1}{2}k_1h\right)$    |

|                 | $k_3 = f\left(x_i + \frac{1}{2}h, y_i + \frac{1}{2}k_2h\right)$    |

|                 | $k_4 = f\left(x_i + h, y_i + k_3 h\right)$                         |

estudiar la complejidad de la dinámica caótica. Por ejemplo, el caos se puede medir a través de la evaluación de los exponentes de Lyapunov (LEs), la dimensión Kaplan Yorke ( $D_{KY}$ ) y la entropía de Kolmogorov-Sinai (KSE). Los exponentes de Lyapunov brindan una medida global del grado de la convergencia o divergencia de dos trayectorias cercanas en el espacio de fases [6, 13, 14], donde el número de estos exponentes corresponde con la dimensión del sistema no lineal [5]. Por ejemplo, el sistema caótico de Lorenz es tridimensional (3D), por lo tanto, tiene tres exponentes de Lyapunov. Además, el conjunto de estos LEs, ordenado de mayor a menor ( $\lambda_1 \geq \lambda_2 \geq \cdots \geq \lambda_m$ ), se conoce como el espectro de Lyapunov [15]. En específico, si un sistema tiene al menos un exponente positivo de Lyapunov, se dice que tiene comportamiento caótico. Si tiene dos o más exponentes positivos, se dice que tiene un comportamiento hipercaótico [6]. Por otro lado, la estimación de la dimensión fractal del atractor, puede evaluarse por la dimensión Kaplan-Yorke, cuyo cálculo se basa en los exponentes de Lyapunov, tal y como se muestra en la ecuación (1.1) [15,16].

$$D_{KY} = j + \frac{\sum_{i=1}^{j} \lambda_i}{|\lambda_{j+1}|} \tag{1.1}$$

Por su parte, la entropía de Kolmogorov-Sinai es una medida de la divergencia de pequeños errores en una trayectoria caótica, dentro de un espacio de fases multidimensional. Su valor se

obtiene sumando los exponentes positivos de Lyapunov, como se describe en la referencia [15].

Encontrar los valores de los exponentes de Lyapunov de un sistema caótico es relevante, porque permite identificar los rangos de valores de los parámetros de un sistema, en el que exhibe un comportamiento caótico y forma un atractor extraño en el espacio de fases. Además, los valores de los exponentes de Lyapunov se pueden usar para calcular la dimensión Kaplan-Yorke y la entropía de Kolmogorov-Sinai. En la mayoría de los sistemas dinámicos no lineales, el cálculo de los LEs por medio de una solución analítica no es posible, ya que se requiere una solución analítica de las ecuaciones diferenciales ordinarias. Debido a esto, en muchos de los casos se emplean algoritmos numéricos para encontrarlos, como el método de Wolf [17]. Otra opción en el cálculo de los exponentes de Lyapunov consiste en utilizar el software de TISEAN, el cual proporciona los valores de los exponentes a partir de las series temporales del sistema caótico, solucionado por métodos numéricos [8].

## 1.3. Generadores de números aleatorios

En la actualidad, los avances tecnológicos han propiciado un aumento en el número de dispositivos electrónicos conectados a las redes inalámbricas. Cada año, una mayor cantidad de dispositivos inteligentes como televisores, sensores, cámaras, lavadoras, relojes, vehículos, entre otros, son conectados a internet. Algunos autores [18], estiman un total de 30 billones de dispositivos del Internet de las Cosas (IoT) conectados para 2027. Ante este panorama, es crucial garantizar la seguridad de la información durante su transmisión por las redes de comunicación. Por ello, los investigadores de diferentes campos trabajan en conjunto en el desarrollo de algoritmos criptográficos más rápidos, robustos y complejos que garanticen la privacidad, confidencialidad y autenticidad de los mensajes enviados y recibidos por los dispositivos electrónicos. Un concepto esencial que aparece en muchos de estos algoritmos criptográficos son los números aleatorios [19], los cuales son proporcionados por los generadores de números aleatorios (RNGs). El RNG es un algoritmo o un circuito capaz de crear una secuencia con números seleccionados al azar, dentro de un rango finito donde todos ellos tienen la misma probabilidad de aparecer. Aunque su aplicación más crítica es la rama de la criptografía, suelen verse en otras áreas, por ejemplo, para introducir aleatoriedad en los eventos de los juegos de video, elegir el ganador de una lotería, en simulaciones de procesos, entre otros [19].

La clasificación de los RNG comprende dos principales tipos: los generadores de números verdaderamente aleatorios (TRNG) y los generadores de números pseudoaleatorios (PRNG) [19–21].

Un TRNG es un sistema no determinista porque no tiene una regla o ecuación matemática que defina los valores futuros de la secuencia. Para lograr la verdadera aleatoriedad, los TRNGs emplean un componente de hardware físico, que realiza la lectura de algún fenómeno físico impredecible, como el ruido atmosférico, para generar los bits aleatorios. A tales dispositivos de hardware se les conoce como fuentes de entropía. Generalmente, los diseños de TRNGs están compuestos por el circuito que mide el fenómeno físico y un extractor de entropía, el cual es un algoritmo de postprocesamiento que genera los números aleatorios a partir de los datos de la fuente de entropía [19]. Debido al no determinismo, no es posible reproducir la misma secuencia. Es por ello que estos sistemas son esenciales en aplicaciones criptográficas. Sin embargo, en aplicaciones que requieren de alta rapidez de procesamiento, como en el cifrado de flujo, algunos TRNGs pueden no ser adecuados, ya que la lectura del fenómeno físico suele ser lenta [21].

Por su parte, el PRNG está asociado a un sistema determinista, ya que cuenta con una regla que define los valores futuros de la secuencia. Para iniciar el proceso de generación de números pseudoaleatorios, este tipo de sistemas requieren de valores iniciales conocidos como la semilla. Los PRNGs pueden ser implementados en software o con elementos de hardware. Al ser sistemas deterministas, la secuencia de números aleatorios es reproducible empleando la misma semilla. Sin embargo, no todo PRNG es útil en aplicaciones criptográficas; para ello, la secuencia de números debe cumplir o superar una serie de pruebas. Entre las pruebas estadísticas se encuentran las NIST y las TestU01, que miden las propiedades de aleatoriedad y uniformidad de la secuencia. Existen otras pruebas que miden la resistencia a la predicción y al retroceso [19], las cuales buscan asegurar que un atacante no pueda predecir valores pasados o futuros de la secuencia, a partir de un grupo de números observados, pero sin conocimiento de la semilla. Algunos autores emplean el concepto de PRNG criptográficamente seguro (CS-PRNG) para aquellos PRNG útiles en aplicaciones de criptografía [21]. Una ventaja de los PRNG es que los algoritmos o sistemas digitales presentan una alta rapidez de procesamiento.

También, es posible encontrar sistemas de RNGs que combinan un TRNG con un PRNG para formar un sistema híbrido, donde el TRNG actúa como el "sembrador" de las semillas para PRNG [20]. La tabla 1.2 muestra las características básicas de los tipos de generadores de números

aleatorios.

Tabla 1.2: Características básicas de los RNG [19].

| Tipo de RNG:              | TRNG.                      | PRNG.                  |

|---------------------------|----------------------------|------------------------|

| Tipo de sistema:          | No determinista            | Determinista           |

| Secuencia:                | Con verdadera aleatoriedad | Semejante a una de     |

|                           |                            | verdadera aleatoriedad |

| Componentes:              | Fuente de entropía         | Algoritmo diseñado en  |

|                           | Extractor de entropía      | software o hardware    |

| Rapidez de procesamiento: | Generalmente lenta         | Rápida                 |

| Para su funcionamiento:   | Miden un fenómeno físico   | Requieren una semilla  |

Las pruebas estadísticas, como las NIST y TESTU01, pueden aplicarse a cualquier tipo de RNG para verificar si las secuencias generadas superan las pruebas de aleatoriedad.

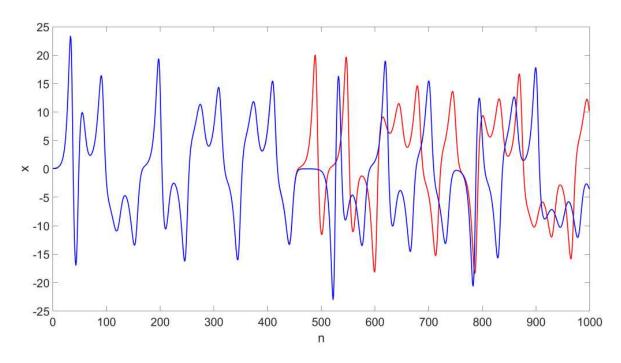

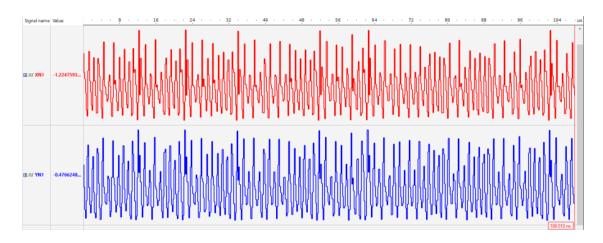

Como caso particular, los PRNG se pueden diseñar con una amplia variedad de algoritmos matemáticos, desde modelos tan simples como los lineales, hasta más complejos como los no lineales. Dentro de estos últimos, los basados en sistemas caóticos son una opción por tener en cuenta, ya que este tipo de PRNGs explotan la propiedad de la alta sensibilidad a las condiciones iniciales para generar secuencias muy diferentes entre sí, al variar ligeramente la semilla, la cual está formada por los valores de las condiciones iniciales de las variables de estado del sistema caótico [22,23]. Un ejemplo de sensibilidad a las condiciones iniciales se observa en la figura 1.1, en la cual se grafica la variable de estado x del sistema de Lorenz, cuando las ecuaciones diferenciales ordinarias se solucionan con dos condiciones iniciales muy cercanas, con una variación de una millonésima.

La serie temporal, como la que se muestra en la figura 1.1, puede procesarse para generar una secuencia binaria de números pseudoaleatorios. Tal secuencia binaria se obtiene a partir de la dinámica caótica de las variables de estado, y para ello se pueden utilizar las técnicas de umbral, módulo o del formato de punto fijo [24]. La aleatoriedad de la secuencia generada a partir de un sistema caótico, se evalúa aplicando pruebas estadísticas, como se muestra en el capítulo 3, en la página 47.

Figura 1.1: Evolución de la serie temporal de la variable de estado x del sistema de Lorenz, utilizando las condiciones iniciales  $x_0$ =0.1 (rojo) y  $x_0$ =0.100001 (azul).

De esta manera, si se acepta que los PRNGs basados en sistemas caóticos son adecuados para criptografía, entonces pueden aplicarse en la generación de llaves de algunos algoritmos de cifrado y autenticación de mensajes.

# 1.4. Cifrado y autenticación de mensajes

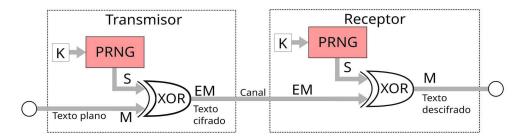

En la criptografía, los protocolos para comunicaciones seguras se diseñan tomando en cuenta ciertos aspectos claves, dos de estos son la confidencialidad e integridad del mensaje [25,26]. La confidencialidad busca evitar que un intruso (usuario no autorizado) sea capaz de leer un mensaje transmitido o almacenado. Para ello, los protocolos usan algoritmos de cifrado de información. El cifrado consiste en transformar un mensaje legible, llamado texto plano (texto, imágenes, archivos), en un mensaje no legible, denominado texto cifrado, utilizando un algoritmo y una llave antes de su transmisión [26,27]. Existen algoritmos que emplean la misma llave para cifrar y descifrar la información, conocidos como algoritmos de clave simétrica [25]. Estos sistemas pueden llevar a cabo el cifrado utilizando un bloque de n bits (cifrado en bloques) o realizando el proceso bit a bit o byte a byte (cifrado de flujo) [28]. En el caso de los esquemas de cifrado/descifrado de flujo, el

funcionamiento general es el siguiente: un PRNG genera un flujo de números pseudoaleatorios, denominado flujo de llaves, que se combinan byte a byte con el texto plano mediante la operación XOR, y produce el texto cifrado que luego se transmite por un canal de comunicación. Para el proceso de descifrado, se ejecuta nuevamente la operación XOR, pero ahora entre el texto cifrado y el mismo flujo de llaves, para recuperar el texto plano original [25, 26]. En este tipo de sistemas de cifrado, o incluso en otros más complejos, los PRNG basados en caos pueden ser aplicados para proporcionar el flujo de llaves para el algoritmo.

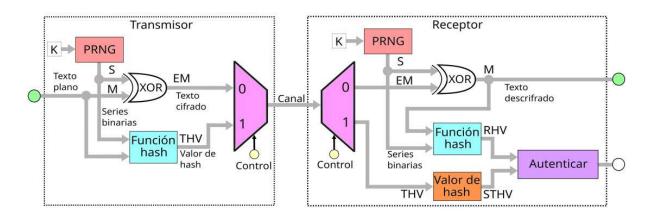

La integridad busca asegurar que el mensaje recibido sea idéntico al enviado y no haya sufrido alteraciones durante su transmisión [25,26]. Para lograrlo, en esta tesis se propone el uso de funciones de hash unidireccionales, conocidas también como resúmenes de mensaje. Las funciones de hash consisten en algoritmos matemáticos que transforman un bloque de texto plano en un conjunto de caracteres alfanuméricos de longitud fija, denominados valor de hash, que representa una etiqueta de autenticación para el mensaje enviado [26]. Algunas características de estas funciones de hash son [26]:

- 1. Admiten datos de entrada de cualquier longitud.

- 2. Producen una salida de longitud fija.

- 3. Son unidireccionales, es decir, dado un valor de hash, es prácticamente imposible recuperar el texto plano original.

- 4. Ofrecen resistencia a la colisión, lo que significa que dos textos planos diferentes no deberían producir el mismo valor de hash.

- 5. Un cambio de un solo bit en la entrada genera una salida completamente distinta.

En un sistema de comunicación emisor/receptor que utiliza el resumen de mensaje, el funcionamiento general es el siguiente: primero, el emisor calcula el valor de hash del texto plano y lo envía al receptor junto con el texto cifrado. Luego, el receptor aplica la misma función de hash con el texto plano obtenido por el procedimiento de descifrado. Al final, se comparan ambos valores de hash, y si son diferentes, esto indica que un intruso ha modificado al menos un bit del mensaje. Por lo tanto, la función de hash funciona como un tipo de firma que permite determinar si un mensaje es auténtico [29].

En la literatura, existen varios tipos de funciones de hash muy utilizadas, por ejemplo, SHA-1, SHA-2. Además, se han propuesto funciones de hash unidireccionales que utilizan números pseudoaleatorios para generar las etiquetas de autenticación, por ejemplo, el método del producto pseudo punto [30], donde los PRNG basados en caos pueden encontrar aplicación.

# 1.5. Acerca de la FPGA y la Raspberry Pi 3

La implementación de sistemas caóticos puede llevarse a cabo empleando recursos de hardware analógico o digital. En el caso particular de un entorno digital, dispositivos como la FPGA y el sistema embebido Raspberry Pi 3 son opciones adecuadas, debido a que ofrecen diversas características y funcionalidades útiles para esta tarea. La FPGA es un dispositivo reconfigurable basado en matrices de bloques lógicos configurables, cuya interconexión se define mediante un lenguaje de descripción de hardware (HDL), como Verilog. Entre sus principales ventajas están el rápido prototipado, la reconfigurabilidad de los diseños, el bajo consumo de recursos y la capacidad de ejecutar múltiples operaciones en paralelo, con el fin de lograr mayores velocidades de procesamiento. El desarrollo de una arquitectura digital en FPGA se basa en la conexión de circuitos digitales combinacionales y secuenciales, desde simples compuertas lógicas hasta circuitos más complejos como contadores, registros de desplazamiento, máquinas de estados, entre muchos otros. La lógica de cada circuito y las conexiones entre estos se describen mediante el lenguaje HDL y se sintetizan en configuraciones específicas dentro de los bloques lógicos configurables, empleando celdas lógicas (o elementos lógicos) que cuentan con: LUTs (Look-Up Tables), flip-flops, registros y multiplexores. Además, los dispositivos FPGA suelen proporcionar otros componentes de hardware digital, como multiplicadores embebidos, bloques de memoria RAM, bucles de amarre de fase (PLL) y otros núcleos de propiedad intelectual [31], para el diseño de sistemas de mayor complejidad.

Por otro lado, el sistema empotrado Raspberry Pi 3 es una computadora de placa única para aplicaciones de propósito general. Este dispositivo es útil en aplicaciones para el Internet de las Cosas, porque tiene la ventaja de contar con una amplia variedad de bibliotecas de programación para manejar protocolos de mensajería como el transporte de telemetría de colas de mensajes (MQTT), y conectividad a Internet. El dispositivo funciona con un sistema operativo basado en Linux y permite programar aplicaciones en lenguajes de alto nivel, como C, Python o Java. Algunas

características del dispositivo son: un procesador de 64 bit ARM Cortex-A53 a 1.2 GHz, 1 GB de memoria RAM y diferentes puertos de entrada y salida de datos [32].

En ambos dispositivos digitales se pueden implementar PRNGs basados en caos para desarrollar sistemas de cifrado y autenticación de mensajes.

# 1.6. Hipótesis

La implementación de sistemas caóticos con múltiples variables de estado puede mejorar el throughput de un generador de números pseudoaleatorios y aumentar la longitud de las etiquetas de autenticación producidas por una función de hash basada en números pseudoaleatorios.

# 1.7. Objetivos

# 1.7.1. Objetivo general

Diseñar un sistema de autenticación de datos utilizando generadores de números pseudoaleatorios basados en sistemas caóticos de distintas dimensiones, los cuales servirán para aumentar la longitud de las etiquetas de autenticación de una función de hash.

# 1.7.2. Objetivos específicos

- Diseñar generadores de números pseudoaleatorios basados en sistemas caóticos de dos, tres y cuatro dimensiones.

- Garantizar la aleatoriedad de las secuencias generadas por los generadores de números pseudoaleatorios mediante pruebas estadísticas NIST.

- Implementar en FPGA y Raspberry Pi los tres PRNGs basados en sistemas caóticos 2D,

3D y 4D.

- Describir en un lenguaje de hardware y sintetizar en una FPGA un sistema de cifrado y autenticación empleando una función de hash, basada en generadores de números pseudoaleatorios.

- Implementar en Raspberry Pi un sistema de cifrado y autenticación usando la función de hash y empleando el protocolo MQTT para la transmisión de datos.

- Autenticar imágenes a escala de grises, RGB y texto.

# 1.8. Organización de la tesis

Esta tesis está organizada en 6 capítulos. El capítulo 1, describe de forma general el objetivo de esta investigación. En el capítulo 2, se analizan las características de tres sistemas caóticos: un mapa en dos dimensiones (2D), y dos sistemas caóticos en tiempo continuo en 3D y 4D, cuya solución numérica emplea el método de Euler hacia adelante. Además, se presentan las series temporales y los atractores de cada sistema caótico. En el capítulo 3, se describe el diseño a bloques de un sistema caótico y su descripción en Verilog para su síntesis en un dispositivo FPGA. Se explican las técnicas para la generación de las secuencias pseudoaleatorias a partir de los sistemas caóticos y se muestran los resultados de las pruebas estadísticas NIST para cada PRNG. El capítulo 4, detalla los algoritmos para cifrar y autenticar imágenes y texto. El algoritmo de cifrado emplea la operación XOR, mientras que el de autenticación utiliza una función de hash, basada en el producto pseudo punto. Además, se describe la implementación de un sistema de comunicación segura que incluye las etapas de cifrado y autenticación de mensajes. De manera similar, el capítulo 5, aborda la implementación en Raspberry Pi 3 de los PRNGs y el esquema de comunicación segura, que incluye el protocolo MQTT para la transmisión y recepción de datos entre dos dispositivos Raspberry Pi. Por último, el capítulo 6 muestra las conclusiones y trabajos a futuro.

# Capítulo 2

# Sistemas caóticos

En este capítulo se describen tres sistemas caóticos con atractores autoexitados y dimensiones que abarcan 2D, 3D, y 4D. El primer caso de estudio es un mapa caótico 2D capaz de proporcionar cuatro diferentes comportamientos caóticos distintos, dependiendo de los valores seleccionados en los parámetros de las ecuaciones discretas. El segundo objeto de estudio aborda un sistema caótico 3D basado en un modelo de memristor, que bajo ciertos parámetros exhibe un comportamiento caótico y muestra multiestabilidad. Por último, el tercer caso de estudio presenta un sistema 4D de tiempo continuo, capaz de producir un comportamiento caótico y multiestabilidad, entre otras propiedades. Además, se proporcionan simulaciones de series temporales, los atractores obtenidos en el espacio de fases y otras características clave, como los puntos de equilibrio, valores propios y exponentes de Lyapunov. Cabe destacar que la solución de los sistemas de tiempo continuo emplea el método numérico de Euler hacia adelante, elegido por su simplicidad y bajo número de operaciones computacionales.

# 2.1. Descripción de los sistemas caóticos

# 2.1.1. Mapas caóticos

Los mapas caóticos son modelos matemáticos compuestos por una o varias ecuaciones discretas que exhiben un comportamiento caótico. Típicamente, se definen por una regla recursiva de la forma  $x_{n+1} = f(x_n)$ , donde  $f(x_n)$  es una función que determina el valor siguiente  $(x_{n+1})$  a partir del actual  $(x_n)$  [33]. Por ejemplo, un mapa caótico, ampliamente estudiado, es el mapa

logístico de una dimensión. Este mapa 1D, demuestra que el comportamiento caótico se origina con una simple función discreta no lineal, la cual se muestra en la ecuación (2.1).

$$x_{n+1} = rx_n(1 - x_n) (2.1)$$

Los mapas generan nuevos valores en cada iteración (n+1), cuyas operaciones iterativas pueden ser sintetizadas en hardware digital. Debido a la alta sensibilidad a las condiciones iniciales, variar una millonésima dos de estas, provoca que las series temporales diverjan significativamente, produciendo diferentes trayectorias al evolucionar en tiempo, tal como sucede con los sistemas de tiempo continuo, cuyo ejemplo se observa en la figura 1.1. Una técnica común que ayuda a encontrar los rangos de los parámetros donde se genera comportamiento caótico en un mapa o sistema dinámico, son los diagramas de bifurcación, los cuales permiten visualizar cómo la variación de un parámetro puede propiciar comportamientos caóticos o converger a valores específicos.

En la literatura, existe una gran variedad de mapas caóticos con distintas funciones no lineales y de diferentes dimensiones. Muchos de estos se han aplicado en la generación de números pseudoaleatorios y en esquemas de comunicaciones seguras para el cifrado de datos. Por ejemplo, entre los mapas unidimensionales más comunes se encuentran el de corrimiento de Bernoulli, el mapa tienda de campaña y el Zigzag. En el caso de mapas bidimensionales, destacan los mapas de Henon, Arnold 2D y el Baker, entre otros [34]. Hoy en día, muchos investigadores continúan desarrollando nuevos modelos novedosos de mapas caóticos en 3D, 4D, 5D, etc., con mejores propiedades de aleatoriedad en las secuencias binarias y con mayores exponentes positivos de Lyapunov.

En la siguiente subsección se detallan algunas propiedades de un mapa caótico bidimensional, que es un caso de estudio en esta tesis para el desarrollo de un PRNG.

# 2.1.2. Mapa caótico 2D de Sprott

El mapa caótico 2D, propuesto por Sprott en [35], está definido por dos variables de estado, designadas como  $x_n$  y  $y_n$ . Las expresiones matemáticas que describen la dinámica de este mapa se presentan en la ecuación (2.2). En ellas, se observa que los valores de las variables de estado en la siguiente iteración (n+1) se calculan mediante operaciones de adición y multiplicación,

utilizando los valores actuales de las variables de estado y un conjunto de parámetros constantes, denotados como  $a_i$ .

$$x_{n+1} = a_1 + a_2 x_n + a_3 x_n^2 + a_4 x_n y_n + a_5 y_n + a_6 y_n^2$$

$$y_{n+1} = a_7 + a_8 x_n + a_9 x_n^2 + a_{10} x_n y_n + a_{11} y_n + a_{12} y_n^2$$

(2.2)

Este mapa caótico puede exhibir diversas dinámicas en función de los valores seleccionados para los coeficientes  $a_i$ . Por ello, en el trabajo [30], se proporcionan un conjunto de coeficientes que dan lugar a cuatro atractores distintos en el espacio de fases. Estos valores se resumen en la tabla 2.1.

Tabla 2.1: Coeficientes  $a_i$  para diversas dinámicas caóticas con el mapa caótico 2D.

| Мара |       | Valores de los coeficientes |       |       |       |       |       |       |       |          |          |          |

|------|-------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|----------|----------|----------|

|      | $a_1$ | $a_2$                       | $a_3$ | $a_4$ | $a_5$ | $a_6$ | $a_7$ | $a_8$ | $a_9$ | $a_{10}$ | $a_{11}$ | $a_{12}$ |

| 1    | -0.6  | -0.1                        | 1.1   | 0.2   | -0.8  | 0.6   | -0.7  | 0.7   | 0.7   | 0.3      | 0.6      | 0.9      |

| 2    | -1.0  | 0.9                         | 0.4   | -0.2  | -0.6  | -0.5  | 0.4   | 0.7   | 0.3   | -0.5     | 0.7      | -0.8     |

| 3    | 0.8   | 1.0                         | -1.2  | -1.0  | 1.1   | -0.9  | 0.4   | -0.4  | -0.6  | -0.2     | -0.5     | -0.7     |

| 4    | -0.6  | -0.4                        | -0.4  | -0.8  | 0.7   | 0.3   | -0.4  | 0.4   | 0.5   | 0.5      | 0.8      | -0.1     |

### 2.1.2.1. Simulación de las series temporales y atractores

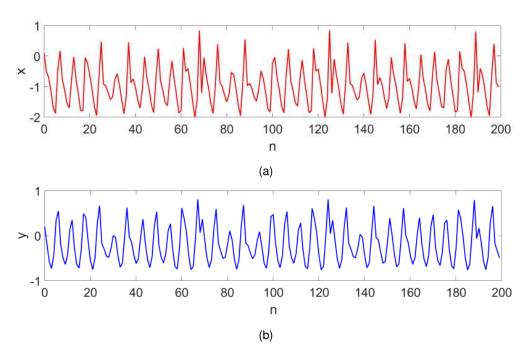

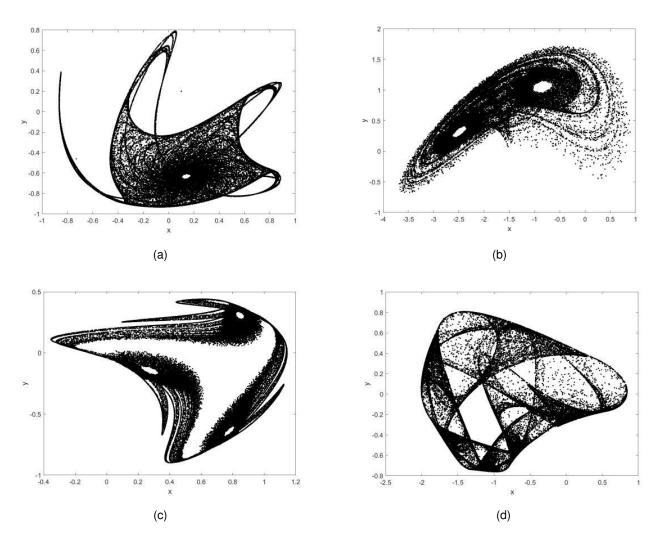

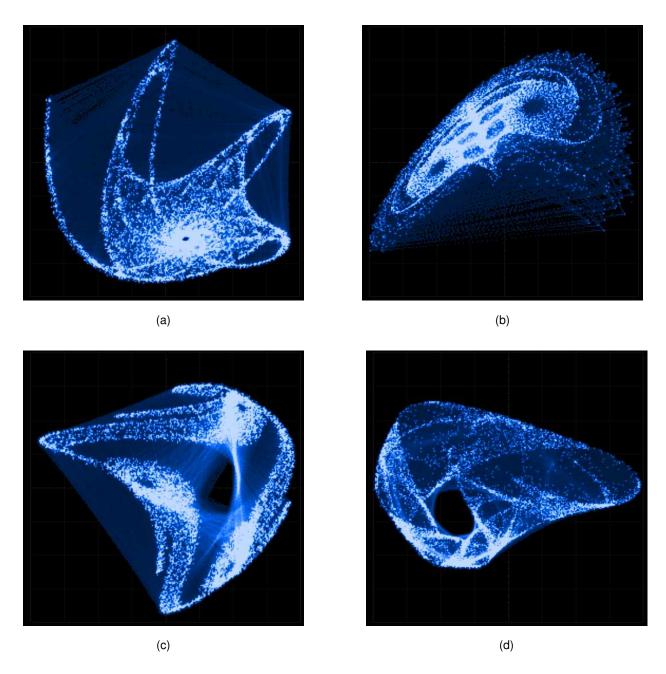

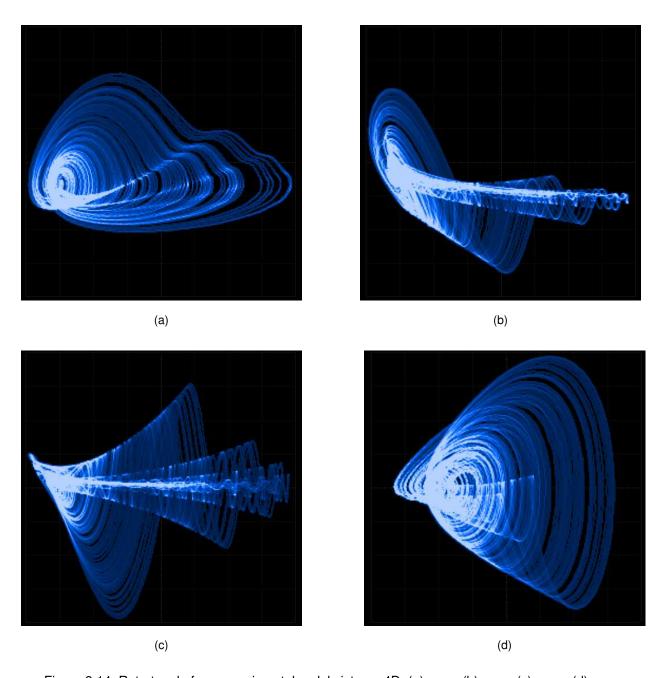

Dado que los mapas caóticos están basados en ecuaciones de diferencias discretas, son fáciles y rápidos de implementar en entornos digitales. Estas ecuaciones se pueden programar y simular utilizando lenguajes de alto nivel, como Python, C++, Java, entre otros. En el caso del mapa 2D de Sprott, en esta tesis la simulación se llevó a cabo en el software de MATLAB® empleando aritmética de punto flotante. Para simular las series temporales, se utilizaron las condiciones iniciales  $x_0=0.1$  y  $y_0=0.2$ . Como ejemplo, la figura 2.1 ilustra las series temporales simuladas con el conjunto de coeficientes  $a_i$  que forman el mapa 4 (ver tabla 2.1). En dicha simulación numérica se realizaron 200 iteraciones. De manera similar, la figura 2.2 ilustra los cuatro atractores distintos en el espacio de fases, formados utilizando el grupo de coeficientes  $a_i$  de la tabla 2.1. Todos los atractores caóticos se graficaron en el espacio de fases, realizando 50000 iteraciones en cada simulación.

Figura 2.1: Series temporales del mapa 2D para las variables de estado a)  $x_n$ , b)  $y_n$ , con los coeficientes  $a_i$  del mapa 4 mostrados en la tabla 2.1.

## 2.1.2.2. Exponentes de Lyapunov y dimensión fractal

En el caso de los exponentes de Lyapunov y la dimensión fractal, la tabla 2.2 (tomada de [35]) agrupa los resultados. En ella se observa que, aunque el mapa 4 muestra la mayor sensibilidad a las condiciones iniciales debido a su mayor exponente positivo de Lyapunov, presenta el atractor menos complejo en términos de la dimensión fractal. Por otro lado, el mapa 1, tiene la menor sensibilidad a las condiciones iniciales, pero muestra el atractor más complejo en la dimensión fractal.

Tabla 2.2: Exponentes de Lyapunov y la dimensión fractal para los diferentes conjuntos de coeficientes  $a_i$  del mapa.

| Мара | Exponente positivo de Lyapunov | Dimensión Fractal |

|------|--------------------------------|-------------------|

| 1    | 0.12                           | 1.77              |

| 2    | 0.14                           | 1.79              |

| 3    | 0.15                           | 1.69              |

| 4    | 0.16                           | 1.50              |

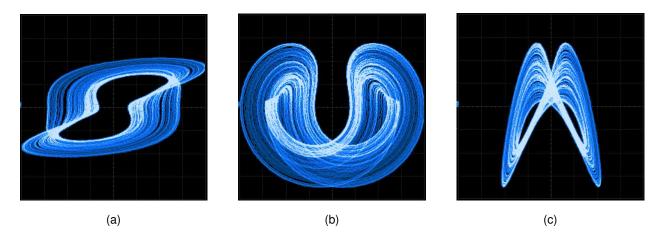

Figura 2.2: Retratos de fase  $x_n - y_n$  con los diferentes conjuntos de coeficientes  $a_i$  de la tabla 2.1: (a) mapa 1, (b) mapa 2, (c) mapa 3, (d) mapa 4.

# 2.1.3. Sistemas caóticos en tiempo continuo

Los sistemas caóticos de tiempo continuo se modelan por ecuaciones diferenciales ordinarias de orden entero o fraccionario. A diferencia de los mapas caóticos, estos modelos matemáticos requieren métodos numéricos para ser resueltos e implementados en entornos digitales. En la literatura, un sistema caótico de orden entero muy popular y estudiado es el sistema de Lorenz, publicado en 1963 en [36], cuyas tres ecuaciones diferenciales ordinarias se muestran en la ecuación (2.3).

$$\dot{x} = \sigma(y - x)$$

$$\dot{y} = \rho x - xz - y$$

$$\dot{z} = xy - \beta z$$

(2.3)

Como puede observarse, el sistema de Lorenz de orden entero está formado por operaciones de resta y multiplicación, donde la no linealidad se introduce a través de los productos de las variables de estado xz y xy. Además, en sus ecuaciones se pueden observar los parámetros con valores constantes  $\sigma$ ,  $\rho$  y  $\beta$ . Estos parámetros son esenciales, ya que una elección apropiada de sus valores puede dar lugar a series temporales con mejor comportamiento caótico. Una región caótica muy estudiada se encuentra con los parámetros establecidos en los valores 10, 28 y 8/3, respectivamente.

Hoy en día, existe una extensa investigación para desarrollar nuevos sistemas caóticos en tiempo continuo, con diferentes dimensiones, como 3D, 4D, 5D, etc. Incluso, algunos de ellos están basados en modelos neuronales y de memristores. Las siguientes subsecciones detallan dos sistemas caóticos en tiempo continuo 3D y 4D, que son útiles en el desarrollo de PRNGs.

### 2.1.4. Sistema caótico 3D basado en un memristor

El memristor es considerado el cuarto componente eléctrico fundamental, cuyas bases teóricas fueron establecidas por León O. Chua en 1971 [37]. Debido a las dificultades en el desarrollo físico del componente, muchos investigadores han optado por crear emuladores del memristor, los cuales pueden ser implementados en sistemas de hardware analógico y digital. Asignando los valores apropiados a los parámetros, los sistemas dinámicos basados en memristores tienen la capacidad de exhibir el comportamiento caótico. Un ejemplo de ello es el sistema caótico memristivo de tres variables de estado introducido en [38], que también presenta la propiedad de multiestabilidad, la cual se refiere a la coexistencia de múltiples atractores en un sistema con los mismos parámetros fijos, pero con diferentes condiciones iniciales [39]. El modelo matemático de este sistema es presentado en la ecuación (2.4).

$$\dot{x} = ayz,$$

$$\dot{y} = x - y$$

$$\dot{z} = k - b(\gamma xy - \delta xy^{3})$$

(2.4)

La dinámica caótica de este sistema y la propiedad de multiestabilidad aparecen con los parámetros establecidos como:  $a=3.5,\,k=1.2,\,b=1.8,\,\gamma=2,\,\delta=0.1.$

# 2.1.4.1. Puntos de equilibrio y valores propios

En el análisis de estabilidad, los valores propios o eigenvalores del sistema se obtienen a partir de la matriz jacobiana [38], como se muestra en la ecuación (2.5). El sistema cuenta con cuatro puntos de equilibrio y sus correspondientes valores propios se presentan en la tabla 2.3.

$$J(x^{\star}, y^{\star}, z^{\star}) = \begin{pmatrix} 0 & az^{\star} & ay^{\star} \\ 1 & -1 & 0 \\ -b(\gamma y^{\star} - \delta y^{\star 3}) & -b(\gamma x^{\star} - 3\delta x^{\star} y^{\star 2}) & 0 \end{pmatrix}$$

(2.5)

Tabla 2.3: Puntos de equilibrio y sus correspondientes valores propios.

| Puntos de equilibrio | Valores propios                 |

|----------------------|---------------------------------|

| (0.58, 0.58, 0)      | (1.01, 0, -2.01)                |

| (-0.58, -0.58, 0)    | (0, -0.5 + 1.34i, -0.5 - 1.34i) |

| (4.43, 4.43, 0)      | (3.47, 0, -4.47)                |

| (-4.43, -4.43, 0)    | (0, -0.5 + 3.90i, -0.5 - 3.90i) |

### 2.1.4.2. Simulación de las series temporales y atractores

Para solucionar y obtener las series temporales y los atractores de este sistema de tiempo continuo, se requiere aplicar un método numérico. Después de seleccionar el método de Euler hacia adelante y emplearlo en las ecuaciones diferenciales ordinarias dadas en la ecuación (2.4), se obtiene el sistema de ecuaciones discretas mostrado en la ecuación (2.6).

$$x_{n+1} = x_n + h(ay_n z_n),$$

$$y_{n+1} = y_n + h(x_n - y_n),$$

$$z_{n+1} = z_n + h(k - b\gamma x_n y_n - b\delta x_n y_n^3),$$

(2.6)

El sistema de ecuaciones anterior puede ser implementado haciendo uso de elementos de hardware digital. Para obtener la respuesta caótica, se estableció un ancho de paso h de 0.01025, mientras que las condiciones iniciales se fijaron en  $x_0=0.2,\,y_0=0.1$  y  $z_0=0$ .

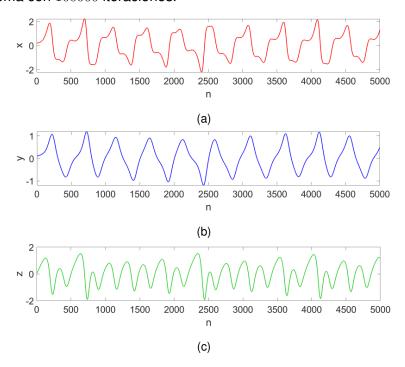

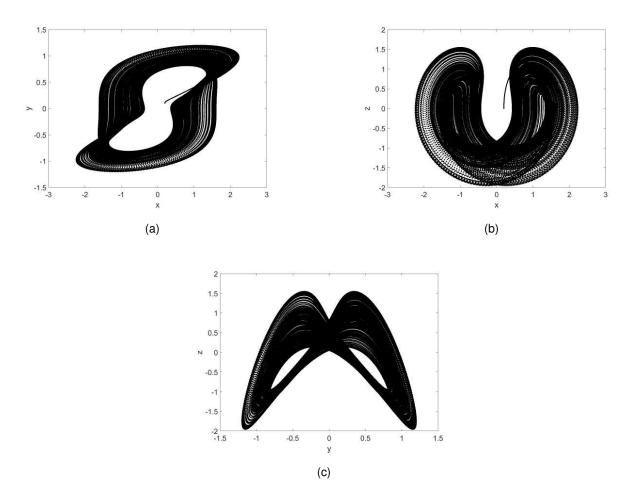

La figura 2.3 muestra las series temporales de las tres variables de estado, efectuando una simulación de 5000 iteraciones. De manera similar, la figura 2.4 ilustra los atractores resultantes al simular el sistema con 100000 iteraciones.

Figura 2.3: Series temporales del sistema 3D para las variables de estado: a)  $x_n$ , b)  $y_n$ , c) $z_n$ , con parámetros establecidos como:  $h=0.01025,~a=3.5,~k=1.2,~b=1.8,~\gamma=2$  y  $\delta=0.1.$

### 2.1.4.3. Exponentes de Lyapunov y dimensión Kaplan-Yorke

En la tabla 2.4, se muestran los exponentes de Lyapunov y la dimensión Kaplan-Yorke obtenidos para el sistema 3D basado en un memristor.

Figura 2.4: Retratos de fase del sistema 3D: (a) x-y, (b) x-z, (c) y-z.

Tabla 2.4: Exponentes de Lyapunov y la dimensión Kaplan-Yorke para el sistema 3D.

| Exponentes de Lyapunov | Dimensión Kaplan-Yorke |

|------------------------|------------------------|

| $LE_1 = 0.22$          |                        |

| $LE_2 = 0$             | 2.1864                 |

| $LE_3 = -1.18$         |                        |

# 2.1.5. Sistema caótico 4D

Este sistema caótico, propuesto por Sambas et al. en [40], está conformado por cuatro ecuaciones diferenciales ordinarias, por lo cual se clasifica como un sistema "hyperjerk". El modelo

matemático contiene ocho términos, en los cuales aparece una función de valor absoluto y dos parámetros constantes positivos, a y b. Además, este sistema cuenta con multiestabilidad y exhibe un comportamiento antimonotónico. Las ecuaciones que describen a este sistema se muestran en la ecuación (2.7).

$$\begin{cases} \dot{x}=y,\\ \dot{y}=z,\\ \dot{z}=w,\\ \dot{w}=-x-|x|-ay-bw-xz, \end{cases} \tag{2.7}$$

para este sistema surge cuando los parámetros se fijan en:  $a=4$  y

El comportamiento caótico para este sistema surge cuando los parámetros se fijan en: a=4 y b=2. La no linealidad de este sistema se introduce por el producto xz y la función valor absoluto |x|.

### 2.1.5.1. Puntos de equilibrio

Los puntos de equilibrio se obtienen al resolver el sistema estableciendo todas las variables de estado en cero en la ecuación (2.7). Al llevar a cabo el análisis, el conjunto de puntos de equilibrio S se simplifica como:  $S = \{(x, y, z, w) | x \le 0, y = 0, z = 0, w = 0\}$ , que corresponde a una semirrecta sobre el eje x negativo en  $\mathbf{R}^4$  [40].

### 2.1.5.2. Simulación de las series temporales y atractores

Al aplicar el método de Euler hacia adelante al modelo matemático mostrado en la ecuación (2.7), se obtiene el conjunto de expresiones matemáticas discretas presentadas en la ecuación (2.8), las cuales están listas para ser programadas en un lenguaje de alto nivel.

$$x_{n+1} = x_n + h(y_n)$$

$$y_{n+1} = y_n + h(z_n)$$

$$z_{n+1} = z_n + h(w_n)$$

$$w_{n+1} = w_n + h(-x_n - |x_n| - ay_n - bw_n - x_n z_n)$$

(2.8)

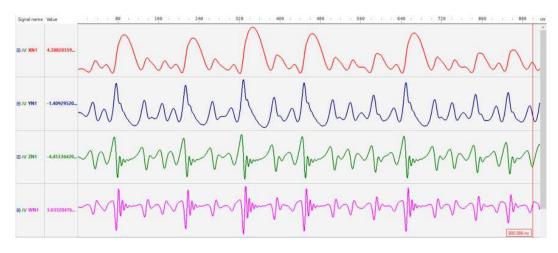

Las series temporales se obtuvieron considerando un ancho de paso h=0.02, y estableciendo las cuatro condiciones iniciales en 0.2.

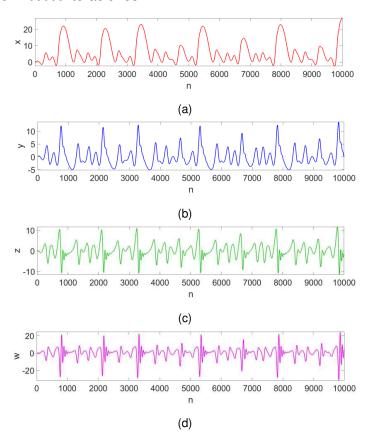

La figura 2.5 muestra las series temporales de las cuatro variables de estado, al realizar una simulación con 10000 iteraciones. Por otro lado, la figura 2.6 muestra cuatro retratos de fase al simular el sistema con 100000 iteraciones.

Figura 2.5: Series temporales del sistema 4D para las variables de estado: a)  $x_n$ , b)  $y_n$ , c) $z_n$ , d) $w_n$ , con los parámetros establecidos como:  $h=0.02,\ a=4$  y b=2.

# 2.1.5.3. Exponentes de Lyapunov y dimensión Kaplan-Yorke

Para obtener los exponentes de Lyapunov y la dimensión Kaplan-Yorke  $D_{KY}$  del sistema 4D, se utilizó la aproximación de Wolf [40]. La tabla 2.5 muestra los resultados.

Figura 2.6: Retratos de fase del sistema 4D: (a) x-y, (b) x-z, (c) x-w, (d) y-z.

Tabla 2.5: Exponentes de Lyapunov y la dimensión Kaplan-Yorke para el sistema 4D.

| Exponentes de Lyapunov | Dimensión Kaplan-Yorke |

|------------------------|------------------------|

| $LE_1 = 0.1214$        |                        |

| $LE_2 = 0$             | 2.1665                 |

| $LE_3 = -0.7292$       | 2.1003                 |

| $LE_4 = -1.3924$       |                        |

# Capítulo 3

# Descripción y síntesis de sistemas caóticos y PRNGs en FPGAs

Las ecuaciones matemáticas discretas que gobiernan el comportamiento de un sistema dinámico caótico pueden encontrar aplicaciones prácticas en la generación de números pseudoaleatorios y en esquemas criptográficos al implementarse en entornos digitales, que abarcan computadoras, sistemas embebidos, microcontroladores y FPGAs. Por ello, este capítulo se centra en la descripción mediante bloques digitales de los tres sistemas caóticos descritos en el capítulo anterior, empleando el lenguaje de descripción de hardware de Verilog. Además, se presentan simulaciones de las series temporales producidas por cada sistema, su síntesis en una FPGA de Intel/Altera, los atractores experimentales obtenidos, el uso de los sistemas como PRNGs y los resultados de las pruebas estadísticas NIST de los bits pseudoaleatorios de cada sistema. La descripción de las ecuaciones mediante un lenguaje de hardware, se lleva a cabo considerando la conexión de múltiples bloques digitales combinacionales y secuenciales, que incluyen elementos lógicos y aritméticos. Estos bloques, al conectarse, forman una arquitectura digital más compleja que finalmente se sintetiza en una FPGA por medio de los conocidos bloques lógicos configurables que conforman a este dispositivo. La FPGA destaca por su capacidad de procesamiento en paralelo, que permite la ejecución de múltiples procedimientos o tareas en un mismo ciclo de reloj, favoreciendo a un incremento en la velocidad de procesamiento del sistema. Este dispositivo también permite verificar si un diseño basado en bloques digitales funciona correctamente, cuando todos los elementos de hardware trabajan en conjunto.

Cabe mencionar que cada descripción y simulación se realizó en el software de Active-HDL 15, mientras que la síntesis para FPGA se efectuó en el software de Quartus-II.

# 3.1. Cuestiones sobre la aritmética de computadora

Los sistemas caóticos descritos con ecuaciones discretas, ya sean mapas o sistemas en tiempo continuo discretizados mediante un método numérico, generalmente suelen estar expresados por operaciones aritméticas simples que trabajan con cantidades con punto decimal. Estas operaciones se pueden implementar y sintetizar en FPGA utilizando bloques digitales tales como, sumadores, restadores y multiplicadores. No obstante, es necesario seleccionar una aritmética de computadora adecuada para la ejecución de estas operaciones en los bloques digitales. Las aritméticas disponibles son la de punto flotante y la de punto fijo. La aritmética de punto flotante ofrece una mayor precisión y un rango más amplio para expresar números grandes o pequeños. Sin embargo, los algoritmos para su implementación suelen ser complejos de realizar. Por otro lado, la aritmética de punto fijo es más sencilla y rápida de implementar [41], ya que solo requiere repartir el número total de bits de la aritmética en tres partes: un bit de signo para indicar si el número es positivo o negativo, un conjunto de bits para la parte entera y otro para la parte fraccionaria. La precisión decimal depende de la cantidad de bits asignados a la parte fraccionaria, la cual mejora al aumentar la cantidad de ellos. No obstante, su desventaja es que el rango de operación está limitado al número de bits asignados a la parte entera del formato.

Por lo anterior, cuando se realizan descripciones de sistemas caóticos en Verilog o cualquier otro lenguaje de descripción de hardware, es fundamental llevar a cabo un análisis previo para estimar el rango de operación, es decir, determinar los valores máximos y mínimos que alcanzan las variables de estado y las operaciones intermedias de cada sistema dinámico [31], con el fin de evitar desbordamientos en los bloques aritméticos. Este análisis puede llevarse a cabo en un lenguaje de alto nivel.

En la literatura, los sistemas caóticos implementados en FPGA con aritmética de punto fijo suelen utilizar 16, 24, 32, 40 e incluso 64 bits. Aunque un mayor número de bits mejora significativamente la precisión decimal, también incrementa el consumo de recursos, ya que los bloques aritméticos deben trabajar con más bits. No obstante, dado que estos sistemas caóticos se utilizan para el desarrollo de PRNGs, es preferible emplear una aritmética con muchos bits y así

contar con un mayor número de condiciones iniciales o semillas para el PRNG. Por ello, los tres sistemas caóticos descritos en el capítulo anterior, se diseñan utilizando aritmética de punto fijo de 64 bits, donde cada uno de los sistemas tiene su propia distribución de bits para el formato.

# 3.2. Descripciones de sistemas caóticos

El lenguaje de Verilog permite la descripción de circuitos digitales combinacionales y secuenciales, como multiplexores, decodificadores, sumadores, multiplicadores, registros, contadores, entre otros, a un alto nivel de abstracción. Esto significa que Verilog describe el comportamiento de un bloque digital junto con sus puertos de entrada y salida de datos, y los pines de control, sin proporcionar detalles a un nivel más bajo, como el diseño basado en transistores. Cada bloque puede visualizarse como una caja negra, donde se conocen sus puertos y su comportamiento, pero no sus elementos internos. Además, Verilog permite crear arquitecturas digitales de forma jerárquica, en las cuales un bloque digital de mayor jerarquía se compone mediante la conexión interna de múltiples bloques simples [42]. Estas estructuras jerárquicas son posibles gracias a la instanciación de bloques, que consiste en la creación de copias de un bloque definido previamente. De esta manera, un bloque puede repetirse las veces que sea necesario dentro de otro bloque de mayor jerarquía.

En las siguientes subsecciones se presenta la descripción de los tres sistemas caóticos mediante diagramas de bloques, los cuales aprovechan el diseño jerárquico de Verilog. Primero se describe el sistema 3D, dado que es sencillo de implementar en 64 bits.

# 3.2.1. Descripción del sistema 3D basado en un memristor

### 3.2.1.1. Análisis de amplitudes para el formato de punto fijo

El análisis de amplitudes máximas y mínimas de las variables de estado es esencial para determinar el rango de valores en los cuales el sistema está acotado, y con ello definir de forma adecuada una distribución del formato de punto fijo para la parte entera y fraccionaria. Aunque el análisis se puede realizar considerando condiciones iniciales fijas, esto no garantiza que otros valores de ellas produzcan series temporales con amplitudes dentro del rango establecido. Por dicha razón, lo mejor es ejecutar múltiples pruebas con diferentes conjuntos de condiciones iniciales.

El sistema 3D se simuló en un lenguaje de alto nivel, utilizando los parámetros especificados en el capítulo 2 y considerando condiciones iniciales dentro del rango observado en los retratos de fase de la figura 2.4. En cada simulación de 100000 iteraciones, se despreciaron las primeras 20000, para eliminar el tiempo transitorio y obtener series temporales diferentes. Los rangos aproximados obtenidos para cada variable fueron:  $x \in [-2.2, 2.2], y \in [-1.2, 1.2]$  y  $z \in [-1.9, 1.5]$ . Dichos resultados coinciden con las amplitudes observadas en las gráficas de los atractores. A partir de estos rangos, se pueden definir posibles condiciones iniciales para el sistema y determinar las amplitudes de los productos intermedios en las ecuaciones, los cuales, sin considerar el transitorio, están dentro del rango  $\pm$  15. Por lo cual, 4 bits de parte entera en el formato de punto fijo serían suficientes. Sin embargo, también es necesario tomar en cuenta el comportamiento de las series caóticas durante el tiempo transitorio, ya que con ciertas condiciones iniciales podrían presentarse amplitudes mayores. Por ejemplo, en este sistema, al establecer condiciones iniciales muy pequeñas como:  $x_0 = 1 \times 10^{-8}$   $y_0 = -1 \times 10^{-8}$ ;  $z_0 = 0$ , se forma el atractor al evolucionar el tiempo, pero las amplitudes durante el transitorio crecen significativamente, provocando que los productos alcancen valores aproximados a ± 128. Esto ocasionaría la pérdida de la secuencia caótica si solo se utilizaran 4 bits de parte entera. Por ello, una mejor opción es emplear 7 bits.

La tabla 3.1 muestra la distribución de punto fijo seleccionada para este sistema en arquitectura de 64 bits. Con esta distribución se tiene una resolución de  $1.38 \times 10^{-17}$ , lo cual es suficiente para mantener el atractor extraño.

Tabla 3.1: Distribución de la aritmética de punto fijo con 64 bits para el sistema 3D.

| Signo | Parte entera | Parte fraccionaria |

|-------|--------------|--------------------|

| 1 bit | 7 bits       | 56 bits            |

#### 3.2.1.2. Descripción del sistema mediante bloques digitales

Una vez definido el formato de punto fijo, el siguiente paso es llevar a cabo un análisis de las ecuaciones del sistema. En este caso, las expresiones matemáticas presentadas en la ecuación (2.6) consisten solamente en operaciones de suma, resta y multiplicación. Los bloques aritméticos digitales que realizan estas operaciones son circuitos combinacionales, es decir, no dependen de una señal de reloj para su funcionamiento. En lugar de ello, cada bloque requiere un breve tiempo

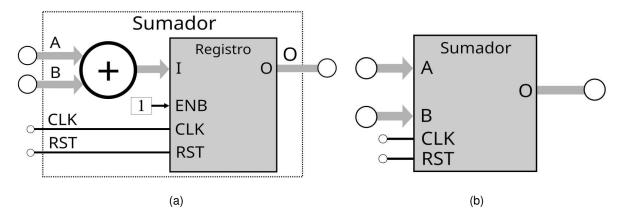

para producir un resultado, conocido como tiempo de propagación, que depende de la tecnología de fabricación de la FPGA. El tiempo de propagación suele ser del orden de los nanosegundos o incluso menor y se puede entender como el tiempo necesario para que la salida de un bloque combinacional produzca un resultado en respuesta a un cambio en las entradas. Sin embargo, cuando dos o más bloques combinacionales se conectan uno tras otro, el tiempo total para obtener un resultado está determinado por la suma de los tiempos de propagación de cada bloque individual. A medida que este tiempo se incrementa, la frecuencia máxima de reloj que puede operar en el sistema para controlar otros circuitos secuenciales, se reduce significativamente. Una manera de evitar esta reducción en la frecuencia de reloj, consiste en segmentar cada ruta de datos añadiendo registros de entrada y salida paralela (PIPO) entre la conexión de dos bloques combinacionales [43]. De esta forma, cada salida de un bloque combinacional se conecta con un registro PIPO, convirtiéndolo en un bloque secuencial. Como ejemplo, la figura 3.1 muestra el circuito interno del bloque sumador, que está compuesto por el sumador combinacional y el registro PIPO para convertirlo en un circuito secuencial, el cual cuenta con un pin de habilitación (ENB). En dicho esquema, las líneas punteadas indican el bloque de mayor jerarquía denominado "Sumador". Por su parte, las líneas gruesas en color gris representan los buses de datos de 64 bits para las operaciones, mientras que las líneas negras son los pines de control para la señal de reloj (CLK) y de reinicio o reset (RST).

Figura 3.1: Sumador: (a) diagrama de hardware digital interno, y (b) representación como bloque secuencial.

El diseño anterior también se aplica para los bloques restadores y multiplicadores. Cabe aclarar que en el bloque restador, la operación de diferencia se ejecuta como: A-B.

Con la segmentación, el tiempo para obtener un resultado depende de la ejecución de varios ciclos de reloj. Estos mismos ciclos se pueden aprovechar para ejecutar otras tareas, mejorando así el procesamiento en paralelo. Además, en algunos sistemas digitales es posible implementar la técnica de la tubería (pipeline); sin embargo, debido a la dependencia de las entradas con las salidas de estos sistemas, esta técnica no puede ser aprovechada por estos diseños.

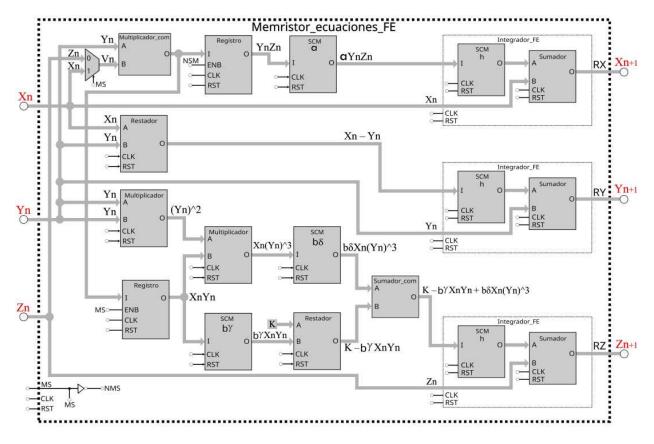

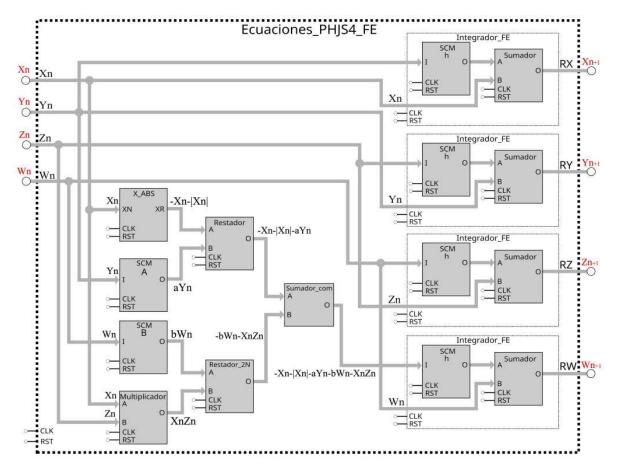

La figura 3.2 ilustra el diagrama de bloques que corresponde con la ecuación (2.6). En el esquema se aprecia la interconexión de bloques secuenciales como sumadores, restadores, multiplicadores y multiplicadores de una sola constante (SCM), junto con bloques combinacionales, indicados con la palabra "com", para desarrollar cada una de las ecuaciones de las variables de estado  $x_{n+1}$ ,  $y_{n+1}$  y  $z_{n+1}$ . La ruta crítica de este sistema, que involucra más bloques y, por lo tanto, más ciclos de reloj, sucede con la variable de estado  $z_{n+1}$ . Además, el diagrama incluye el bloque Integrador\_FE, formado internamente por un SCM y un bloque sumador.

Figura 3.2: Diagrama de bloques de las ecuaciones del sistema 3D basado en un memristor [38].

Dependiendo del modelo de FPGA, los bloques de multiplicación entre variables se pueden

sintetizar utilizando recursos de hardware conocidos como multiplicadores embebidos, que operan con 9 o 18 bits. Sin embargo, cada modelo de FPGA cuenta con un limitado número de estos recursos, y en arquitecturas de 64 bits, estos se consumen rápidamente al emplear unos pocos bloques de multiplicación entre variables. Una manera de reducir el uso de los multiplicadores embebidos es reutilizar un solo bloque multiplicador para realizar varios productos entre variables. En el esquema de la figura 3.2 se observa la conexión de un multiplexor a la entrada B de un multiplicador combinacional, cuya salida O está conectada a dos registros PIPO. Esta conexión permite calcular los productos  $x_ny_n$  y  $y_nz_n$  reutilizado el mismo bloque de multiplicación en dos ciclos de reloj. Dado que la variable  $z_{n+1}$  representa la ruta crítica, en el primer ciclo de reloj se calcula el producto  $x_ny_n$ , y en el segundo, el producto  $y_nz_n$ . Para lograr lo anterior, el pin de entrada MS controla el selector del multiplexor y los habilitadores de los registros. Antes del primer ciclo, el pin debe tener un estado alto, y posteriormente debe colocarse en bajo. Mediante una compuerta lógica NOT, se garantiza que solo un registro a la vez almacene el resultado de una multiplicación.

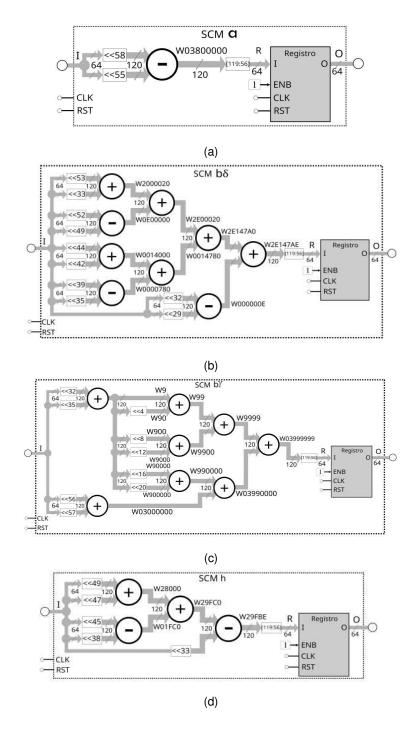

Otra manera de ahorrar multiplicadores embebidos ocurre cuando en un sistema aparece la multiplicación entre una variable y una constante. Esta operación se puede realizar mediante bloques multiplicadores de una sola constante, como se muestra en [31], los cuales emplean recursos lógicos en su síntesis. El bloque SCM realiza la multiplicación, mediante operaciones de suma, resta y desplazamiento. Su funcionamiento se basa en la suma y resta de potencias de dos de la variable a multiplicar. Cada SCM se diseña específicamente para una aritmética de punto fijo particular, utilizando el sistema numérico de dígitos con signo (Signed-digit), el cual representa a los números binarios con los dígitos 1, -1 y 0. La figura 3.3 muestra la estructura interna de los cuatro SCM que se utilizan en este sistema.

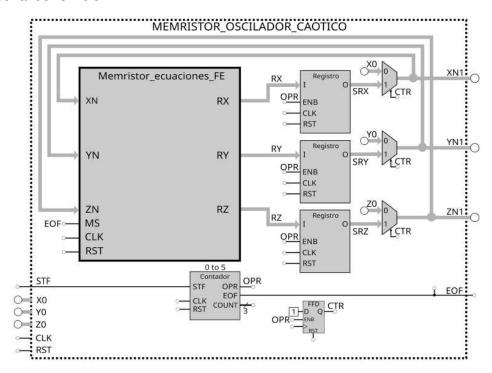

El diagrama de la figura 3.2, que describe las ecuaciones discretas del sistema caótico 3D basado en un memristor, calcula los valores de la siguiente iteración [n+1] para cada variable de estado a partir de los valores actuales n de las mismas, después de cinco ciclos de reloj. Sin embargo, este bloque por sí solo no es suficiente para generar las series temporales de forma indefinida. Para lograrlo, se requiere retroalimentar las salidas RX, RY y RZ con las entradas XN, YN y ZN, además de considerar que en la primera iteración las condiciones iniciales deben conectarse a las entradas del bloque. Debido a estos detalles, es necesario añadir otros recursos de hardware digital. La figura 3.4 muestra el diagrama del oscilador completo, en el cual se

Figura 3.3: Diagramas de bloques de los cuatro SCM mostrados en la figura 3.2 diseñados con una aritmética de punto fijo de 64 bits (1:7:56): a) a, b)  $b\delta$ , c)  $b\gamma$  y d) h.

observa que el bloque Memristor\_ecuaciones\_FE tiene sus tres salidas conectadas a registros de entrada y salida paralela, los cuales se encargan de almacenar los resultados de cada itera-

ción y devolverlos a las entradas para el cálculo de la siguiente. Las salidas de estos registros PIPO están conectadas a multiplexores, que pueden proporcionar las condiciones iniciales para el sistema caótico o conectar las salidas con las entradas.

La arquitectura de la figura 3.4 requiere seis ciclos de reloj para actualizar cada variable de estado. Durante los primeros cinco ciclos, los registros PIPO mantienen el valor actual de cada iteración, y en el sexto ciclo se actualizan con nuevos valores. Esto es posible gracias a un contador cuya salida de control OPR, activa los habilitadores de los registros.

Al iniciar o reiniciar el sistema, un flip-flop tipo D comienza en un estado lógico bajo, para que las condiciones iniciales se apliquen a las entradas del bloque que desarrolla las ecuaciones. Después de los seis ciclos de reloj, este flip-flop cambia a un estado lógico alto, lo cual conecta las salidas de los registros PIPO con las entradas del bloque Memristor\_ecuaciones\_FE, a través de los multiplexores. Para iniciar una nueva secuencia con otras condiciones iniciales, es necesario utilizar la señal de reinicio.

Figura 3.4: Diagrama para el oscilador 3D basado en un memristor.

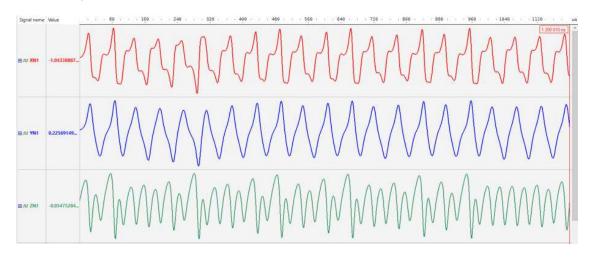

#### 3.2.1.3. Simulación del sistema en Verilog

El software de Active-HDL permite realizar simulaciones de los sistemas caóticos a través de bancos de pruebas, para verificar el funcionamiento del sistema antes de su síntesis en una FPGA, así como la visualización de las series temporales. Además, ofrece herramientas que permiten generar archivos de texto con los resultados de cada iteración. La figura 3.5 muestra las tres series temporales obtenidas mediante la herramienta de forma de onda de Active-HDL.

Figura 3.5: Series temporales del sistema 3D simuladas en Active-HDL.

#### 3.2.1.4. Resultados experimentales

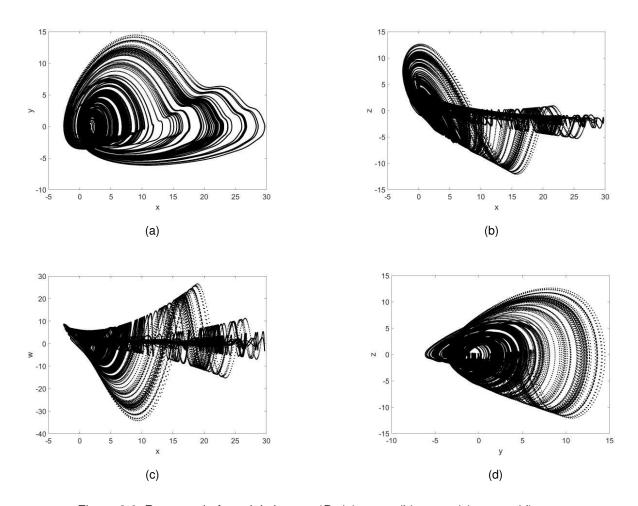

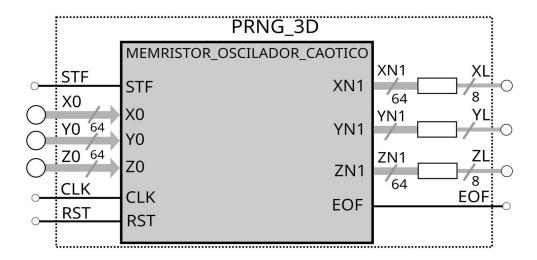

La síntesis de este sistema caótico 3D basado en un memristor, en una FPGA de Altera/Intel, se llevó a cabo en el software de Quartus II. Para visualizar las series temporales y los atractores experimentales, se utilizó un convertidor digital a analógico (DAC) de 16 bits. Por ello, fue necesario añadir bloques adicionales para controlar el DAC por medio del protocolo de interfaz periférica serie (SPI) y realizar el procedimiento de truncamiento de 64 a 16 bits. La figura 3.6 muestra los atractores experimentales obtenidos.

## 3.2.2. Descripción hardware del mapa caótico 2D

#### 3.2.2.1. Análisis de amplitudes para el formato de punto fijo

Al igual que con el sistema caótico 3D, previo a la descripción en Verilog de los bloques digitales, es necesario simular este mapa 2D en un software de alto nivel, para determinar el rango

Figura 3.6: Retratos de fase experimentales del sistema 3D: (a) x - y, (b) x - z, (c) y - z [38].

de amplitudes de las dos variables de estado y los productos que aparecen en las ecuaciones. Después de realizar simulaciones con 1000000 de iteraciones y diferentes condiciones iniciales, los rangos máximos y mínimos, considerando los cuatro conjuntos de parámetros  $a_1$  del mapa, estaban dentro del rango aproximado  $\pm 16$ . Por lo cual, para este mapa el formato de punto fijo solo requiere 4 bits de parte entera. La tabla 3.2 muestra la distribución del formato de punto fijo en 64 bits para este sistema de dos dimensiones.

Tabla 3.2: Distribución de la aritmética de punto fijo con 64 bits para el mapa caótico en 2D.

| Signo | Parte entera | Parte fraccionaria |

|-------|--------------|--------------------|

| 1 bit | 4 bits       | 59 bits            |

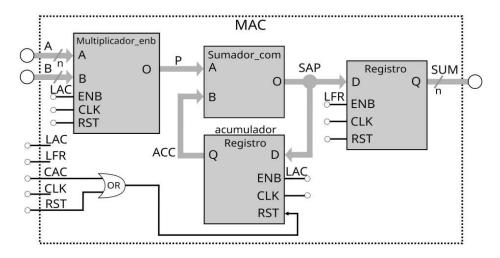

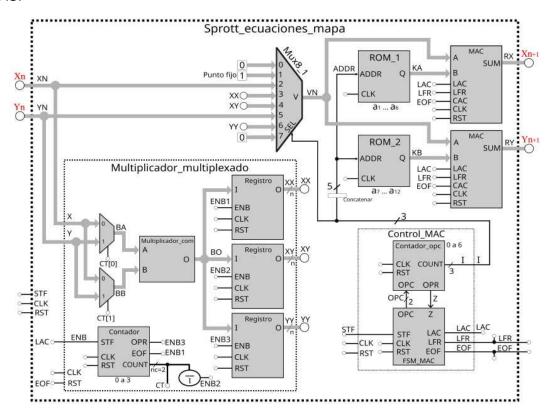

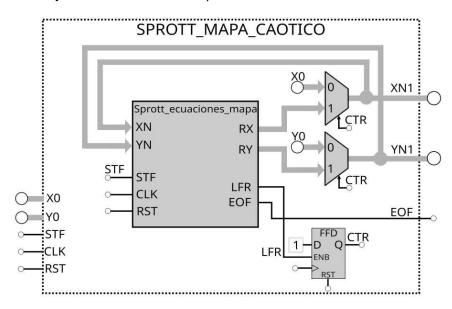

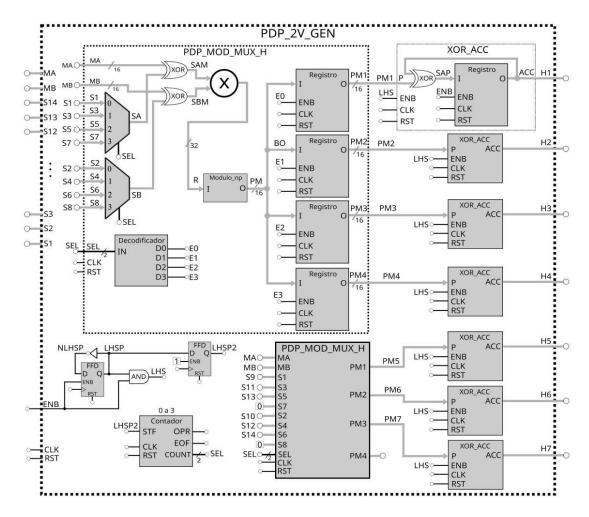

#### 3.2.2.2. Descripción del sistema mediante bloques digitales

Al analizar la ecuación (2.2) del mapa caótico en 2D, se observa que las expresiones que describen a las variables de estado  $x_{n+1}$  y  $y_{n+1}$  presentan una estructura con un orden de operaciones similar, pero con diferentes coeficientes  $a_i$ . La descripción con bloques digitales para FPGA podría implementarse mediante la conexión en serie de sumadores, multiplicadores entre variables y multiplicadores de una sola constante, como se efectuó para el sistema anterior. Sin embargo, para este mapa 2D, una descripción directa de las ecuaciones requeriría del diseño de alrededor de ocho bloques SCM a 64 bits para un único conjunto de coeficientes  $a_i$  o utilizar