## CMOS Circuit Design for Bio-Impedance Spectroscopy Applications

by

### BSc. Joselyn Mayte Fernández Martínez

A Dissertation Submitted in partial fulfillment of the requirement for the degree of:

### **Master of Science in Electronics**

At

Instituto Nacional de Astrofísica, Óptica y Electrónica

November 2024 Tonantzintla, Puebla, México.

Advisored by:

**Dr. Wilfrido Calleja Arriaga Dr. Alejandro Díaz Sánchez** Electronics Department - INAOE

©INAOE 2024 The author hereby grants to INAOE permission to reproduce and to distribute copies of this thesis document in whole or in part.

The deeper I get the less that I know That's the way that it go The less that I know the deeper I go

The Strokes

### Acknowledgements

This work represents the culmination of a collective effort, made possible by those who supported me at crucial moments in my life and from whom I learned valuable lessons.

To my advisors, Dr. Alejandro Díaz Sánchez and Dr. Wilfrido Calleja Arriaga, for their guidance, patience, and support over these two years. Their expertise was crucial in shaping this project. To Dr. Gregorio Zamora Mejía, whose valuable contributions and encouragement were equally essential. I am also grateful to CONAHCYT for the financial support provided through the scholarship with CVU: 1188692.

To my parents, Roberto and Fabiola, my greatest inspiration and unwavering support. Your resilience and encouragement have given me the strength to persevere and achieve this goal. Thank you for being my pillar.

To my siblings, Isaac, Natalia, and Fernanda, for the joy and laughter you bring into my life. You are a constant reminder of how fortunate I am to have you as my family.

To my lab colleagues, Adán and Miguel, for being not only labmates but also a source of learning and motivation. Your support and friendship have been invaluable throughout this journey.

To my dear friends, Laura and Juliet, for arriving at just the right time. Your support and the bond we share have been a great comfort and strength to me.

To the friendships formed during university, Miguel V., Enrique. And especially to Odman, who departed this world but whose essence remains alive in my heart.

Finally, to INAOE for introducing me to many incredible people who, though not mentioned here, have undoubtedly shaped my life in meaningful ways.

### Abstract

The analysis of bioimpedance spectroscopy (BIS) is based on measuring the passive electrical properties of biological tissues and their frequency-dependent response to alternating current. This non-invasive characterization technique has become a fundamental tool for obtaining diagnostic information about the physiological properties of the human body.

The non-invasiveness, continuous monitoring capability, portability, and versatility of BIS systems have become increasingly relevant in the development of new healthy applications and measurement techniques. Additionally, the advancements in CMOS technology, these factors highlight the need to optimize analog and digital blocks to enable precise voltage measurements across a broad frequency range while meeting requirements for noise, power consumption, and area efficiency in both front-end and back-end stages.

This work presents proposed analog and digital blocks for BIS applications designed using UMC 180nm technology. For signal generation in the backend stage, a QFGTmodified ring oscillator topology operating in weak inversion is proposed to generate kilohertz-range signals. The oscillator incorporates dual control mechanisms: one based on a feedback factor,  $\beta$ , and other based on a tuning voltage,  $V_{Tune}$ . As an digital alternative, a Direct Digital Synthesizer (DDS) with signal compression is introduced, reducing the memory consumption of the ROM used to store the discretized sine wave. Finally, the design of a front-end signal conditioning circuit is presented, comprising and high-performance instrumentation amplifier with a gain range of 26–76 dB and an associated CMRR of 130–189 dB.

**Keywords**: Bio-Impedance Spectroscopy Analysis, QFGT-modified ring oscillators, Direct Digital Synthesizer, Instrumentation Amplifier.

# Contents

|                                                                                                | vii                 |

|------------------------------------------------------------------------------------------------|---------------------|

| 1 Introduction                                                                                 | 1                   |

| 1.1 Motivation                                                                                 | 1                   |

| 1.1.1 Objectives                                                                               |                     |

| 1.2 Theoretical Fundamentals                                                                   |                     |

| 1.2.1 Electrical Impedance                                                                     |                     |

| 1.2.2 Electrical Properties of Living Tissues                                                  |                     |

| 1.2.2.1 Dispersion and Dielectric Phenomena                                                    |                     |

| 1.2.2.2 Frequency Response of the Tissue                                                       |                     |

| 1.2.3 Techniques for Measuring Tissue Impedance .                                              |                     |

| 1.2.3.1 Bipolar Technique                                                                      |                     |

| 1.2.3.2 Tetrapolar Technique                                                                   |                     |

| 1.2.4 Electrode-Tissue Interface                                                               | 8                   |

| 1.2.5 Applications of Bio-Impedance in Biomedical M                                            |                     |

| 1.3 Adquisition System Proposal                                                                |                     |

| 1.4 Conclusions                                                                                |                     |

| 2 Signal Generation Proposals                                                                  | 19                  |

| 2.1 Oscillators                                                                                |                     |

| 2.1 Oscillators                                                                                |                     |

| 2.1.2 Delay Cell Types                                                                         |                     |

| 2.1.2 Delay Cell Types                                                                         |                     |

| 2.1.2.1 Maneaus Cent                                                                           |                     |

| 2.1.4 Quasi-Floating Gate Transistors                                                          |                     |

| 2.1.5 Voltaje Follower Structure                                                               |                     |

| 2.1.6 Voltage Follower-modified Maneatis Cell                                                  |                     |

| 2.1.7 Maneatis Cell with Phase Degeneration using Ir                                           |                     |

| Networks                                                                                       |                     |

| 2.1.8 Design and Verification of the different Ring Os                                         |                     |

| 2.1.8.1 Simulation and verification                                                            |                     |

|                                                                                                |                     |

|                                                                                                | iations Analysis 39 |

| 2.1.8.2 Monte Carlo Analysis and Process Van<br>2.2 Direct Digital Frequency Synthesizer (DDS) | -                   |

|              |      | 2.2.2   | Simulation and verification in Aldec-HDL                                              | 44 |

|--------------|------|---------|---------------------------------------------------------------------------------------|----|

|              |      |         | 2.2.2.1 Frequency Divider Module                                                      | 44 |

|              |      |         | 2.2.2.2 Phase Accumulator Module                                                      | 45 |

|              |      |         | 2.2.2.3 Sine Look-Up Table Module                                                     | 46 |

|              |      |         | 2.2.2.4 Top DDS Design                                                                | 47 |

|              |      | 2.2.3   | Synthesis using 180 nm technology                                                     | 48 |

|              |      |         | 2.2.3.1 Timing analysis                                                               | 48 |

|              |      |         | 2.2.3.2 Power Analysis                                                                | 49 |

|              |      | 2.2.4   | Logic Equivalence and Layout                                                          | 50 |

|              | 2.3  |         | isions                                                                                | 51 |

|              |      |         |                                                                                       |    |

| 3            | Inst |         | tation Amplifier Design                                                               | 53 |

|              |      | 3.0.1   | Folded Cascode Operational Transconductance Amplifier (FC-                            |    |

|              |      |         | OTA)                                                                                  | 53 |

|              |      |         | 3.0.1.1 DC Analysis                                                                   | 54 |

|              |      |         | 3.0.1.2 AC Analysis                                                                   | 54 |

|              |      |         | 3.0.1.3 Noise Analysis                                                                | 55 |

|              |      | 3.0.2   | Common-Source Amplifier                                                               | 58 |

|              |      |         | 3.0.2.1 DC Analysis                                                                   | 58 |

|              |      |         | 3.0.2.2 AC Analysis                                                                   | 59 |

|              |      |         | 3.0.2.3 Noise Analysis                                                                | 60 |

|              |      | 3.0.3   | Two-Stages Amplifier                                                                  | 63 |

|              |      |         | 3.0.3.1 Indirect Compensation                                                         | 64 |

|              |      |         | 3.0.3.2 Noise Analysis $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 66 |

|              |      | 3.0.4   | Instrumentation Amplifier                                                             | 67 |

|              | 3.1  | Design  | and Verification of the Two-Stages Amplifier                                          | 69 |

|              |      | 3.1.1   | Simulation and Verification                                                           | 72 |

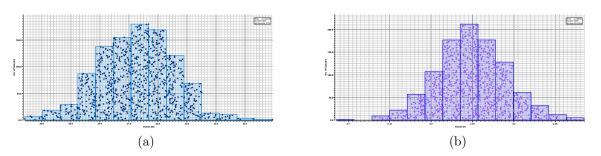

|              |      | 3.1.2   | Process Variations and Monte Carlo Analysis                                           | 74 |

|              | 3.2  | Design  | and Verification of the IA                                                            | 75 |

|              |      | 3.2.1   | Simulation and Verification                                                           | 75 |

|              |      | 3.2.2   | Monte Carlo Analysis and Process Variations                                           | 77 |

|              | 3.3  | Conclu  | usions                                                                                | 78 |

| 4            | Con  | clusior | 18                                                                                    | 81 |

| $\mathbf{A}$ | Mor  | nte Ca  | rlo Simmulations                                                                      | 83 |

| в            | Lay  | out De  | signs                                                                                 | 87 |

| С            | Veri | ilog Co | odes                                                                                  | 93 |

| -            |      | -0 -0   |                                                                                       |    |

# List of Figures

| 1.1                                              | Definition of the impedance $Z(f)$ of a two-terminal system $\ldots \ldots$                  | 3                                      |

|--------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------|

| 1.2                                              | Graphical representations of an impedance response. a) Bode Plot b)                          |                                        |

|                                                  | Cole-Cole Plot                                                                               | 3                                      |

| 1.3                                              | Polarization mechanism under the influence of an electric field                              | 4                                      |

| 1.4                                              | Dispersions illustrated in conductivity and permittivity spectra for muscle.[1               | ] 5                                    |

| 1.5                                              | Low- and high-frequency current paths in tissue. [2]                                         | 6                                      |

| 1.6                                              | Bipolar Technique. a) Representation b) Equivalent circuit                                   | 7                                      |

| 1.7                                              | Tetrapolar Technique a) Representation b) Equivalent circuit                                 | 8                                      |

| 1.8                                              | Complex circuit model for the skin-electrode interface considering elec-                     |                                        |

|                                                  | trode, electrode/skin contact, epidermis, and subcutaneous layers.[3]                        | 9                                      |

| 1.9                                              | Equivalent circuit model for electrode-skin interface                                        | 9                                      |

| 1.10                                             | Comparison of the impedance response for each electrode type $\ldots$ .                      | 10                                     |

| 1.11                                             | Different branches of Bio-Impedance Anaysis in human clinical studies.                       |                                        |

|                                                  | $[4]  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                       | 11                                     |

|                                                  | Signal Conditioning System for Bio-Impedance Measurement. [5]                                | 14                                     |

|                                                  | Devices Under Test                                                                           | 16                                     |

| 1.14                                             | Cole-Cole Plot Response of model and measurement for DUT in Figure                           |                                        |

|                                                  | 1.13                                                                                         | 16                                     |

| 2.1                                              | Classification of the different types of oscillators                                         | 19                                     |

| 2.2                                              | Basic topology of a three-stage ring oscillator                                              | 20                                     |

| 2.3                                              | Time domain response of 3-stages RO of Figure 2.2. [6]                                       | 20                                     |

| 2.4                                              | Basic structure of the Maneatis Cell ( <b>Topology A</b> )                                   |                                        |

| 0 5                                              | Dasic structure of the Maneaus Cen (Topology A)                                              | 22                                     |

| 2.5                                              | DC characterization of the Maneatis Cell. a) Load structure b) Charac-                       | 22                                     |

| 2.5                                              |                                                                                              | 22<br>22                               |

| 2.5<br>2.6                                       | DC characterization of the Maneatis Cell. a) Load structure b) Charac-                       |                                        |

|                                                  | DC characterization of the Maneatis Cell. a) Load structure b) Charac-<br>teristic I-V curve | 22                                     |

| 2.6                                              | DC characterization of the Maneatis Cell. a) Load structure b) Charac-<br>teristic I-V curve | 22<br>24                               |

| $2.6 \\ 2.7$                                     | DC characterization of the Maneatis Cell. a) Load structure b) Charac-<br>teristic I-V curve | 22<br>24                               |

| $2.6 \\ 2.7$                                     | DC characterization of the Maneatis Cell. a) Load structure b) Charac-<br>teristic I-V curve | 22<br>24<br>25                         |

| 2.6<br>2.7<br>2.8                                | DC characterization of the Maneatis Cell. a) Load structure b) Charac-<br>teristic I-V curve | 22<br>24<br>25<br>26                   |

| 2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11         | DC characterization of the Maneatis Cell. a) Load structure b) Charac-<br>teristic I-V curve | 22<br>24<br>25<br>26<br>27<br>27<br>28 |

| 2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12 | DC characterization of the Maneatis Cell. a) Load structure b) Charac-<br>teristic I-V curve | 22<br>24<br>25<br>26<br>27<br>27       |

| 2.14         | Topology of the 5-stage ring oscillator proposed                                                          | 32       |

|--------------|-----------------------------------------------------------------------------------------------------------|----------|

| 2.15         | Biasing block for the Voltage Follower blocks                                                             | 32       |

|              | Characteristic DC transfer curve of the Voltage Follower                                                  | 34       |

|              | AC analysis of the voltage follower.                                                                      | 35       |

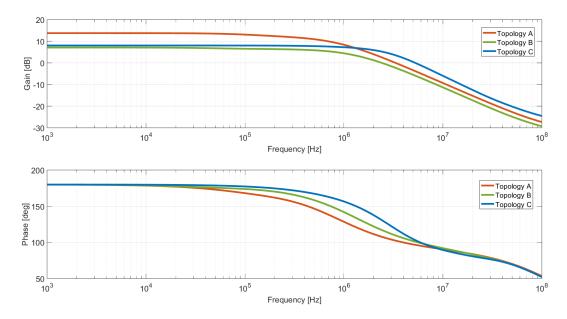

| 2.18         | I-V curve of the load transistors $(M_3 \text{ and } M_4)$ considering different biases.                  | 36       |

|              | Gain and Phase frequency responses of each topology considered                                            | 36       |

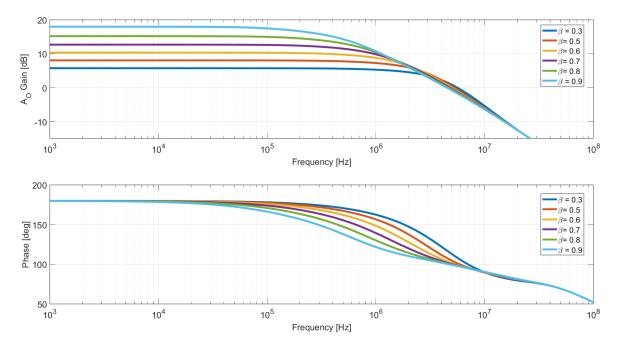

| 2.20         | Gain and Phase frequency response of Topology C, as a function of the                                     |          |

|              | feedback factor $\beta$                                                                                   | 38       |

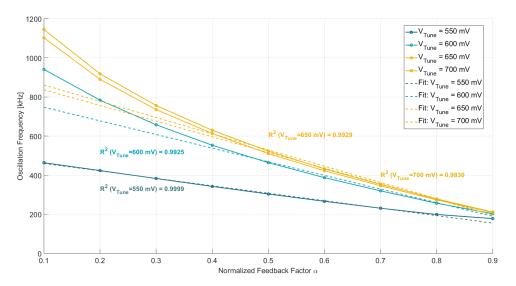

| 2.21         | Characteristic frequency curve as a function of $R_1$ considering the 5-                                  |          |

|              | Stages Ring Oscillator based on Topology C                                                                | 38       |

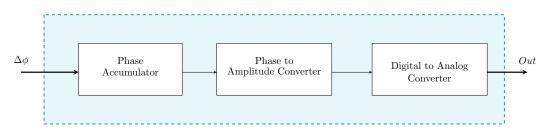

| 2.22         | Block diagram of DDS                                                                                      | 41       |

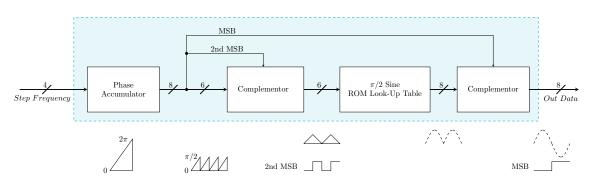

| 2.23         | ROM-based DDS with signal compression                                                                     | 42       |

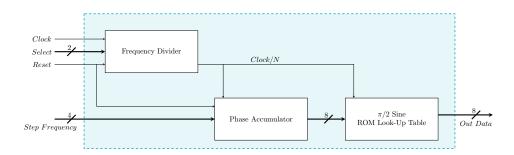

| 2.24         | Top Design of DDS proposed                                                                                | 42       |

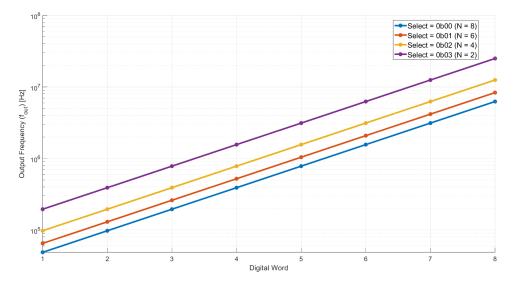

| 2.25         | Output frequency values obtained for different input words                                                | 43       |

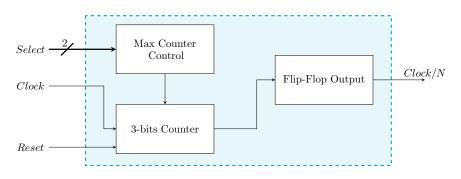

| 2.26         | Block Diagram of Frequency Divider Verilog Module                                                         | 44       |

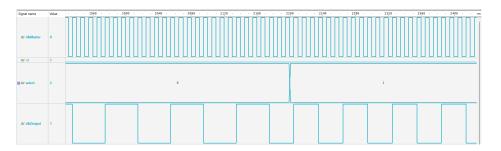

| 2.27         | Simulation of the <b>Clock Divider</b> module for Select $= 0$ (up to 2200 ns)                            |          |

|              | and Select = 1. $\ldots$ | 44       |

| 2.28         | Simulations of the Clock Divider module for different Select configu-                                     |          |

|              | rations                                                                                                   | 45       |

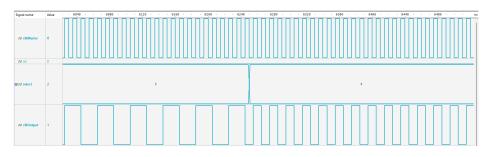

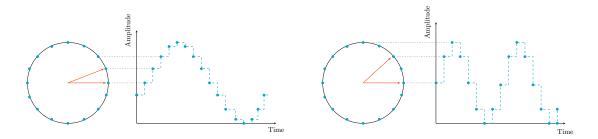

| 2.29         | View of a 16-state phase accumulator operation using a phase wheel to                                     |          |

|              | visualize how the tuning word affects the output frequency of the DDS                                     | 45       |

| 2.30         | Analog signal corresponding to the output of the phaseComp register                                       |          |

|              | considering step $A = 01, 04, and 0A$                                                                     | 46       |

|              | Block Diagram of Sine Look-Up Table Verilog Module                                                        | 46       |

|              | Simulation of the output register for each of the 64 addresses of the LUT                                 | 46       |

|              | Final simulation of the Top design described in Figure 2.24                                               | 47       |

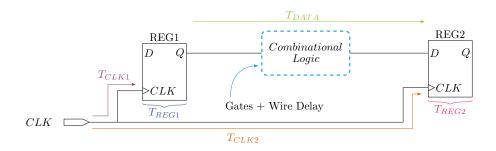

|              | Illustration of slack definition between two synchronous blocks                                           | 48       |

|              | Timing diagram of signals presented in 2.34.                                                              | 48       |

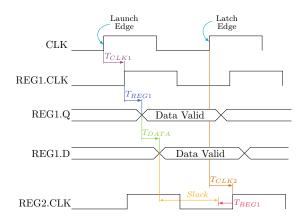

| 2.36         | Histogram of the slack associated with the critical logic paths of the                                    |          |

|              | synthesized design obtained with Genus tool                                                               | 49       |

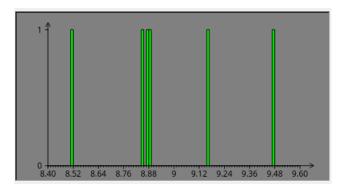

| 2.37         | Resulting schematic from the association of the design with the digital                                   |          |

|              | cells from the library                                                                                    | 51       |

| 3.1          | Folded Cascode OTA Topology                                                                               | 53       |

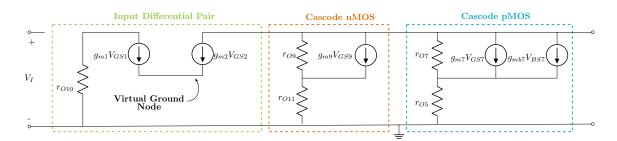

| 3.1<br>3.2   | Small Signal Model of the FC-OTA shown in Figure 3.1                                                      | 55       |

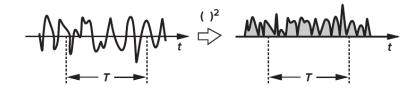

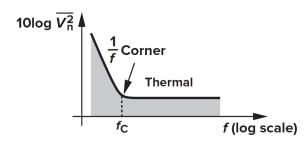

| 3.3          | Average noise power. [7]                                                                                  | 56       |

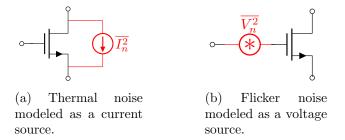

| 3.4          | MOSFET noise modeled as spectral density functions.                                                       | 56       |

| $3.4 \\ 3.5$ | Concept of flicker noise corner frequency. [7]                                                            | 50<br>57 |

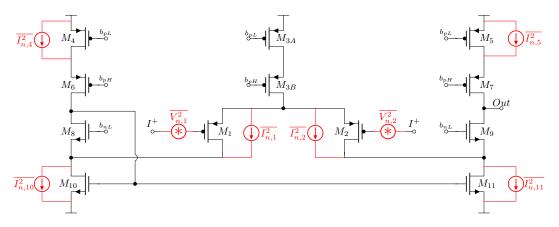

| 3.6          | FC-OTA Topology with significant noise contributions                                                      | 57       |

| 3.0<br>3.7   | Common-Source Amplifier Topology                                                                          | 58       |

| 3.8          | CS-Amplifier with noise contributions.                                                                    | 50<br>60 |

| 3.9          | Two-Stage Operational Amplifier Requirements by Stage. [7]                                                | 63       |

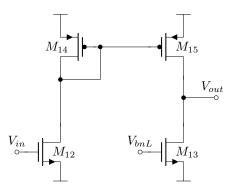

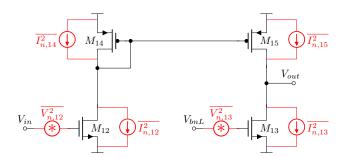

| 3.9<br>3.10  | Two-Stages Amplifier Topology                                                                             | 63       |

|              | Typical Feedback Configuration                                                                            | 64       |

|              | Block diagram of the topology shown in Figure 3.11                                                        | 64       |

| 0.12         | DIOCK diagram of the topology shown in Figure 3.11                                                        | 04       |

| 3.13       | Model used to estimate bandwidth with indirect compensation. [8]               | 65 |

|------------|--------------------------------------------------------------------------------|----|

| 3.14       | Noise performance of a cascade of amplifiers                                   | 66 |

| 3.15       | The Classic Three Op-Amp IA Circuit                                            | 67 |

| 3.16       | Detailed noise model of a Three-Amp IA. [9]                                    | 69 |

|            | Bias Voltage Generation Circuit.                                               | 70 |

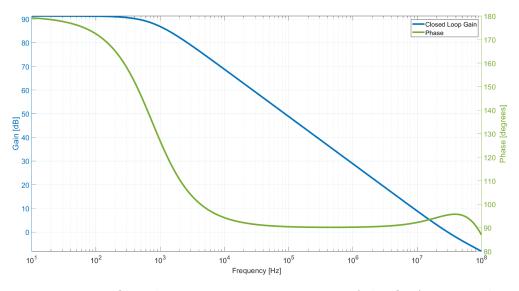

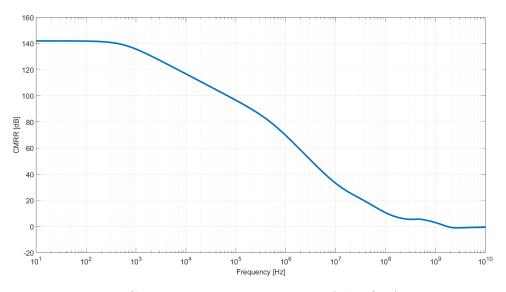

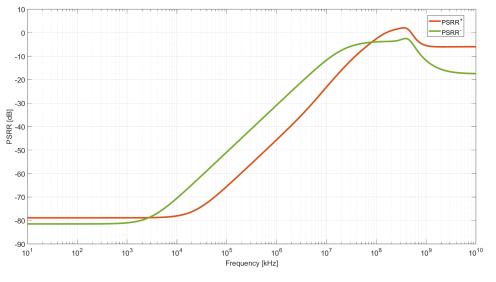

| 3.18       | Closed Loop Frequency Response of the OTA proposed                             | 72 |

| 3.19       | CMRR Frequency Response of the OTA proposed                                    | 72 |

|            | Top Design of DDS proposed                                                     | 73 |

|            | Frequency response of the IA at an approximate gain of 20 dB; differ-          |    |

|            | ential mode gain, common mode gain, and CMRR are shown in green,               |    |

|            | blue, and orange, respectively.                                                | 75 |

| 3.22       | Frequency response of the IA at an approximate gain of 20 dB; differ-          |    |

|            | ential mode gain, common mode gain, and CMRR are shown in green,               |    |

|            | blue, and orange, respectively.                                                | 76 |

| 3.23       | Characteristic curve of the differential mode gain (blue) and CMRR             |    |

|            | (green) as a function of $R_G$                                                 | 76 |

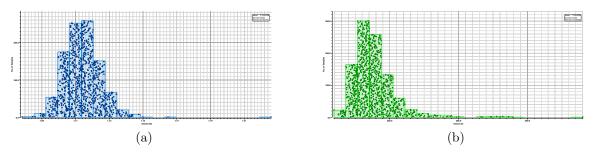

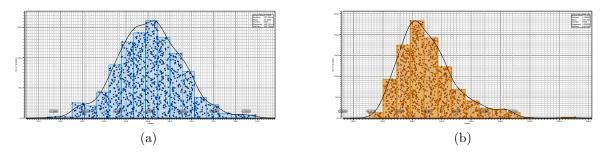

| A.1        | Monte Carlo Results for Transient Analysis. a) Topology A-based RO.            |    |

|            | b) Topology B-based RO.                                                        | 83 |

| A.2        | Monte Carlo Results for Transient Analysis. a) RO with $\beta = 0.5$ b)RO      |    |

|            | with $\beta = 0.1$                                                             | 83 |

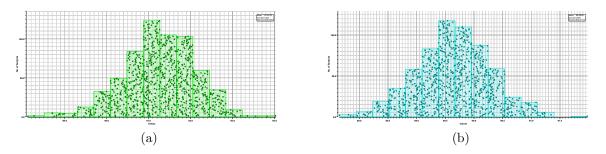

| A.3        | Monte Carlo Results for Stability Analysis. a) Closed-Loop Gain. b)            |    |

|            | Phase Margin.                                                                  | 84 |

| A.4        | Monte Carlo Results for Stability Analysis. a) $PSRR^+$ b) $PSRR^-$ c)         |    |

|            | CMRR                                                                           | 84 |

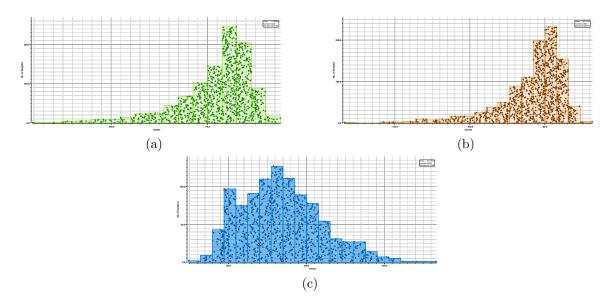

| A.5        | Monte Carlo simulation results. a) Slew Rate $(+)$ b) IRN $\ldots$             | 85 |

| A.6        | Monte Carlo Results for AC Analysis. a) Gain. b) CMRR                          | 85 |

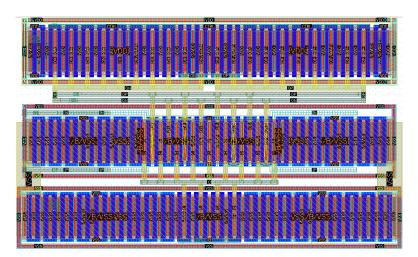

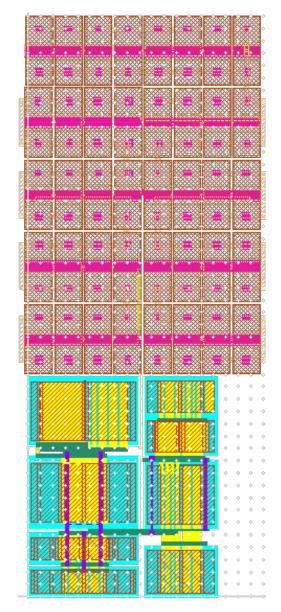

| B.1        | Final Layout of the Basic Maneatis Cell Delay ( <b>Topology</b> $\mathbf{A}$ ) | 87 |

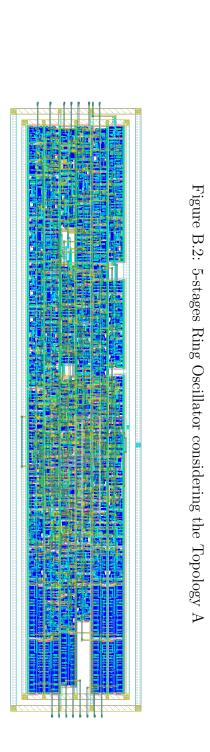

|            | 5-stages Ring Oscillator considering the Topology A                            | 88 |

| B.2        |                                                                                |    |

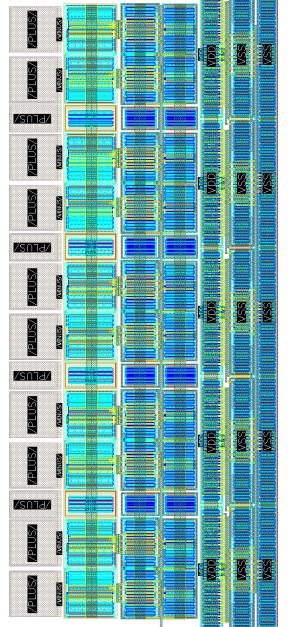

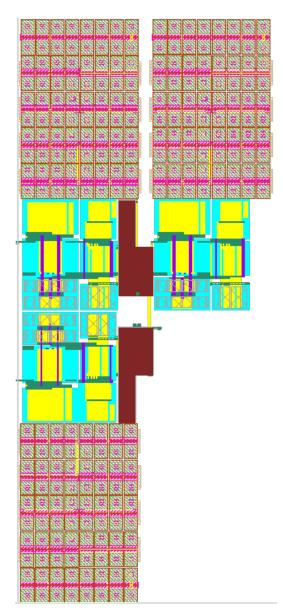

| B.2<br>B.3 | Final Layout proposal for the proposed DDS                                     | 88 |

|            | 0 0 1 00                                                                       |    |

| B.3        | Final Layout proposal for the proposed DDS                                     | 88 |

# List of Tables

| 1.1  | Biological mechanisms in dispersion regions [10]                              | 6  |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | Mean values for typical electrodes used in medical applications               | 10 |

| 1.3  | Summary of monitoring applications of Bio-Impedance with key param-           |    |

|      | eters and references.                                                         | 13 |

| 2.1  | Design specifications of biasing circuit cell of 10 $\mu$ A                   | 33 |

| 2.2  | Dimensions corresponding to Voltage Follower Bias Cell                        | 33 |

| 2.3  | Dimensions corresponding to Voltage Follower                                  | 34 |

| 2.4  | Dimensions corresponding to Basic Maneatis Cell Delay                         | 35 |

| 2.5  | Comparison of the frequency response of the different delay cells             | 37 |

| 2.6  | Comparison of the time response of the Ring Oscillators based on the          |    |

|      | different topologies                                                          | 37 |

| 2.7  | Summary of the results obtained from the process variation analysis.          | 39 |

| 2.8  | Results of the process variation analysis for the different ring oscillators. | 40 |

| 2.9  | Summary of Monte Carlo simulation results for the different Ring Os-          |    |

|      | cillators                                                                     | 40 |

|      | Power Detail Report                                                           | 50 |

| 2.11 | Logic Equivalence Check                                                       | 50 |

| 3.1  | Summary Design Parameters                                                     | 62 |

| 3.2  | Design specifications of biasing circuit cell of 250 $\mu$ A                  | 69 |

| 3.3  | Dimensions corresponding to the Biasing Stage                                 | 70 |

| 3.4  | Design specifications of 2-Stages Amplifier                                   | 71 |

| 3.5  | Dimensions corresponding to the Two-Stage Amplifier                           | 71 |

| 3.6  | Summary of nominal characterizations of the two-stage amplifier               | 73 |

| 3.7  | Results obtained from process variations for the two-stage amplifier          | 74 |

| 3.8  | Summary of Monte Carlo simulation results for the two-stage amplifier.        | 75 |

| 3.9  | Results obtained from process variations for IA                               | 77 |

| 3.10 | Summary of Monte Carlo simulation results for IA                              | 77 |

| 3.11 | Comparison of the implemented design against the state of the art             | 79 |

## CHAPTER 1

# Introduction

This chapter outlines this work's specific goals and objectives, providing a clear structure for the study. Moreover, it introduces tissue behavior and the appropriate techniques for bio-impedance measurements. It begins by focusing on the impedance response in the frequency domain. Finally, it briefly describes the biological phenomena involved in measuring tissue impedance, highlighting the frequency ranges of each biological mechanism.

### 1.1 Motivation

In recent years, Bio-Impedance Spectroscopy (BIS) analysis is a non-invasive method that has positioned itself as an alternative to continuous monitoring and early detection of diseases, even as a novel tool to generate tomographic type images, therefore, to exploit the full potential of Bioimpedance Spectroscopy measurements it is essential using front-end and back-end systems that require high accuracy and a wide bandwidth range. These systems are usually implemented as application-specific integrated circuits (ASICs) in CMOS technology that allow the integration of analog and digital blocks on a single chip at a reasonable cost.

Typically, BIS architectures comprise a back-end consisting of a signal generator over the frequency range of interest and a transconductor stage to convert the voltage signal into a current to be injected into the Tissue Under Test (TUT). On the other hand, the front-end stage allows the voltage reading of the generated response to subsequently calculate the magnitude and phase of the associated, or the real and imaginary component.

However, the integration of this type of systems involves designing robust systems to artifacts due to the electrodes, high dynamic range  $(1 \text{ m } \Omega - 10 \text{ k} \Omega)$ , high skin-electrode impedances (10 k $\Omega$  - 10 M $\Omega$ )). Similarly, the need for low-power consumption and safety compliance to medical standards (IEC) requires customized approaches that take advantage of the benefits offered by analog and digital design.

Although many publications address specific components such as internal amplifiers, signal generators, and a voltage-controlled current source (VCCS), the implementation of the front-end and back-end of the system represents a challenge in the design of the

BIS ASIC due to the wide frequency range over which it must work, raising the need to improve designs or include topologies that allow an accurate measurement considering the abovementioned aspects.

Using BIS analysis as a non-invasive continuous monitoring tool represents an opportunity for optimizing ASICs that perform these measurements. The wide range of frequencies over which it works, as well as the power consumed by the system, represents a tradeoff in the design of each of the blocks that make up the ASIC; on the other hand, implementing a back-end stage that meets the specifications of medical standards represents a necessity not only in a structured design but in a complete integration of a high-performance BIS system.

#### 1.1.1 Objectives

To conduct a comprehensive study of the requirements for various applications of Bio-Impedance Spectroscopy (BIS) analysis, aiming to provide an overview of the architectures capable of performing these measurements. That includes developing a macromodeling methodology for blocks comprising an impedance measurement system and proposing analog signal generators based on QFGT-modified Ring Oscillators and digital signal generators using a Direct Digital Synthesizer (DDS) approach. Additionally, the research aims to design an initial signal conditioning front-end to facilitate accurate impedance measurements.

#### Specific objectives

- Study the principles of Bio-Impedance measurement, including excitation signal generation, impedance modeling and equivalent electrical representation of the measurement system.

- Investigate the fundamental building blocks of a bioimpedance front-end system, including their interdependencies and the critical parameters used to assess their performance.

- Analyze the theoretical performance of existing architectures for Bio-Impedance front-end electronics and correlate these findings with the state of the art to identify limitations and opportunities for improvement.

- Propose a novel design approach to signal generator using a QFGT-modified Maneatis Cell Ring Oscillator to generate a signal over a wide frequency range.

- Design and optimize the proposed architecture and validate through process variations and Monte Carlo analysis to verify the robustness of the design, making each block relevant to Bio-Impedance applications.

### **1.2** Theoretical Fundamentals

#### **1.2.1** Electrical Impedance

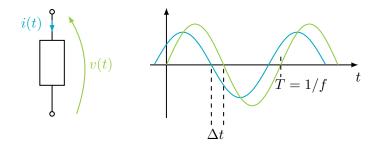

The electrical impedance of a two-terminal system is a complex quantity equal to the ratio between the voltage signal applied to the two-terminal element and the corresponding current flowing through it, according to Ohm's law, impedance (Z) is frequency dependent and equal to the complex ratio of the AC voltage (V) over the current (I), as is described in Equation 1.1.

$$Z(f) = \frac{1}{Y(f)} = \frac{V_O sin(2\omega t + \phi)}{I_O sin(2\omega t)} = Re(Z) + jIm(Z) = R + jX$$

(1.1)

In Equation 1.1, the  $I_O$  and  $V_O$  are the injected current and recorded voltage signal amplitudes, as shown in Figure 1.1, t is time,  $\phi$  is the phase difference between current and voltage (positive or negative, depending if an inductive or capacitive), Y is the admittance, Re(Z) is the real part of the impedance, which is the resistance (R) and Im(Z) is the imaginary part of the impedance, known as the reactance (X).

Figure 1.1: Definition of the impedance Z(f) of a two-terminal system

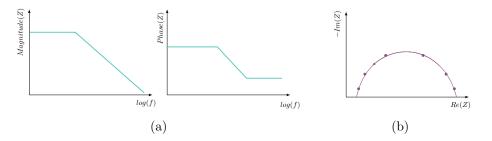

The Bode Plot and the Cole-Cole Plot are two standard tools for analyzing impedance in the frequency domain. The Bode plot (shown in Figure 1.2a) is graphical representation of the polar form of the frequency response of the analyzed system. This representation provides information on essential parameters such as cut-off frequency, resonance frequency, and system stability.

Figure 1.2: Graphical representations of an impedance response. a) Bode Plot b) Cole-Cole Plot

The Cole-Cole Plot is a particular case of the Nyquist plot that decomposes the impedance value into its real and imaginary parts (calculated or measured over a range of frequencies), representing them as a set of points on a complex plane as is shown in Figure 1.2b). This representation helps to describe the behavior of nonlinear systems or those whose changes vary significantly with frequency. Additionally, it allows for showing the behavior of the time constants in the impedance, which correspond to semicircles in the complex plane.

#### **1.2.2** Electrical Properties of Living Tissues

A specific conductivity  $\sigma$  and a relative permittivity  $\epsilon_r$  can characterize every material. To incorporate the losses due to the dielectric and the frequency dependence of the material, the conductivity and permittivity are defined as complex quantities in the time domain, as shown in 1.2 - 1.5. [2] [10] Where  $\hat{\sigma}(\omega)$  and  $\hat{\epsilon}(\omega)$  are the complex conductivity and permittivity respectively.

$$\hat{\sigma}(\omega) = \sigma' + j\sigma'' \tag{1.2}$$

$$\hat{\epsilon}(\omega) = \epsilon' - j\epsilon'' = (\epsilon'_r - j\epsilon''_r)\epsilon_0 \tag{1.3}$$

where

$$\sigma'' = \omega \epsilon' \tag{1.4}$$

and

$$\epsilon'' = \frac{\sigma'}{\omega} \tag{1.5}$$

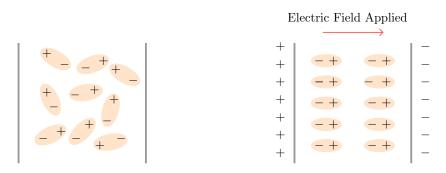

All living tissues are wet biological materials with DC conductivity because the ions are free and can migrate. [11] Polarization and the displacement of charges do not occur instantaneously when an electric field is applied, as shown in Figure 1.3. When the frequency is low enough, all charges in the tissue have the necessary time to change their position and then the polarization is maxima. While when the frequency increases the polarization and the permittivity decrease.[11] [12]

Figure 1.3: Polarization mechanism under the influence of an electric field

The time it takes for charges to change their position due to an increase or decrease in an induced electric field is known as **relaxation time**. [2] The dispersion mechanism can also be analyzed in frequency domain as a function of the permittivity of the material.

#### 1.2.2.1 Dispersion and Dielectric Phenomena

In general, the tissue is an anisotropic medium due to the orientation of cells, macromembranes, and organs. A first approximation to the frequency behavior of biological tissues can be observed in [1], which proposed a distribution of time constants (DRT) for different tissues and biological fluids based on real measurements.

Equation 1.6 allows us to describe the frequency behavior of the tissue as a sum of the contributions of each variations in permittivity associated with the time constant, where  $\alpha$  is the distribution parameter,  $\tau$  is the relaxation time constant of the polarization mechanism,  $\epsilon_{\infty}$  is the high frequency dielectric constant,  $\sigma$  is the static ionic conductivity. [1]

$$\hat{\epsilon}(\omega) = \epsilon_{\infty} + \sum_{n} \frac{\Delta \epsilon_{n}}{1 + (j\omega\tau_{n})^{(1-\alpha)}} + \frac{\sigma}{j\omega\epsilon_{0}}$$

(1.6)

With the permittivity response, the complex conductivity and the tissue impedance can be calculated using Equations 1.7 and 1.8, respectively.

$$\hat{\sigma}(\omega) = j\omega\epsilon_0\hat{\epsilon}(\omega) \tag{1.7}$$

$$\hat{z}(\omega) = \frac{1}{\hat{\sigma}}(\omega) \tag{1.8}$$

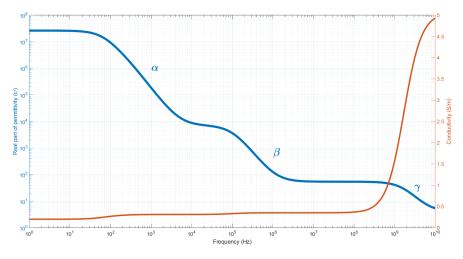

The frequency response of permittivity for any tissue can be plotted using Equation 1.6 and the time constants defined in [1]. Figure 1.4 shows the MATLAB simulation of the frequency response for the permittivity and conductivity of muscle tissue (transversal).

In this response, as frequency increases, permittivity decreases nonlinearly. These changes occur primarily in three steps associated with dispersions defined in [13]:  $\alpha$  defined in the range of Hz to kHz,  $\beta$  established in the range of hundreds of kHz to MHz, and finally  $\gamma$  at frequencies on the order of GHz. Table 1.1 details the biological

Figure 1.4: Dispersions illustrated in conductivity and permittivity spectra for muscle.[1]

mechanisms involved in each frequency range corresponding to the dispersions indicated in Figure 1.4. This information allows to define the frequency range within the characteristics of the tissue can be analysed.

| Type | Characteristic Freq. | Mechanism                                                                                              |

|------|----------------------|--------------------------------------------------------------------------------------------------------|

| α    | mHz - kHz            | The dispersion is related with ionic diffusion gated cell membrane channels and cell membrane effects. |

| eta  | 0.1 - 100M Hz        | Protein molecule response,<br>cell membrane polarizations relaxations<br>and Maxwell-Wagner effects.   |

| γ    | 0.1 - 100 GHz        | Dipolar polarization mechanisms<br>in polar media and the abundant tissue water.                       |

#### 1.2.2.2 Frequency Response of the Tissue

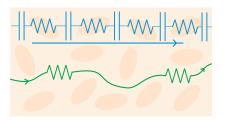

The effect of applying an external electric field (usually through a known current) is known as the **exogenic method** according to [10]. This method primarily involves the induced electric field displacing charges, forming dipoles, and polarizing the material [11]. Due to the anisotropy of biological tissues, the response to an induced electric field varies non-linearly depending on the frequency of the injected signal. Figure 1.5 shows two pathways through which the current can flow.

- DC and Low Frequencies (green path): The medium where the cells are located acts as a resistance due to intracellular and extracellular fluids, causing current to flow around the cells.

- High Frequencies (blue path): The capacitances associated with the cell membranes contribute a slight conductance, allowing for some conduction within the cells due to local conductivity.

Figure 1.5: Low- and high-frequency current paths in tissue. [2]

6

#### **1.2.3** Techniques for Measuring Tissue Impedance

Most impedance spectroscopy systems inject a constant current at different frequencies and measure the resulting voltage. Voltage measurement techniques are classified into bipolar and tetrapolar, the primary difference being the number of electrodes used.

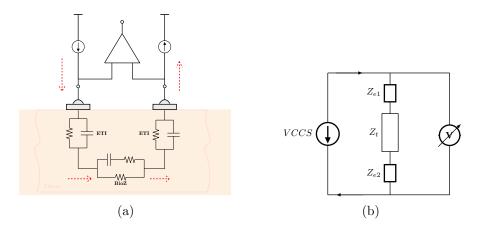

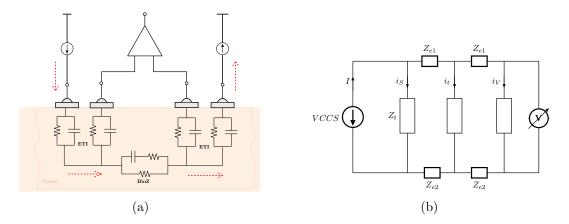

#### 1.2.3.1 Bipolar Technique

In this type of configuration, the current is injected through a pair of electrodes, and the resulting voltages are measured across the same pair of electrodes, as shown in Figure 1.6a, the equivalent circuit associated to the measurement system is shown in figure 1.6b.

Figure 1.6: Bipolar Technique. a) Representation b) Equivalent circuit

In this configuration, the total measured impedance can be expressed as the sum of the impedance due to the tissue-electrode interface (denoted as  $Z_{e1}$  and  $Z_{e2}$ ) and the impedance of the tissue under test as is expressed in Equation 1.9.

$$Z_{meas} = Z_{e1} + Z_T + Z_{e2} \tag{1.9}$$

Assuming both electrodes are identical, then the measured impedance  $(Z_{meas})$  can be expressed according to Equation 1.10

$$Z_{meas} = Z_T + 2Z_e \tag{1.10}$$

From expressions 1.9 and 1.10, it is evident that the influence of the electrodes is the main disadvantage in the measurement process because it is not possible to determine whether the measured variations in the voltage response are due to the tissue response  $(Z_t)$  itself or changes in the electrode impedance  $(Z_{e1}, Z_{e2})$ . Moreover, any noise signal originating from the current source directly affects the load, leading to undesired signals or measurement errors. [14]

#### 1.2.3.2 Tetrapolar Technique

The tetrapolar technique involves using a different pair of electrodes for each stage, with two electrodes for current injection and two for measuring the voltage response, as shown in Figure 1.7.

Figure 1.7: Tetrapolar Technique a) Representation b) Equivalent circuit

The equivalent circuit is shown in Figure 1.7b, and its impact on tissue measurement has been thoroughly analyzed and detailed in [14]. This analysis defines the concept of transfer impedance as the ratio of the resulting potential between the injection and measurement electrodes. As in shown in Equation 1.11, assuming that all electrode impedances are equal  $(Z_{e1} = Z_{e2} = Z_{e3} = Z_{e4} = Z)$ .

$$T_{Z} = \frac{Z_{t}}{1 + Z_{t} \left[\frac{4Z + Z_{V} + Z_{S}}{Z_{V} Z_{S}}\right] + 2Z \left[\frac{2Z + Z_{V} + Z_{S}}{Z_{V} Z_{S}}\right]}$$

(1.11)

Ideally, it is possible to consider that the impedance due to the source  $Z_S$  and the impedance due to the voltage measurement  $Z_V$  tend to infinity; however, the design is limited by the parasitic capacitances connected to ground, particularly at very high frequencies. [14]

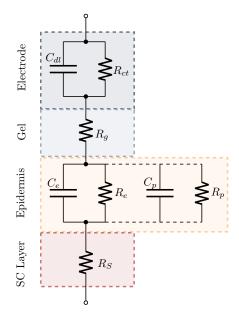

#### **1.2.4** Electrode-Tissue Interface

The connection of the electrode to the tissue involves adding an impedance associated with both the electrode and the tissue interface, commonly referred to as ETI. In [15] and [3], an equivalent circuit model for the skin-electrode interface is proposed, associating resistance and capacitance with each tissue layer involved in the measurement process, as shown in Figure 1.8.

Figure 1.8: Complex circuit model for the skin-electrode interface considering electrode, electrode/skin contact, epidermis, and subcutaneous layers.[3]

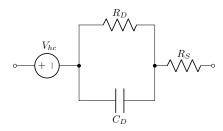

For general purposes, it is possible to simplify the model in Figure 1.8 according to [16] to a simpler model, considering the half-cell potential of the electrode due to the charge distribution between the electrode material and its surface electrolytes caused by oxidation  $(V_{hc})$ . The electrical charges between the skin and the electrode are represented by the capacitance  $C_D$ , and the charge transfer in the conductive medium between the skin and the electrode is represented by  $R_D$ . The under-skin tissue resistance is represented by  $R_S$ .

Figure 1.9: Equivalent circuit model for electrode-skin interface.

Therefore, the simplified impedance of the ETI results in the Equation 1.12.

$$Z_e = R_S + \frac{R_D}{1 + sC_D R_D} \tag{1.12}$$

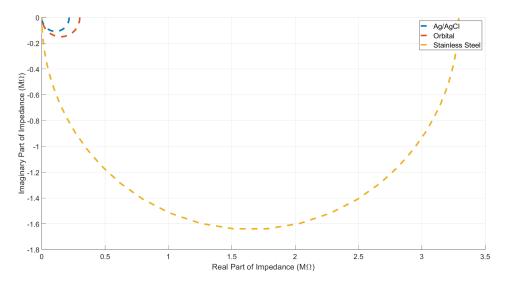

This simplification allows for the characterization of the different types of electrodes that are clinically used. The Table 1.2 shows the mean values for Ag/AgCl, Orbital, and Stainless Steel electrodes according to [16].

9

| Electrode Type  | $R_D [\mathbf{k}\Omega]$ | $C_D [\mathrm{nF}]$ | $R_S \left[\Omega\right]$ |

|-----------------|--------------------------|---------------------|---------------------------|

| Ag/AgCl         | 215.82                   | 18.9                | 399.7                     |

| Orbital         | 299.4                    | 9.3                 | 626.8                     |

| Stainless Steel | 3289.4                   | 4.9                 | 856.4                     |

Table 1.2: Mean values for typical electrodes used in medical applications

Figure 1.10 shows the Cole-Cole plots simulated in MATLAB using the data from Table 1.2 for the electrodes analyzed in [16]. It can be observed that the electrode type with the highest impedance is Stainless Steel, whose response is at least 10 times greater compared to Ag/AgCl and Orbital electrodes.

Figure 1.10: Comparison of the impedance response for each electrode type

The correct choice of electrodes improves the acquisition of the biological signal to be measured. Otherwise, a high electrode-skin impedance would result in poor biological signal quality, low signal amplitude, and low signal-to-noise ratio. [16]

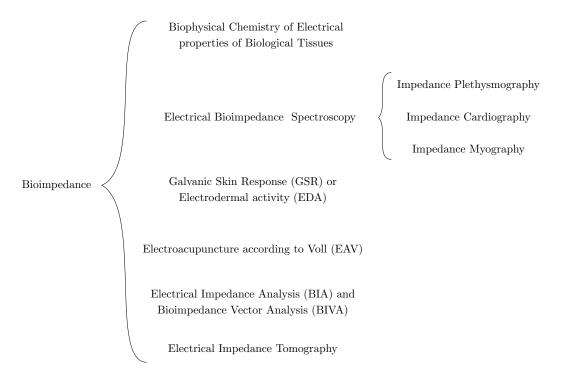

### 1.2.5 Applications of Bio-Impedance in Biomedical Monitoring

In recent years, non-invasive monitoring techniques have gained clinical relevance for accurately detecting diseases. In this context, Bio-Impedance measurement has emerged as a prominent approach.[17] It has been demonstrated that Bio-Impedance monitoring through various methods holds significant clinical applications as is detailed shown in Figure 1.11. [4]

According to Table 1.3, body composition analysis typically utilizes frequency ranges from 50 kHz to 1 MHz in Bio-Impedance spectroscopy (BIS) applications. This frequency range is selected because, at these frequencies, the impedance of the cell membrane predominates, enabling precise measurements of intracellular and extracellular fluid volumes.

Although the amplitude of the applied current is generally very low (typically ranging from  $\mu A$  to mA) [18] recommends a current value of 800  $\mu A$ . Furthermore, studies have demonstrated a strong correlation between BIS and multiple dilution techniques for assessing total body water (TBW).

In [19], a measurement technique operating at specific frequencies: 5, 50, and 250 kHz, this was proposed to analyze segmental phase angles for diagnosing diabetes-mellitus in individuals. On the other hand, other studies have focused on narrower frequency ranges, such as 455.5 kHz for electrical measurements [20]. Additionally, [21] explored a broader frequency range, from 10 kHz to 100 kHz, for bio-impedance measurement

applications. For heart rate applications, the frequency operations region in this study refers to the use of a 30 kHz frequency to inject a current of 1 mA for Bio-Impedance measurements on the participants. [22] Other authors [23] validate the use of BIS to heart rate applications using commercial devices.

In [24], the frequency range analysis focused on applying an alternating signal with frequencies ranging from 100 Hz to 0.1 MHz to measure the impedance parameters of subjects' skin. This study demonstrated significant differences in resistance, capacitance, and phase measurements between hydrated and dehydrated states, highlighting the potential of bio-impedance analysis to classify hydration status. A commercial bio-impedance analysis device was utilized for the measurements, and the summarized data in Table 1.3 was extracted from the manufacturer's datasheet.

Besides, [25] suggests that for accurate hydration parameter measurements, it is advisable to operate within a frequency range of 1 kHz to 1 MHz, as noted in [10]. This analysis typically applies a current in the range of 500–800  $\mu$ A and emphasizes that the distance between the signal and detection electrodes should be at least 5 cm to minimize measurement errors.

Advanced applications employ bio-impedance as an alternative method to tomography or as an imaging tool by using an array of electrodes placed over the region of interest. These systems map the measured impedance values to associated colors, enabling visual representation. The selection of the operating frequency range depends on the specific application within the human body and the desired trade-off between spatial resolution and penetration depth.

In general, Electrical Impedance Tomography (EIT) systems tailor their operating frequency range to the specific tissue being imaged, considering factors like the impedance of the tissue, size of the region of interest, and the desired imaging depth. [26] [27] In EIT systems, the number of electrodes used for data collection is critical for image resolution. Common configurations include systems with 8, 16, 32, 64, or even 128 electrodes.

| Analysis               | Frequency Range                                 | Current Applied                                | Current Applied Electrode Distance References | References       |

|------------------------|-------------------------------------------------|------------------------------------------------|-----------------------------------------------|------------------|

| Body Composition       | 50 kHz - 1 MHz                                  | $800 \ \mu A$                                  | 4 - 7 cm (S.A.)                               | [28], [18], [29] |

| Glucose Analysis       | Multi-frequency                                 | Not mentioned                                  | $5 \mathrm{cm} (\mathrm{S.A.})$               | [19], [20], [21] |

| Heart Rate             | 30 kHz - 50 kHz                                 | $1 \mathrm{mA}$                                | Variable ( $\leq 10 \text{ cm}$ )             | [22], [23]       |

| Hydration Assessment   | $5 \mathrm{~kHz} \mathrm{~a} 100 \mathrm{~kHz}$ | 620 $\mu\mathrm{A},$ 500 - 800 $\mu\mathrm{A}$ | $5 \mathrm{~cm}$                              | [24], [25], [30] |

| EIT                    | 10  Hz  a  10  MHz                              | 10 $\mu$ - 1 mA                                | Circular matrix                               | [27], [26]       |

| C A . Commutal Analian |                                                 |                                                |                                               |                  |

| s.                                                                             |

|--------------------------------------------------------------------------------|

| ence                                                                           |

| refer                                                                          |

| s and ref                                                                      |

| rs a                                                                           |

| nete                                                                           |

| nary of monitoring applications of Bio-Impedance with key parameters and refer |

| key                                                                            |

| rith                                                                           |

| ce w                                                                           |

| edan                                                                           |

| mpe                                                                            |

| -I                                                                             |

| f Bi                                                                           |

| 0                                                                              |

| cions                                                                          |

| cat                                                                            |

| nary of monitoring appli                                                       |

| 60<br>60                                                                       |

| rin                                                                            |

| litc                                                                           |

| nor                                                                            |

| ofr                                                                            |

| ry                                                                             |

| ma                                                                             |

| IMI                                                                            |

| $\mathbf{S}_{\mathbf{U}}$                                                      |

| 1.3:                                                                           |

|                                                                                |

| able                                                                           |

| ñ                                                                              |

S.A.: Segmental Analysis Commercial Device (Bodystat Multiscan 5000 ⓒ)

### **1.3** Adquisition System Proposal

The impedance behavior can be described in terms of magnitude and phase using topologies such as Peak Detector or Rectification and low-pass filter (LPF) applied to the signals acquired by the instrumentation amplifiers [31], [32]. Other topologies propose Synchronous Sampling at points where the injected signal is at its zero and maximum values, allowing the calculation of the real and imaginary parts of the impedance within a single channel [33], [34], [35]. Additional structures suggest a bridge-based method, consisting of the unknown impedance (typically the Tissue Under Test) in series with a known impedance, which can be adjusted to balance the response of the current applied to the load [36], [37], [38].

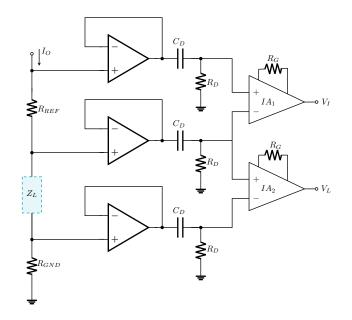

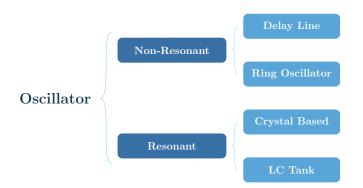

The topology considered for signal measurement is the one proposed in [5] due to the simplicity. This topology allows for reading and recording data on current, voltage, and phase difference throughout the measurement process. The reference resistor ( $R_{REF}$ ) is used to ensure that the current measured by the data acquisition system accurately reflects the current injected into the sample.

Figure 1.12: Signal Conditioning System for Bio-Impedance Measurement. [5]

The structure of the Bio-Impedance spectroscopy measuring system shown in Figure 1.12 can be explained as follows:

- The buffer is an isolation circuit, it serves to ensure that the current and voltage signals are not affected by the circuit afterwards.

- The RC circuit after buffer forms a high pass filter (HPF) set at 10 Hz cut-off frequency to eliminate DC-offset voltage.

- The IA is used to convert the differential signal to single ended, by amplifying the signals  $(G_1 \text{ and } G_2)$  through  $R_G$  selection.

• The value of the actual current  $I_Z$  is the voltage on the reference resistor divided by the value of the reference resistor  $R_{REF}$ .

The output signals correspond to the reference voltage signals (the voltage generated by the resistance  $R_{REF}$  and the input current  $I_Z$ ) and the voltage generated by the load impedance  $(Z_L)$ , thus input current  $I_Z$  indirectly through  $V_I$  using the Equation 1.13

$$|I_Z| = \frac{|V_I|}{G_1 * R_{REF}}$$

(1.13)

Where  $G_1$  corresponds to the gain of the instrumentation amplifier  $(IA_1)$ , and the voltage measured across the load is across  $V_L$  using the Equation 1.14

$$|V_Z| = \frac{|V_L|}{G_2} \tag{1.14}$$

Similarly,  $G_2$  is the gain of the instrumentation amplifier  $(IA_2)$ , so that the impedance of the load can be calculated as shown in Equation 1.15.

$$|Z_L| = \frac{|V_L|}{|I_Z|}$$

(1.15)

And therefore, the phase shift of the signals is measured through  $V_I$  and  $V_L$  as is explained in Equation 1.16.

$$\theta_L = \theta_{VL} - \theta_{VI} = 360^\circ \frac{\tau}{T} \tag{1.16}$$

Where  $\tau$  is the time delay between the signals  $V_L$  and  $V_I$ , T is the period of the  $I_Z$  signal.

The resistive part (associated with  $Z_{L,Re}$ ) and the reactive part (associated with  $Z_{L,Im}$ ) of the load impedance can be calculated using the Equations 1.17 and 1.18.

$$Z_{L,Re} = |Z_L|\cos(\theta_L) \tag{1.17}$$

$$Z_{L,Im} = |Z_L|\sin(\theta_L) \tag{1.18}$$

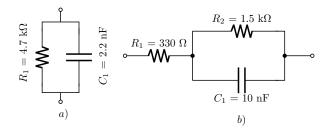

To verify the considered system and the macromodelling, 2 different loads are considered and shown in Figure 1.13. For the first case (Fig. 1.13a)), the analysis focuses on the combination of resistive and capacitive elements, with proposed values of  $R_{L2} = 4.7 \text{ k}\Omega$  and  $C_{L2} = 2.2 \text{ nF}$ , the second case (Figure 1.13b)), an equivalent electrical tissue model is employed, as detailed in [39].

The expression of the characteristic impedance in each case of Fig. 1.13 is described through Equations 1.19 - 1.20.

$$Z_A(f) = \frac{R_{L2}}{1 + (2\pi f R_{L2} C_{L2})^2} - j \frac{2\pi f R_{L2}^2 C_{L2}}{1 + (2\pi f R_{L2} C_{L2})^2}$$

(1.19)

$$Z_B(f) = R_{L3} + \frac{R_{L2}}{1 + (2\pi f R_{L4} C_{L3})^2} - j \frac{2\pi f R_{L4}^2 C_{L3}}{1 + (2\pi f R_{L4} C_{L3})^2}$$

(1.20)

Figure 1.13: Devices Under Test

In this way, the magnitude and phase of each load, can be calculated using the rectangular form expressed in Equations 1.17 - 1.18.

$$|Z_L| = \sqrt{Z_{L,Re}^2 + Z_{L,Im}^2} \tag{1.21}$$

$$\theta_L = \arctan\left(\frac{Z_{L,Im}}{Z_{L,Re}}\right) \tag{1.22}$$

The response is compared against the measurements obtained from the proposed system to validate the model defined by Equations 1.19 and 1.19 for each case. Figure 1.14 presents the Cole-Cole plot of the simulated results for each scenario.

Figure 1.14: Cole-Cole Plot Response of model and measurement for DUT in Figure 1.13

### 1.4 Conclusions

Bio-Impedance Spectroscopy (BIS) systems are specialized devices developed to measure and extract the electrical properties of biological tissues, subsequently converting these properties into digital data for further analysis. The importance of BIS systems lies in their expanding role within the growing field of non-invasive medical monitoring, which offers significant potential for real-time health assessment and management.

Throughout this chapter, the relevance of BIS systems has been evaluated and detailed, highlighting their application as a wearable alternative for various body measurement. This analysis not only underscores the advantages of BIS technology but also delineates the current landscape of its applications, offering insights into the specific measurement parameters considered in each use case.

The responsible for generating signals within the frequency range of interest is the Back-End stage which poses a significant challenge due to the wide range it must cover, requiring a robust and versatile design. On the other hand, the Front-End stage is an essential component in the measurement process, as it ensures the accurate acquisition of the signal response. For both stages, it is crucial to perform macromodeling to define the necessary specifications and validate the integrated operation of all blocks, ensuring system coherence and reliability.

Specifically, the performance of the instrumentation amplifier (IA) plays a decisive role in the overall accuracy and reliability of the Bio-Impedance System. Parameters such as adjustable gain range, bandwidth, and common-mode rejection are critical to achieving high-fidelity measurements under varying physiological conditions. Similarly, other essential blocks, such as signal generators, play a key role in enabling precise system operation and characterization, ensuring that the design and performance requirements are met.

# CHAPTER 2

# Signal Generation Proposals

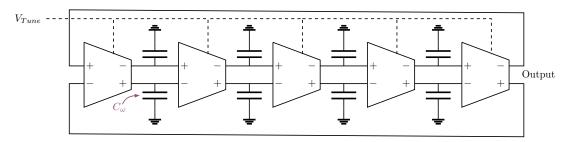

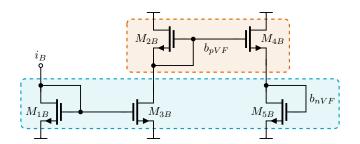

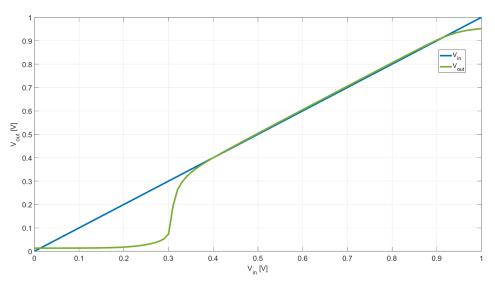

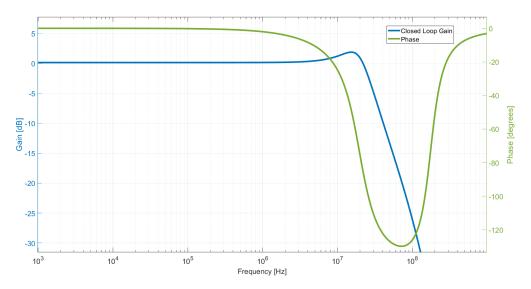

This chapter propose two solutions to signal generation within the dispersion range  $\beta$ . The first employs a QFGT-modified Ring Oscillator operating in Weak Inversion region offering kilohertz-range signals with a dual control via feedback factor  $\beta$  and the tuning voltage  $V_{Tune}$ . The second approaches the advantages of digital synthesis using a DDS with signal compression, reducing the sizing of the memory due to the discretization. Both methods ensure a compact design and reliable signal generation.

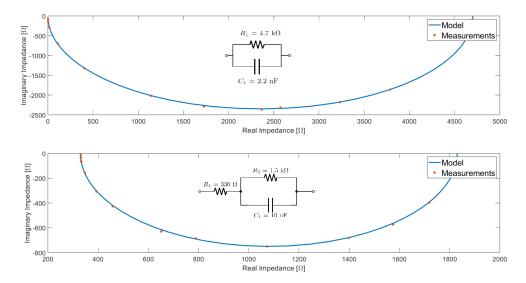

### 2.1 Oscillators

Oscillators are essential components in every electronic system and are responsible for generating periodic signals autonomously. They can be classified into non-resonant and resonant types. Non-resonant oscillators, such as delay lines and ring oscillators, do not rely on resonant elements, which are widely used in CMOS digital applications due to their simplicity [7]. Resonant oscillators, including crystal-based and LC tank types, leverage resonant circuits to ensure frequency stability, making them ideal for high-precision applications like telecommunications [40]. The choice between these oscillators depends on factors such as frequency stability and application-specific requirements.

Figure 2.1: Classification of the different types of oscillators

#### 2.1.1 Ring Oscillators

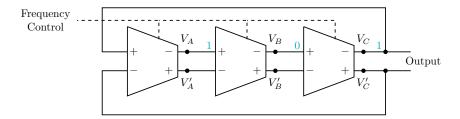

A ring oscillator is composed of an odd and even number (N) of open loop inverting amplifiers or delay cells (or stages) coupled in a positive feedback loop [6]. When an initial condition excites the Ring Oscillator, the propagation signal passes through the chain of N delay cells, resulting in a total delay of  $2Nt_p$  to complete one period ( $T_{osc}$ ), where  $t_p$  is the propagation time of a single delay cell, as shown in Equation 2.1.

$$f_{osc} = \frac{1}{T_{osc}} = \frac{1}{2Nt_p} \tag{2.1}$$

From the Equation 2.1, it is possible to denote that the oscillation frequency is determined by the propagation time  $t_p$  of each stage and the number of stages of the Ring Oscillator (denoted as N).

Figure 2.2: Basic topology of a three-stage ring oscillator

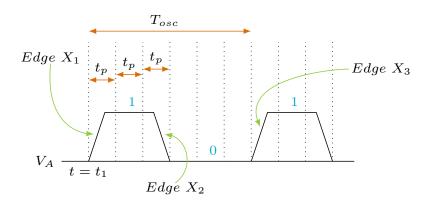

For every single cycle, there are downward and upward transition, and each delay cell's intrinsic propagation delay times, high-to-low  $(t_{PHL})$  and low-to-high  $(t_{PHL})$ , are associated with those transitions. Figure 2.3 shows the corresponding waveform of the 3-stages Ring Oscillator shown in Figure 2.2.  $V_A$  represents a differential signal oscillating between high and low logic levels and shows the three key points associated to each transition in time domain, denoted as **Edge**  $X_1$ , **Edge**  $X_2$ , and **Edge**  $X_3$ .

Figure 2.3: Time domain response of 3-stages RO of Figure 2.2. [6]

The total oscillation period, denoted as  $T_{\rm osc}$ , is the time required for the signal to return to its original state after propagating through the three stages. In figure 2.3,  $T_{\rm osc}$  is defined as the interval between two equivalent edges, for example, between **Edge**  $X_1$ and the subsequent edge after the signal has passed through the three stages.

# 2.1.2 Delay Cell Types

When comparing and classifying types of delay cells used in ring oscillators, several approaches are highlighted in recent research, focusing on key factors such as power consumption, phase noise, tuning range, and robustness against process variations.

- Inverter-based Delay Cells: Inverter-based delay cells are the most used in ROs due to their simplicity and efficiency in area. These cells introduce a delay through each inverter, determined by the load capacitance and channel resistance. These cells are well-suited for CMOS integration and are preferred in low-power applications where simplicity and cost-efficiency are critical [41] [42].

- **Dual-Delay-Path Cells:** These cells provide better control over the oscillation frequency by utilizing two separate delay paths. This architecture allows for more precise tuning of the oscillation frequency and offers improvements in phase noise performance. They are particularly useful in high-frequency applications where linearity and frequency stability are required [42].

- Differential Delay Cells: Differential delay cells are designed to minimize noise and increase frequency range. These cells are often used in high-performance RF circuits and systems due to their superior noise immunity and wide frequency tuning capabilities. Additionally, they offer better control over phase noise, making them ideal for communication systems [43] [41].

- Voltage-Controlled Delay Cells: Voltage-controlled delay cells are used in voltage-controlled oscillators (VCOs), where the oscillation frequency is adjusted by an external voltage. These cells are common in phase-locked loops (PLLs) and data converters, where a precise control of frequency is necessary. They are also advantageous in low-power designs requiring wide frequency tunability [41]

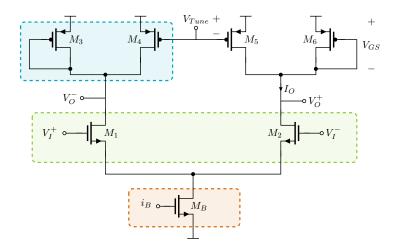

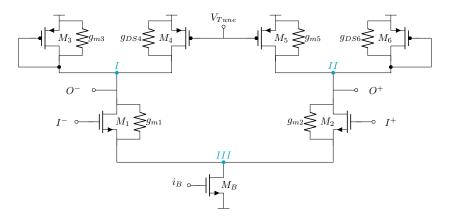

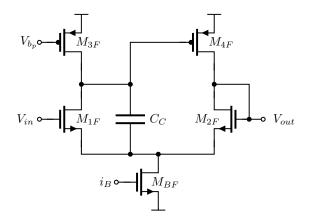

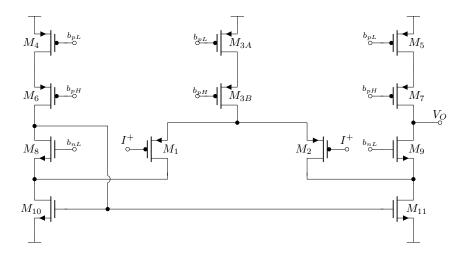

## 2.1.2.1 Maneatis Cell

The Maneatis cell was first introduced in 1993 [44]. It is a delay cell consisting of an nMOS differential amplifier  $(M_{1,2})$  with pMOS triode loads  $(M_{3,4})$  in parallel with a current source  $(M_{5,6})$ . By adjusting the control voltage  $(V_{Tune})$ , transistors  $M_{5,6}$ modify the total current through the differential pair, thereby allowing the oscillation frequency to increase or decrease.

A detailed description of the function of each stage indicated in Figure 2.4 is provided below:

- $M_B$  Transistor: operates as the bias transistor of the delay cell (also known as the Tail Current).

- $M_1$  and  $M_2$  Transistors: these transistors function as the input differential pair.

- $M_3$  and  $M_4$  Transistors: they serve as the load for one of the output branches, where  $M_3$  is a transistor connected as a diode, and  $M_4$  acts as a voltage-controlled current source regulated by  $V_{Tune}$ .

Figure 2.4: Basic structure of the Maneatis Cell (**Topology A**)

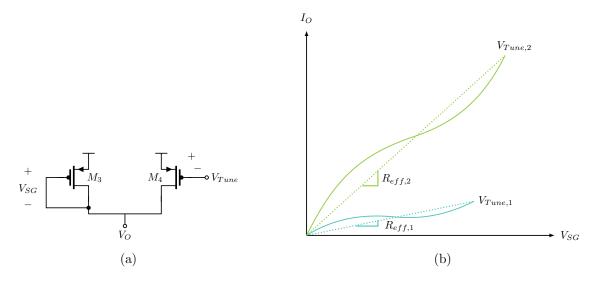

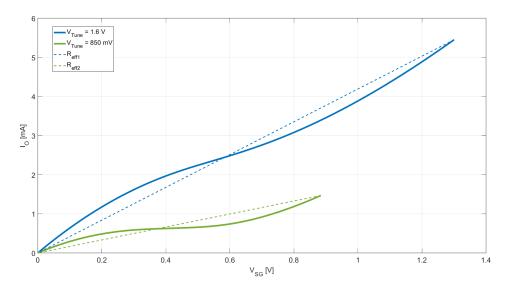

This cell is referred to as symmetric load because the current-to-control voltage relationship is symmetric with respect to the midpoint of the voltage excursion, as shown in Figure 2.5. Figure 2.5 illustrates the ideal I-V characteristics of symmetric loads at low (labeled as I in Figure 2.5b) and mid-range (labeled as II) bias voltages. With the upper supply acting as the maximum swing limit, the lower swing limit is symmetrically positioned at the bias level of the pMOS transistor,  $V_{Tune}$ . The dashed lines represent the effective resistance of the load and highlight the symmetry of their I-V characteristics.

Figure 2.5: DC characterization of the Maneatis Cell. a) Load structure b) Characteristic I-V curve

The delay time generated by the Maneatis Cell is primarily determined by the capacitive and resistive elements of the load. Thus, the delay of the cell is given by expression 2.2.

$$\tau = R_{eff} \cdot C_{eff} \tag{2.2}$$

Where  $R_{eff}$  is the inverse of the transconductance and can be easily obtained from its definition, as shown in expression 2.3

$$g_m = \frac{\partial i_D}{\partial V_{GS}} \tag{2.3}$$

Due to the applications of ring oscillators involve high frequencies, it is very common for the transistors in the delay cells to operate in strong inversion (also known as the saturation region). Therefore, the Drain Current  $(I_D)$  is expressed as

$$I_D = \frac{1}{2} \mu_{n,p} C_{OX} \frac{W}{L} (V_{GS} - V_{Th})^2$$

(2.4)

Therefore, the transconductance is obtained by applying 2.3 to 2.4, and specifically for the pMOS load transistors, it results in Equation 2.5

$$g_m = \mu_p C_{OX} \frac{W}{L} (V_{GS} - V_{Th}) \tag{2.5}$$

The AC gain of the cell is given by the Equation

$$A_V = \frac{g_{m1}}{g_{m3} + g_{DS1} + g_{DS3} + g_{DS4}}$$

(2.6)

The ring oscillator configuration implies that the delay cell uses a load with these characteristics. Therefore, the circuit bandwidth will be determined by

$$\omega_O = \frac{g_{m3} + g_{DS1} + g_{DS3} + g_{DS4}}{C_{GS1} + C_{GS3} + C_{DB1} + C_{DB3} + C_{DB4}}$$

(2.7)

From expressions 2.6 and 2.7, it is possible to obtain the gain-bandwidth product, as shown in the equation

$$\omega_T = \frac{g_{m1}}{C_{GS1} + C_{GS3} + C_{DB1} + C_{DB3} + C_{DB4}}$$

(2.8)

#### 2.1.3 DPI/SFG Analysis

The systematic method of circuit and system analysis, Driving Point Impedance / Signal Flow Graph, proposed by [45], allows using signal flow graphs as a visual and mathematical tool to model their interaction, enabling the decomposition and simplification of complex circuit analysis. The driving-point impedance methodology was first introduced by [46]. This method addresses the problem by dividing it into two more manageable sub-circuits, which are later synthesized to construct the complete solution of the original system.

• Short Circuit Current: An AC ground short is imposed at the desired output node "x", and the current that flows through this short is calculated, commonly referred to as the short-circuit current,  $I_{scx}$ .

• Driving Point Impedance: In this sub-circuit, the equivalent impedance (known as the "Driving Point Impedance") seen from the node of interest "x"  $(DPI_x)$  is calculated.

Therefore, the voltage seen at node "x" can be easily calculated as

$$V_X = I_{SC,x} \cdot DPI_x \tag{2.9}$$

In this work, the DPI/SFG method has been applied to the analysis of the Maneatis delay cell. To simplify the analysis, the output resistances involved in each of the transistors composing the topology described in Figure 2.6 are considered.

Figure 2.6: Resistances associated with the transistors for the DPI/SFG analysis

The impedance seen at node I is described as detailed in Equation 2.10, by considering that the contribution due to  $g_{DS3}$  and  $g_{DS1}$  is negligible.

$$DPI_1 = (g_{m3} + g_{DS4})^{-1} = r_{O1}$$

(2.10)

The short-circuit current at the same node is given by the transconductance of the input differential pair as is shown in 2.11.

$$I_{SC,1} = V_{III}(g_{DS1} + g_{m1}) - V_{I^+}g_{m1}$$

(2.11)

Due to the symmetry of the topology, the short-circuit current (and impedance) seen at node II is analogous to Equations 2.11 and 2.10, respectively.

$$DPI_2 = (g_{m6} + g_{DS5})^{-1} = r_{O2}$$

(2.12)

$$I_{SC,2} = V_{III}(g_{DS2} + g_{m2}) - V_{I^-}g_{m2}$$

(2.13)

Finally, the total short-circuit current at node III is the sum of the contributions from both branches; thus, the total current is given by Equation 2.14.

$$I_{SC,3} = V_{I^+} g_{m1} + V_{I^-} g_{m2} \tag{2.14}$$

The impedance at node III is described in Equation 2.15.

$$DPI_3 = (g_{DS1} + r_O^{-1})^{-1} \tag{2.15}$$

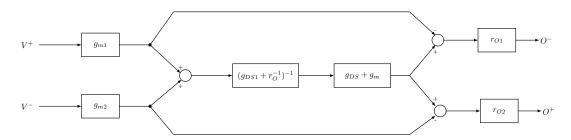

Expressions 2.10 - 2.15 establish the corresponding Signal Flow Graph (SFG) shown in Figure 2.7. To illustrate the relationship between the equations and the SFG, each current (or voltage) generation is marked by its respective expression: for instance,  $V_{I+}g_{m1}$  and  $V_{I-}g_{m2}$  are indicated in blue, and according to Equation 2.14, both are represented as a summation point whose result is  $I_{SC3}$ .

Figure 2.7: Resulting SFG from the DPI analysis of the Maneatis Cell (Topology A)

The SFG allows to describe the following points:

- Differential Input  $(V^+, V^-)$ : The signals  $V^+$  and  $V^-$  pass through transistors  $M_1$  and  $M_2$  with transconductance gains of  $g_{m1}$  and  $g_{m2}$ , respectively.

- Short-Circuit Current  $(I_{SC})$ : A short-circuit current is generated at node I, which is influenced by the transconductance terms and the  $g_{DS}$  conductances, in addition to the output resistance  $r_o$ .

- Impedance  $Z_{III}$ : Node III demonstrates how the circuit combines differential conductance and the impedances  $g_{DS} + g_m$ . This node is crucial for determining the frequency response of the circuit.

- Differential Output  $(V_O^+, V_O^-)$ : The signals  $O^+$  and  $O^-$  are obtained through the load resistances  $r_{o1}$  and  $r_{o2}$ , which help stabilize the signals and minimize distortion.

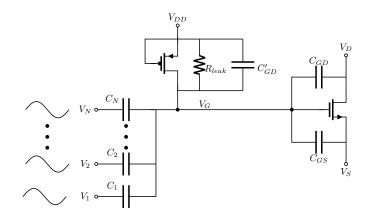

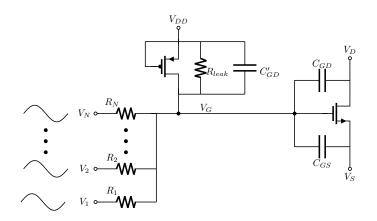

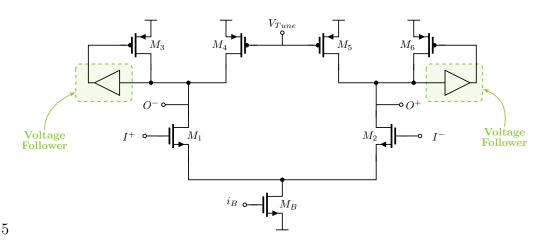

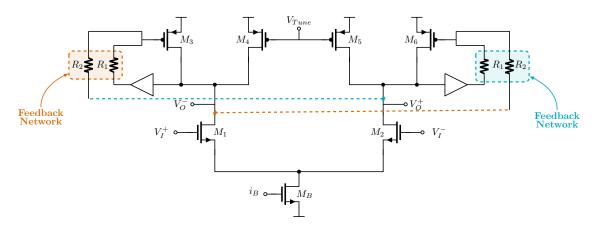

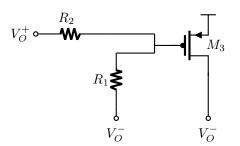

# 2.1.4 Quasi-Floating Gate Transistors

The structure of the Quasi-Floating Gate Transistor (QFGT) is shown in Figure 2.8. In this modification, the gate of the transistor functions as a weighted summation point, dependent on the weighting of the gate capacitors. This topology is called with the prefix "Quasi" because there is an nMOS (or pMOS) transistor connected to  $V_{DD}$  (or  $V_{SS}$ ) through a reverse-biased diode-connected transistor, which acts as a large-value resistor, thus maintaining the operating point.

Figure 2.8: Structure of a Quasi-Floating Gate Transistor (QFGT) capacitively coupled

The voltage at the gate of the QFGT  $(V_G)$  is described in Equation 2.16, where  $C_{Total}$  is the total capacitance seen at the gate, primarily composed of the parasitic capacitances of the QFGT and the capacitances associated with the signals as shown in Equation 2.17.

$$V_G = \frac{sR_{leak}C_{Total}}{1 + sR_{leak}C_{Total}}$$

(2.16)

$$C_{Total} = \sum_{i=1}^{N+1} C_i + C_{GS} + C_{GD} + C'_{GD}$$

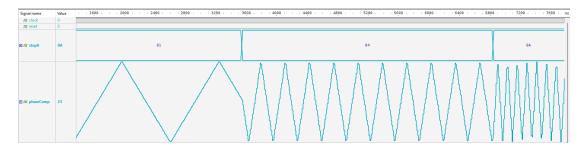

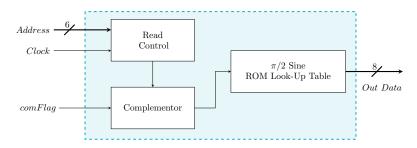

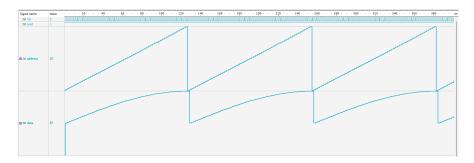

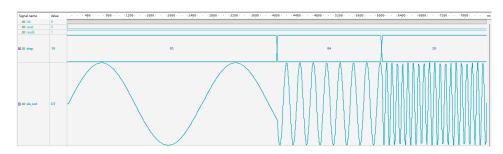

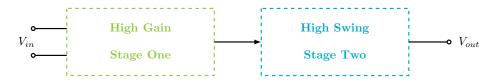

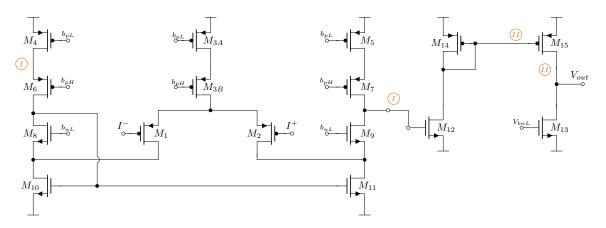

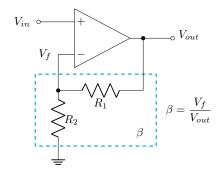

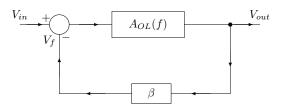

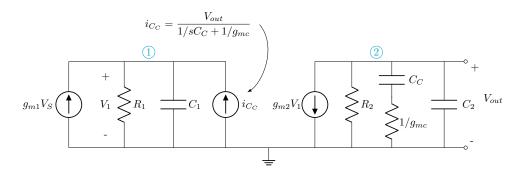

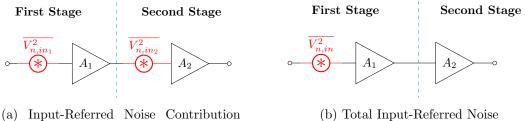

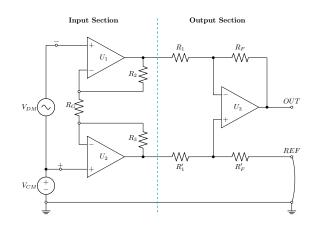

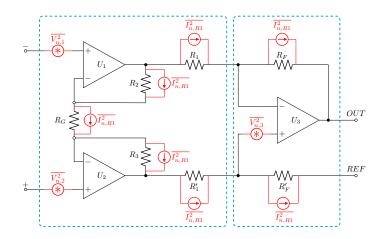

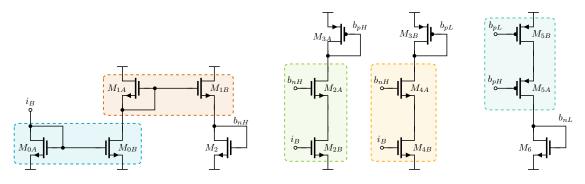

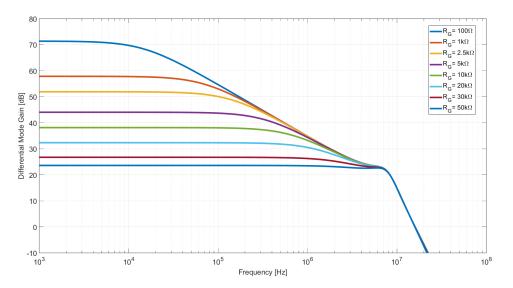

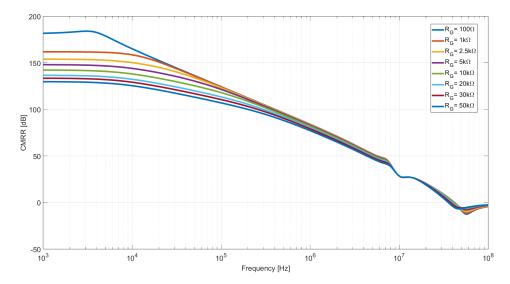

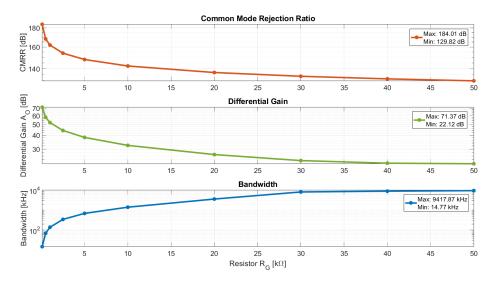

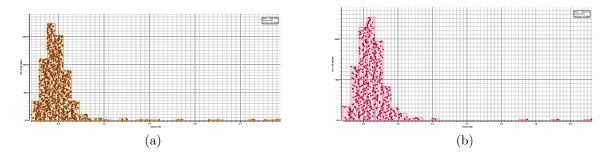

(2.17)