## Diseño Embebido de Sistemas Caóticos de Orden Fraccional

por

## MC Daniel Clemente López

Tesis sometida como requisito parcial para obtener el grado de

## DOCTORADO EN CIENCIAS EN LA ESPECIALIDAD DE ELECTRÓNICA

en el

Instituto Nacional de Astrofísica, Óptica y Electrónica

> Enero 2025 Tonantzintla, Puebla

Supervisada por:

Dr. José de Jesús Rangel MagdalenoInvestigador Titular INAOEDr. Jesús Manuel Muñoz PachecoInvestigador Titular BUAP

**©INAOE 2025**

El autor otorga al INAOE el permiso de reproducir y distribuir copias en su totalidad o en partes de esta tesis

## Diseño Embebido de Sistemas Caóticos de Orden fraccional

Tesis de Doctorado

#### Por:

## MC Daniel Clemente Lopez

#### ASESORES:

Dr. José de Jesús Rangel Magdaleno (INAOE) Dr. Jesús Manuel Muñoz Pacheco (BUAP)

Instituto Nacional de Astrofísica Óptica y Electrónica Coordinación de Electrónica

A Dios, por ser mi guia y fortalexa en cada paso. A mi familia, por ser mi mayor motor y refugio. A mi padre Gustavo y a mi madre Maria, por su amor incondicional y sabiduria infinita. A mi hermano Gustavo, cuyo apoyo y confianza han sido fundamentales en este camino.

A mi hijo Daniel, quien es mi mayor inspiración y motivo para seguir adelante. Su presencia llena mi vida de alegría y propósito.

## Agradecimientos

En primera instancia, agradezco al Instituto Nacional de Astrofísica, Óptica y Electrónica (INAOE) por brindarme el apoyo necesario durante mi estancia en el Doctorado en Ciencias en Electrónica.

Agradezco profundamente a mis asesores de tesis, el Dr. José de Jesús Rangel Magdaleno y el Dr. Jesús Manuel Muñoz Pacheco, quienes con su invaluable orientación, conocimientos y compromiso me ayudaron a culminar este trabajo.

Extiendo mi agradecimiento al jurado de tesis, compuesto por la Dra. Luz del Carmen Gómez Pavón, el Dr. José Hugo Barrón Zambrano, el Dr. Juan Manuel Ramírez Cortés, el Dr. Israel Cruz Vega y el Dr. Óscar Martínez Fuentes. Sus observaciones y comentarios enriquecieron significativamente el desarrollo de este trabajo.

Agradezco al Consejo Nacional de Ciencia y Tecnología (CONACYT) por el apoyo brindado a través de la beca doctoral con CVU No. 859036, la cual fue fundamental para la realización de mis estudios.

## Resumen

Este trabajo presenta el desarrollo y la implementación de sistemas caóticos de orden fraccional utilizando un método de descomposición por tramos lineales (PWL-DM) y una plataforma embebida basada en la arquitectura RISC-V. La investigación parte de una revisión detallada de los operadores fraccionales de clase F<sub>1</sub>, con énfasis en los operadores de Caputo y Grünwald-Letnikov, que permiten modelar sistemas dinámicos de orden fraccional preservando propiedades críticas como la memoria y la herencia.

A lo largo del proyecto, se analizaron métodos de solución como FDA, GL y ADM, identificando sus limitaciones en aplicaciones prácticas. Esto condujo al desarrollo del método PWL-DM, diseñado para resolver sistemas PWL de orden fraccional que presentan atractores caóticos de múltiples enrollamientos. El método PWL-DM ofrece una estructura eficiente basada en operadores lineales y vectores constantes, lo que facilita su aplicación en sistemas caóticos complejos al permitir una representación precisa de los atractores caóticos mediante una partición estructurada del espacio fase.

El trabajo experimental incluyó la implementación de estos sistemas caóticos en una FPGA mediante la síntesis estándar, y posteriormente en un sistema embebido basado en RISC-V. La implementación en FPGA aprovechó las capacidades de cómputo paralelo y reconfiguración de hardware para alcanzar un rendimiento computacional elevado, aunque cada sistema caótico requirió de un diseño de arquitectura específica. En contraste, el sistema embebido basado en RISC-V se caracteriza por su flexibilidad, permitiendo manejar diferentes sistemas caóticos sin necesidad de modificar el hardware, siempre y cuando estos puedan ser representados en una palabra de 32 bits. Además, el sistema embebido demostró una eficiencia energética superior, optimizando el uso de recursos mediante un protocolo de comunicación interno.

Los resultados obtenidos confirman que el diseño embebido basado en RISC-V,

IV RESUMEN

en combinación con el método PWL-DM, proporciona una solución escalable y adaptable para la implementación de sistemas caóticos de orden fraccional. Este enfoque presenta un balance entre eficiencia energética, rendimiento computacional y flexibilidad, lo cual lo convierte en una opción viable para aplicaciones en modelado de sistemas dinámicos y seguridad. Este trabajo sienta las bases para futuras investigaciones en el campo de sistemas caóticos y sus aplicaciones en plataformas embebidas, contribuyendo al avance de la ingeniería en el análisis y control de sistemas dinámicos complejos.

## Tabla de Contenido

| Agradecimientos                                            | ]   |

|------------------------------------------------------------|-----|

| Resumen                                                    | III |

| ndice de Figuras v                                         | III |

| ndice de Tablas                                            | X   |

| . Introducción                                             | 2   |

| 1.0.1. Antecedentes                                        | 4   |

| 1.0.2. Motivación y Justificación                          | 6   |

| 1.0.3. Planteamiento del Problema                          | 8   |

| 1.0.4. Hipótesis                                           | 9   |

| 1.0.5. Objetivo General                                    | 9   |

| 1.0.6. Objetivos Particulares                              | 9   |

| 1.0.7. Metodología                                         | 10  |

| 1.1. Alcance de la Metodología y Resultados Preliminares   | 12  |

| 1.2. Organización del documento                            | 13  |

| . Análisis de Derivadas de Orden Fraccional                | 15  |

| 2.1. Derivadas de Orden Fraccional                         | 15  |

| 2.2. Métodos de solución para sistemas de orden fraccional | 18  |

| 2.2.1. Aproximación en el dominio de la frecuencia         | 19  |

| 2.2.1.1. Alcance y limitaciones de FDA para la implementa- |     |

| ción de sistemas caóticos de orden fraccional              | 21  |

| 2.2.2. Algoritmo numérico de Adams-Bashforth-Moulton       | 23  |

|    |      |         | 2.2.2.1.   | Alcance y limitaciones del método ABM para la im-          |    |

|----|------|---------|------------|------------------------------------------------------------|----|

|    |      |         |            | plementación de sistemas caóticos de orden fraccional.     | 24 |

|    |      | 2.2.3.  | Algoritm   | no de Grünwald-Letnikov                                    | 25 |

|    |      |         | 2.2.3.1.   | Alcance y limitaciones del enfoque numérico GL pa-         |    |

|    |      |         |            | ra la implementación de sistemas caóticos de orden         |    |

|    |      |         |            | fraccional                                                 | 27 |

|    |      | 2.2.4.  | Método     | de Descomposición de Adomian                               | 28 |

|    |      |         | 2.2.4.1.   | Alcance y limitaciones del enfoque ADM para la im-         |    |

|    |      |         |            | plementación de sistemas caóticos de orden fraccional      | 30 |

|    | 2.3. | Desem   | peño de l  | os métodos de implementación de sistemas caóticos de       |    |

|    |      | orden   | fraccional | l                                                          | 34 |

| 3. | For  | mulaci  | ón del I   | Método de Descomposición PWL para Sistemas                 |    |

|    | Caó  | ticos d | le Order   | Fraccional                                                 | 41 |

|    | 3.1. | Métod   | lo de desc | omposición propuesto (enfoque PWL-DM)                      | 42 |

|    | 3.2. | Utiliza | ando PW    | L-DM para resolver sistemas caóticos PWL de orden          |    |

|    |      | fraccio | onal       |                                                            | 48 |

|    |      | 3.2.1.  |            | 1: Demostración paso a paso para un sistema caótico        |    |

|    |      |         | PWL de     | orden fraccional de 2 enrollamientos                       | 48 |

|    |      | 3.2.2.  |            | 2: Sistema caótico de múltiples enrollamientos de or-      |    |

|    |      |         | den frac   | cional                                                     | 52 |

| 4. |      |         | experin    |                                                            | 58 |

|    | 4.1. |         |            | Estadar para la Síntesis e Implementación en FPGA de       |    |

|    |      |         |            | cos de Orden Fraccional                                    | 58 |

|    |      | 4.1.1.  |            | del sistema caótico PWL de orden fraccional con 2 en-      |    |

|    |      |         | rollamie   | ntos                                                       | 59 |

|    |      |         | 4.1.1.1.   | Estimación de la palabra digital                           | 60 |

|    |      |         | 4.1.1.2.   | Simulación numérica en punto fijo                          | 61 |

|    |      |         | 4.1.1.3.   | Síntesis del sistema utilizando lenguaje de descripción    |    |

|    |      |         |            | de hardware                                                | 62 |

|    |      | 4.1.2.  | Síntesis   | del sistema caótico PWL de orden fraccional con $4\times4$ |    |

|    |      |         |            | iientos                                                    | 64 |

|    | 4.2. |         |            | lo basado en RISC-V para la implementación de siste-       |    |

|    |      | mas ca  | aóticos de | orden fraccional                                           | 67 |

|           | 4.2.1.     | Arquited | ctura del Conjunto de Instrucciones (ISA) RISC-V      | 67  |

|-----------|------------|----------|-------------------------------------------------------|-----|

|           |            | 4.2.1.1. | Codificación de Instrucciones en RISC-V               | 69  |

|           |            | 4.2.1.2. | Registros                                             | 75  |

|           | 4.2.2.     | Diseño o | le la Microarquitectura RISC-V                        | 76  |

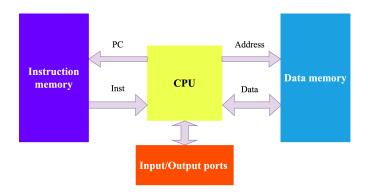

|           |            | 4.2.2.1. | Arquitectura Harvard para la Configuración de Me-     |     |

|           |            |          | morias                                                | 76  |

|           | 4.2.3.     | Ciclo de | Instrucción en la Microarquitectura Propuesta         | 78  |

|           | 4.2.4.     | Validaci | ón del sistema embebido basado en RISC-V              | 83  |

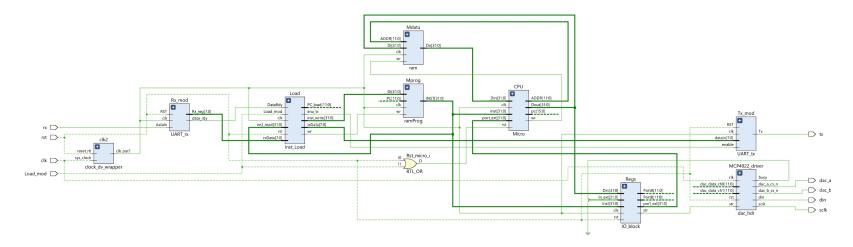

|           |            | 4.2.4.1. | Diseño en FPGA del sistema embebido basado en         |     |

|           |            |          | RISC-V                                                | 83  |

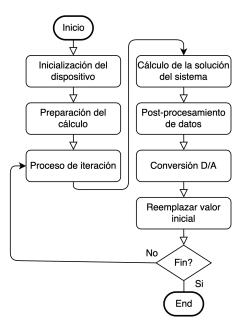

|           |            | 4.2.4.2. | Implementación de sistemas caóticos de orden fraccio- |     |

|           |            |          | nal en el sistema embebido basado en RISC-V           | 86  |

| <b>5.</b> | Análisis d | e Result | ados                                                  | 89  |

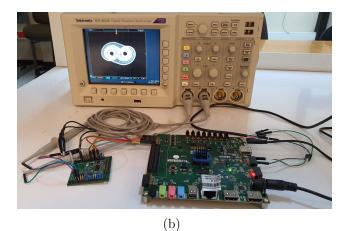

|           | 5.0.1.     | Configur | ración experimental                                   | 89  |

|           | 5.0.2.     | Uso de l | nardware                                              | 91  |

|           | 5.0.3.     | Consum   | o de Energía                                          | 93  |

|           | 5.0.4.     | Rendim   | iento Computacional                                   | 95  |

| 6.        | Conclusion | nes      |                                                       | 97  |

| Aj        | péndices   |          |                                                       | 101 |

| Bi        | bliografía |          |                                                       | 109 |

# Índice de Figuras

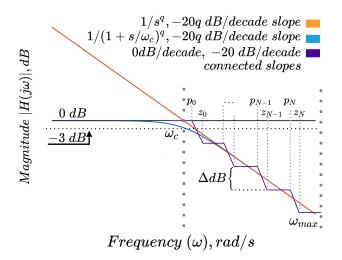

| 2.1. | Comparación de diagramas de Bode entre $1/s^q$ y $H(s)$ utilizando el método de Charef                                                                                                                                                                                                                                                                                                                        | 21 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

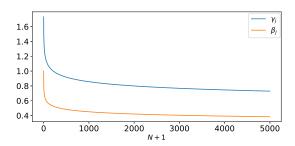

| 2.2. | Evolution of the weights $\gamma_{j,N+1}$ and $\beta_{j,N+1}$ in the ABM algorithm with $q=0.9$ and $N=5000.$                                                                                                                                                                                                                                                                                                 | 24 |

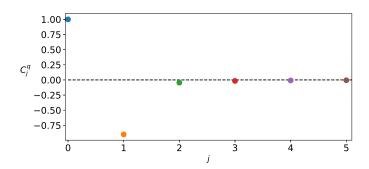

| 2.3. | Valores numéricos de los coeficientes binomiales (2.2.12) en $q=0.9$ y $j=0,1,\ldots 5.$                                                                                                                                                                                                                                                                                                                      | 26 |

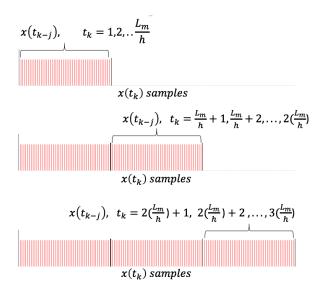

| 2.4. | Una gestión típica de datos para resolver sistemas caóticos de orden fraccional con la aproximación SMP-GL. Los corchetes denotan la longitud de la memoria utilizada para calcular la solución $x(t_k)$ con las muestras anteriores $x(t_{k-j})$ almacenadas durante todo el tiempo de simulación                                                                                                            | 27 |

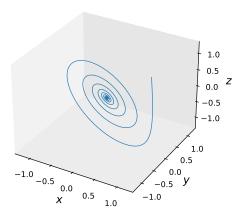

| 2.5. | Diagrama de fases del sistema fraccional tridimensional (2.2.20) utilizando el ADM con $h=0.01$ y condiciones iniciales $[x(t_0),y(t_0),z(t_0)]=[1,0,1].$                                                                                                                                                                                                                                                     | 33 |

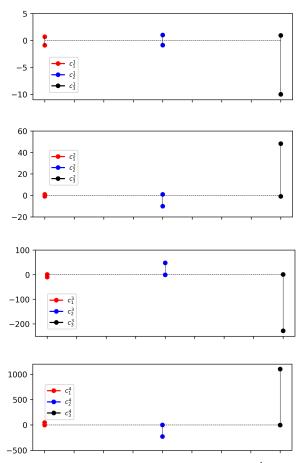

| 2.6. | Evolución del comportamiento de los coeficientes ADM $c_p^k$ ( $k=1,\ldots,4;\ p=1,2,3$ ) para el sistema de orden fraccional (2.2.20)                                                                                                                                                                                                                                                                        | 33 |

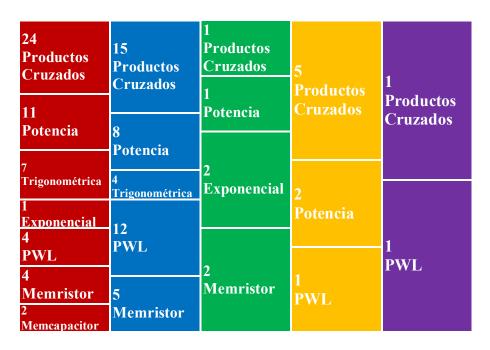

| 2.7. | Gráfico de mapa de colores ponderado de las publicaciones existentes sobre implementaciones embebidas y no embebidas de sistemas caóticos de orden fraccional. Los colores indican la <i>Plataforma</i> utilizada: ARM (rojo), DSP (azul), FPGA conforme (morado); y estos, a su vez, se subdividen en cuadros que denotan el número de publicaciones asociadas con los diferentes <i>métodos de solución</i> | 37 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 2.8.  | Gráfico de mapa de colores ponderado de las publicaciones existentes sobre implementaciones embebidas y no embebidas de sistemas caóticos de orden fraccional. Los colores indican el <i>Método de Solución</i> utilizado: ADM (rojo), aproximación GL (azul), ADM conforme (verde), FDA |    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | (amarillo) y ABM (morado); y estos, a su vez, se subdividen en cuadros que denotan el número de publicaciones asociadas con los diferentes <i>Tipos de Funciones No Lineales</i>                                                                                                         | 37 |

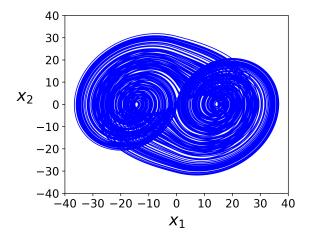

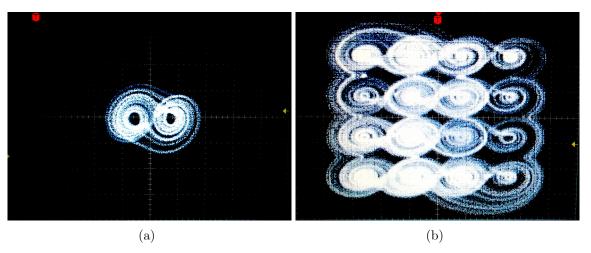

| 3.1.  | Simulación numérica del atractor caótico de 2 enrollamientos con un orden fraccional $q=0.92$ utilizando PWL-DM                                                                                                                                                                          | 52 |

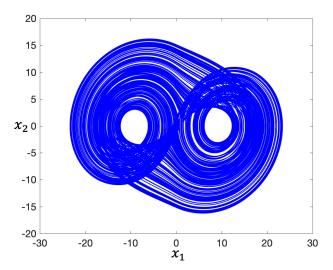

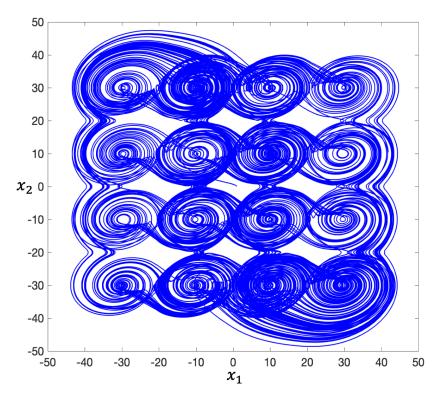

| 3.2.  | Simulación numérica del atractor caótico de orientación 2D de $4 \times 4$ enrollamientos con un orden fraccional $q=0.93.$                                                                                                                                                              | 57 |

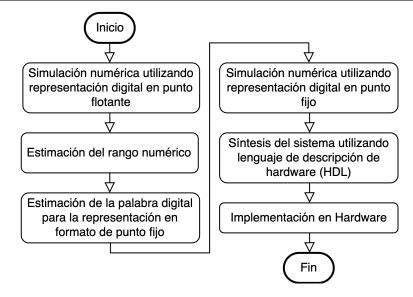

| 4.1.  | Procedimiento estándar para implementaciones en FPGA de sistemas caóticos de orden entero y orden fraccional                                                                                                                                                                             | 59 |

| 4.2.  | Simulación con punto fijo del atractor caótico de 2 enrollamientos con un orden fraccional $q=0.92$ utilizando PWL-DM                                                                                                                                                                    | 61 |

| 4.3.  | Esquemas RTL del sistema caótico PWL de orden fraccional con 2 enrollamientos en FPGA                                                                                                                                                                                                    | 62 |

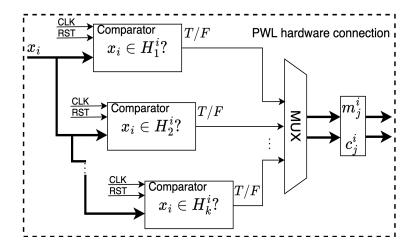

| 4.4.  | Interconexión de hardware de alto nivel para las funciones PWL $f_i(\cdot)$ (3.1.4)                                                                                                                                                                                                      | 62 |

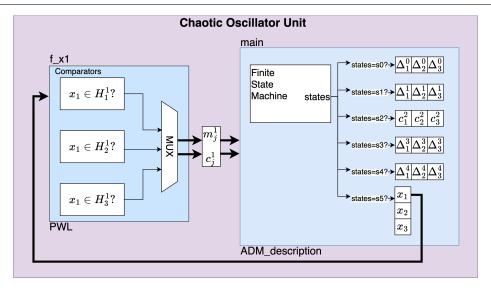

| 4.5.  | Diagrama de bloques del mecanismo de generación del atractor caótico de 2 enrollamientos                                                                                                                                                                                                 | 63 |

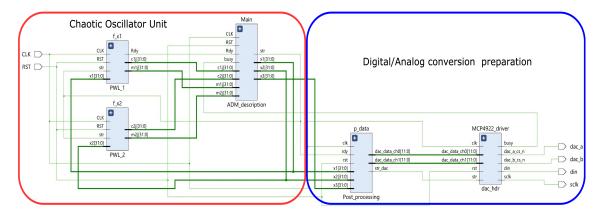

| 4.6.  | Esquemas RTL del sistema caótico PWL de orden fraccional con $4\times4$ enrollamientos en FPGA                                                                                                                                                                                           | 65 |

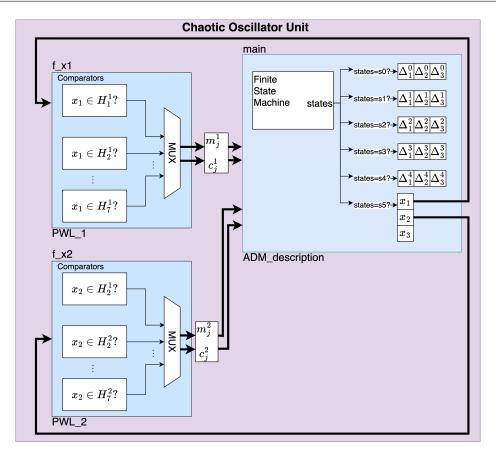

| 4.7.  | Diagrama de bloques del mecanismo de generación del atractor caótico de 4x4 enrollamientos                                                                                                                                                                                               | 66 |

| 4.8.  | Diagrama de bloques de la arquitectura de Harvard                                                                                                                                                                                                                                        | 77 |

| 4.9.  | Ciclo de instrucción en la microarquitectura propuesta                                                                                                                                                                                                                                   | 82 |

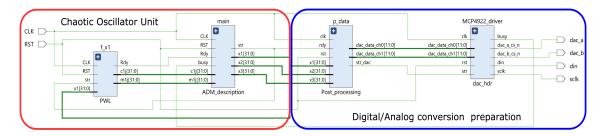

| 4.10. | Esquemático RTL de la implementación del sistema embebido basdo en RISC-V                                                                                                                                                                                                                | 85 |

| 4.11. | Procedimiento para implementaciones de sistemas caóticos de orden fraccional en el diseño embebido propuesto                                                                                                                                                                             | 86 |

X ÍNDICE DE FIGURAS

| 5.1. | Configuración experimental para las implementaciones de sistemas              |    |

|------|-------------------------------------------------------------------------------|----|

|      | caóticos de orden fraccional. (a) Configuración experimental utilizando       |    |

|      | la síntesis estandar de sistemas caóticos y (b) Configuración experimen-      |    |

|      | tal utilizando el diseño embebido basado en RISC-V                            | 90 |

| 5.2. | Resultados experimentales de la implementación en FPGA basada en              |    |

|      | la síntesis estándar de sistemas caóticos, (a) retrato de fase $x_1, x_2$ del |    |

|      | sistema del sistema caótico PWL de orden fraccional con 2 enrolla-            |    |

|      | mientos, (b) retrato de fase $x_1, x_2$ del sistema caótico PWL de orden      |    |

|      | fraccional con $4 \times 4$ enrollamientos                                    | 91 |

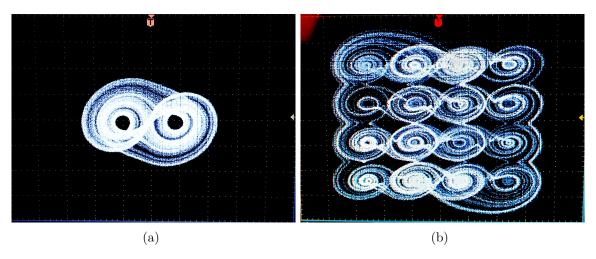

| 5.3. | Resultados experimentales de la implementación realizada el sistema           |    |

|      | embebido basado en RISC-V, (a) retrato de fase $x_1, x_2$ del sistema         |    |

|      | del sistema caótico PWL de orden fraccional con 2 enrollamientos, (b)         |    |

|      | retrato de fase $x_1, x_2$ del sistema caótico PWL de orden fraccional con    |    |

|      | $4 \times 4$ enrollamientos                                                   | 92 |

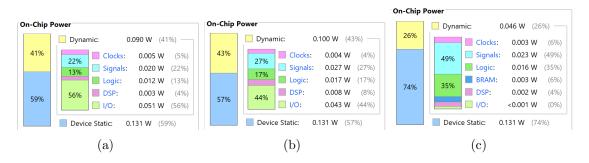

| 5.4. | Consumo de energía de la implementación de sistemas caóticos de               |    |

|      | orden fraccional. (a) Síntesis estándar 2 enrollamientos, (b) síntesis        |    |

|      | estándar $4\times 4$ enrollamientos y (c) Implementación en el sistema em-    |    |

|      | bebido basado en RISC-V                                                       | 95 |

## Índice de Tablas

| es embebidas y no embebidas de SCOF                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| avactavísticas da disaña ambabida y na ambabida                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| aracteristicas de diseño embebido y no embebido                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ango numérico de los coeficientes ADM $c_p^k$ $(k=1,\ldots,4;\ p=1,2,3)$            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ango numérico de los términos ADM $\frac{h^{kq}}{\Gamma(kq+1)}$ con $q=0.9$ para el |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| stema de orden fraccional (2.2.20)                                                  | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| omparación de rendimiento entre los métodos de solución ABM, GL                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ADM                                                                                 | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| rabajos que reportan implementaciones de sistemas caóticos de orden                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| accional en plataformas FPGA                                                        | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| rabajos reportan implementaciones de sistemas caóticos de orden                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| accional en plataformas DSP                                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| rabajos reportan implementaciones embebidas de sistemas caóticos                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| e orden fraccional en plataformas ARM                                               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| tilización de hardware de las implementaciones en FPGA de sistemas                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| aóticos de orden fraccional                                                         | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| omparación del rendimiento computacional entre las diferentes im-                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| lementaciones de sistemas caóticos de orden fraccional                              | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                     | ango numérico de los coeficientes ADM $c_p^k$ $(k=1,\ldots,4;\ p=1,2,3)$ ensiderando el sistema de orden fraccional $(2.2.20)$ .  ango numérico de los términos ADM $\frac{h^{kq}}{\Gamma(kq+1)}$ con $q=0.9$ para el stema de orden fraccional $(2.2.20)$ .  comparación de rendimiento entre los métodos de solución ABM, GL ADM.  cabajos que reportan implementaciones de sistemas caóticos de orden accional en plataformas FPGA.  cabajos reportan implementaciones de sistemas caóticos de orden accional en plataformas DSP.  cabajos reportan implementaciones embebidas de sistemas caóticos e orden fraccional en plataformas ARM.  tilización de hardware de las implementaciones en FPGA de sistemas óticos de orden fraccional. |

1 ÍNDICE DE TABLAS

### Capítulo 1

## Introducción

La teoría del **caos** es una rama de las matemáticas que se dedica al estudio de comportamientos complejos que emergen en sistemas dinámicos no lineales, conocidos como sistemas caóticos [1]. Esta teoría se enfoca en fenómenos como la extrema sensibilidad a las condiciones iniciales y a los parámetros del sistema, transitividad, y la existencia de un conjunto denso de órbitas periódicas [2]. Los sistemas caóticos se pueden encontrar en casi todos los campos de la ciencia e ingeniería, como la astrofísica [3], mecánica [4], economía [5], comunicaciones seguras [6], criptografía [7], robótica [8] y control [9].

En la literatura se reporta dos formas para clasificar a los sistemas caóticos en cuanto a su cuenca de atracción [10]. Por un lado, los sistemas caóticos con atractores autoexcitados son aquellos cuya cuenca de atracción intersecta con un equilibrio inestable. Por otro lado, los sistemas caóticos con atractores ocultos tienen una cuenca de atracción que no intersecta con ningún vecindario abierto de los equilibrios. Desde que se encontró el primer atractor oculto en el circuito clásico de Chua [11], se ha prestado mucha más atención a este nuevo tipo de atractor. En primer lugar, la dinámica de los atractores ocultos es altamente compleja de analizar, ya que pueden llevar a comportamientos inesperados. Por ejemplo, fenómenos complejos como la "Multiestabilidadz la "Multiestabilidad Extrema" son propensos a aparecer en sistemas dinámicos con atractores ocultos [12]. Los fenómenos de multiestabilidad se refieren a cuando dos o más atractores diferentes coexisten bajo los mismos parámetros, mientras que la multiestabilidad extrema ocurre cuando coexisten infinitos atractores. Debido a que estos fenómenos dependen de las condiciones iniciales para cambiar de un atractor a otro totalmente diferente, se pueden usar como una fuente adicional de aleatoriedad para aplicaciones potenciales. Por ejemplo, podrían mejorar el rendimiento en criptografía [13] y comunicaciones seguras [14].

En relación con el estudio de sistemas caóticos, el cálculo fraccional es un tema que ha adquirido un gran interés en tiempos recientes. Este se refiere a la generalización de integrales y derivadas de orden entero a órdenes arbitrarios. El cálculo fraccional es un área de las matemáticas propuesta hace más de 300 años, pero solo recientemente ha emergido como un tema de alto interés en investigación debido a sus características superiores para el modelado de sistemas complejos. Por ejemplo, las definiciones del cálculo fraccional poseen propiedades de memoria que permiten una descripción más precisa de varios fenómenos físicos en comparación con sus contrapartes de orden entero. (por ejemplo, véase: procesos biológicos [15], economía [16], mecánica [17], electrónica [18], fenómenos sociales [19]). De esta manera, los sistemas caóticos de orden fraccional (SCOF) pueden considerarse como la capa de interacción que unifica las ramas matemáticas del caos y el cálculo de orden fraccional. A conocimiento de los autores, el sistema de Chua propuesto por Hartley et al. [20], puede considerarse el primer manuscrito que reportó un sistema caótico con derivadas fraccionales. Desde entonces, un número creciente de sistemas caóticos de orden fraccional se han reportado en la literatura, incluidos los sistemas clásicos de Lorenz [21], Chen [22], y Duffing [23].

Es importante remarcar que la dimensión efectiva en sistemas dinámicos tridimensionales de orden fraccional dada por  $\sum_{i=1}^{n=3} q_i$ , con  $n \ge q_i \in (0,1]$  siendo el número de variables pseudo-estado y el orden fraccional, respectivamente, puede ser menor que tres. Sin embargo, sorprendentemente, pueden generar comportamientos caóticos. Así, el teorema de Poincaré-Bendixson no se aplica a esos sistemas. Debido a que la evolución dinámica en los sistemas de orden fraccional contiene efectos de memoria de todos los eventos pasados, se ha utilizado para modelar fenómenos caóticos en física e ingeniería. Aquí, las derivadas de orden fraccional sirven como un grado de libertad adicional para mejorar las aplicaciones de ingeniería basadas en el caos. Por ejemplo, en criptografía y comunicaciones seguras, los sistemas caóticos de orden fraccional pueden generar un espacio de claves más grande que los de orden entero [24, 25]. Además, se han propuesto para algoritmos de cifrado de imágenes [26,27], algoritmos de cifrado de sonido [28, 29], algoritmos de autenticación para Internet de las Cosas (IoT) [30, 31]. De la misma manera, las aplicaciones de robótica basadas en el caos, como la planificación de rutas [32, 33], pueden beneficiarse del grado de libertad adicional para optimizar la cobertura de una determinada área.

4 1. Introducción

Las técnicas convencionales de sistemas clásicos se han generalizado a sistemas de orden fraccional para aplicaciones en control del caos y sincronización del caos [34]. Se ha encontrado que los sistemas caóticos de orden fraccional pueden generar varias familias de atractores ocultos y auto-excitados en sus modelos conmensurados e inconmensurados, y también se observan fenómenos de multi-estabilidad [35, 36]. Una derivada de orden fraccional es capaz de proporcionar un mejor control en la propagación de atractores caóticos que su contraparte de orden entero [37]. Aprovechando esta ventaja, los sistemas caóticos basados en funciones PWL (Lineales por Segmento por sus siglas en ingles Piece Wise Linear), son de gran interés debido a su capacidad para generar atractores caóticos de múltiples enrollamientos, los cuales pueden desplegarse en diferentes direcciones 1D, 2D y 3D y por lo tanto, pueden tener comportamientos dinámicos más complejos.

Sin embargo, la mayoría de estos trabajos permanecen en el campo teórico o solo se implementan en simuladores de circuitos, en lugar de realizaciones de hardware físico que son necesarias para validar las aplicaciones prácticas de los modelos matemáticos. Por lo tanto, uno de los principales desafíos en los sistemas caóticos de orden fraccional es su diseño de circuitos, que se puede realizar mediante dispositivos electrónicos analógicos o digitales, de modo que se puedan utilizar para varias aplicaciones, como cifrado, memristores, robótica, generadores de números aleatorios verdaderos, bioingeniería, sistemas de control, filtros, y muchos más.

#### 1.0.1. Antecedentes

Para aplicaciones prácticas, la derivada de orden fraccional puede implementarse utilizando circuitos analógicos o digitales [38]. Por un lado, las implementaciones analógicas se realizan empleando circuitos analógicos elaborados a partir de amplificadores operacionales, resistores, capacitores, bobinas y diodos, entre otros componentes [39]. Esta técnica resulta en una gran complejidad debido a los efectos no lineales intrínsecos en los componentes pasivos y activos [40]. Esta complejidad se hace evidente en varias publicaciones, como [41] y [42]. En cuanto a los sistemas caóticos, los circuitos analógicos están sujetos a perturbaciones externas como ruido y calor que pueden destruir el comportamiento caótico [43]. Otras limitaciones se presentan en [44], donde la implementación analógica de un sistema caótico se realiza con fines de comunicaciones seguras. A pesar de que esta implementación conserva las propiedades caóticas teóricas para aplicaciones de seguridad, la respuesta en frecuencia de esta implementación es difícil de mejorar y, por lo tanto, el rendimiento en la transmisión de datos se ve afectado.

Por otro lado, la complejidad de las implementaciones digitales radica en la formulación de algoritmos elegantes para resolver los modelos matemáticos que representan la derivada FO [45], que luego deben implementarse en plataformas digitales. A diferencia de las implementaciones analógicas, las digitales poseen características atractivas adicionales, como robustez, portabilidad, mayor flexibilidad para variar parámetros y condiciones iniciales del sistema [30,46,47]. Además, dado su enfoque intrínsecamente digital, ofrecen una mayor adaptabilidad para integrarse con aplicaciones emergentes, como el Internet de las Cosas (IoT). Por lo tanto, el interés de este trabajo se centra en la implementación digital.

Las preocupaciones actuales de las implementaciones digitales de SCOF incluyen el tipo de familia del sistema, la velocidad de operación, interfaces de comunicación y consumo de hardware y energía. Según la literatura, existen dos enfoques principales para la implementación digital de sistemas caóticos de orden fraccional [48]:

■ Implementaciones embebidas: Las implementaciones integradas están orientadas a la computación secuencial en procesadores de señal digital (DSP) o plataformas digitales basadas en Advanced RISC Machine (ARM), que son ejecuciones desarrolladas con lenguajes de programación de alto nivel como C o Python. Por ejemplo, las plataformas basadas en ARM presentan características atractivas como bajo consumo de energía, comunicación de hardware, costo relativamente bajo y amplio dominio sobre los dispositivos electrónicos de consumo, por lo que se utilizan en varias publicaciones [49–51]. Sin embargo, en aplicaciones en tiempo real, el análisis de rendimiento inevitablemente se degrada debido a los efectos de latencia durante la operación del hardware. Lo mismo se puede extender para las implementaciones basadas en DSP. Una técnica de mejora para esta tecnología puede obtenerse mediante el uso de procesamiento paralelo, aunque esta técnica introduce una complejidad considerable. Esto se debe a la necesidad de diseñar algoritmos que distribuyan las tareas equitativamente entre los procesadores y manejen la sincronización y comunicación entre ellos.

6 1. Introducción

■ Implementaciones no embebidas: Estas se enfocan en la computación paralela sobre hardware reconfigurable como tarjetas FPGAs. Estas implementaciones se diseñan utilizando un lenguaje de descripción de hardware como Verilog o VHDL para elaborar los circuitos digitales, los cuales pueden ser reutilizados en diferentes implementaciones. La tecnología FPGA es adecuada para implementar sistemas complejos con alto rendimiento computacional. Sin embargo, el diseño de sistemas caóticos de orden fraccional en FPGAs introduce una complejidad adicional, ya que cada tipo de sistema puede requerir una arquitectura de hardware específica. A pesar de esto, en en los ultimos años se han reportado varios trabajos sobre implementaciones de FPGAs de estos sistemas [52–56].

Para comprender mejor ambos enfoques, en la Tabla 1.1 se describen las principales características cada uno. En la Tabla 1.2, se presenta el número de publicaciones científicas relacionadas con las implementaciones embebidas y no embebidas de sistemas caóticos de orden fraccional para los principales chips digitales. Se puede observar que el número de trabajos ha mantenido un interés constante en los últimos años.

| Tabla 1.2: Número de publicacione | s por aî | o relacionadas | con | las implementaciones | embebidas y no |

|-----------------------------------|----------|----------------|-----|----------------------|----------------|

| embebidas de SCOF.                |          |                |     |                      |                |

| Año  | ARM | DSP | FPGA | Total |

|------|-----|-----|------|-------|

| 2015 | 0   | 2   | 0    | 2     |

| 2016 | 0   | 1   | 0    | 1     |

| 2017 | 1   | 1   | 10   | 12    |

| 2018 | 0   | 3   | 10   | 13    |

| 2019 | 1   | 3   | 11   | 15    |

| 2020 | 3   | 9   | 8    | 20    |

| 2021 | 1   | 12  | 1    | 14    |

#### 1.0.2. Motivación y Justificación

Uno de los principales desafíos para implementar SCOF en plataformas digitales consiste en seleccionar métodos de resolución adecuados, como los algoritmos numéricos de Adams-Bashforth-Moulton (ABM) y Grünwald-Letnikov (GL), el Método de Descomposición de Adomian (ADM), los métodos de Aproximación en el Dominio de la Frecuencia (FDA). Además, es crucial reducir la complejidad de estos métodos para que los recursos de hardware disponibles puedan manejar todos los estados anteriores

Tabla 1.1: Características de diseño embebido y no embebido.

|               | Enfoque embebido               | Enfoque no embebido              |

|---------------|--------------------------------|----------------------------------|

| Arquitectura  | Configuración predetermina-    | Una extensa colección de cel-    |

| de hardware   | da basada en arquitecturas     | das lógicas y bloques de me-     |

|               | ARM o Harvard. [57, 58].       | moria para una configuración     |

|               |                                | de una arquitectura flexible     |

|               |                                | [59].                            |

| Configuración | Opciones de lenguajes de pro-  | Configuración basada en Len-     |

|               | gramación como C o Python      | guajes de Descripción de         |

|               | [60, 61].                      | Hardware como Verilog o          |

|               |                                | VHDL [62,63].                    |

| Procesamiento | Paralelismo limitado debido a  | Alto paralelismo mediante la     |

| en paralelo   | la baja cantidad de núcleos de | configuración flexible de las    |

|               | procesador disponibles. [64].  | celdas lógicas, que pueden       |

|               |                                | ser programadas para ejecu-      |

|               |                                | tar múltiples operaciones si-    |

|               |                                | multáneamente [59].              |

| Interfaces de | Alta conectividad con otros    | Requiere la integración de       |

| comunicación  | dispositivos electrónicos gra- | protocolos de comunicación       |

|               | cias a las interfaces de co-   | específicos en el diseño, ya que |

|               | municación integradas, como    | no vienen predefinidos en el     |

|               | UART, SPI, y video [65].       | FPGA [66].                       |

| Resumen       | Diseño optimizado para pro-    | Flexibilidad para diseñar so-    |

|               | gramación versátil y sencilla, | luciones digitales con proce-    |

|               | pero con opciones limitadas    | samiento en paralelo para lo-    |

|               | para el procesamiento parale-  | grar altas velocidades de eje-   |

|               | lo.                            | cución, aunque su configura-     |

|               |                                | ción es compleja.                |

y calcular la solución actual, es decir, manejar los efectos de la memoria del sistema de orden fraccional.

Es importante destacar que las implementaciones digitales de sistemas de orden fraccional son relativamente un tema nuevo y en desarrollo. Podemos rastrear uno de los primeros trabajos en [67], donde se aborda la implementación digital de un controlador de orden fraccional. Varios años después, las publicaciones sobre sistemas caóticos con derivadas de orden fraccional se volvieron extensas y populares. A pesar de los numerosos trabajos publicados en los últimos años, las implementaciones digitales de sistemas caóticos de orden fraccional todavía enfrentan muchos problemas prácticos, como el costo, la complejidad y el rendimiento, que limitan las aplicaciones potenciales al interés académico.

8 1. Introducción

Motivado por el resumen anterior, este trabajo está orientado a la implementación digital de sistemas caóticos de orden fraccional. La complejidad tanto en la teoría matemática como en la configuración del hardware ha hecho que esta tesis tenga dos objetivos. La primera parte investiga los enfoques de las derivadas de orden fraccional y su potencial implementación en plataformas digitales. Con los resultados obtenidos, queremos generar una nueva metodología para el proceso de discretización de sistemas caóticos de orden fraccional. La segunda parte se ocupa de la configuración del hardware. Con las tecnologías emergentes de SoC, creemos que la comunicación de procesadores basados en RISC y plataformas FPGA ofrece más flexibilidad en aplicaciones en tiempo real. Por lo tanto, la segunda parte de este trabajo tiene como objetivo desarrollar una arquitectura de hardware optimizada para sistemas de orden fraccional en una plataforma FPGA.

#### 1.0.3. Planteamiento del Problema

En términos generales, la implementación digital de SCOF requiere formulaciones teóricas que proporcionen aproximaciones efectivas de derivadas fraccionales y la elección de una arquitectura de hardware eficiente que ofrezca tanto precisión computacional como costos razonables. Por lo tanto, los principales desafíos a resolver en el trabajo propuesto son los siguientes:

- Amplio rango de comportamiento caótico. Para validar los esfuerzos de un nuevo diseño de arquitectura embebida, los sistemas propuestos a implementar deben presentar un comportamiento dinámico dentro de un amplio rango de sus parámetros y de la derivada de orden fraccional.

- Baja complejidad en la configuración del sistema. Además de la flexibilidad para variar las propiedades dinámicas de un sistema dado, la arquitectura propuesta requiere una herramienta que permita configurar e implementar los sistemas caóticos de manera eficiente y utilizando un alto nivel de abstraccón.

- Rendimiento Computacional. Los resultados de la implementación digital deben presentar un alto rendimiento considerando un bajo uso de recursos de hardware para que estos puedan ser usados en aplicaciones practicas de ingeniería.

#### 1.0.4. Hipótesis

La formulación de algoritmos eficientes basados en la teoría matemática para resolver sistemas de orden fraccional (FO) permitiría realizar un diseño embebido específico basado en FPGA para la implementación de sistemas caóticos de orden fraccional. Dicho diseño podría proporcionar un buen equilibrio entre los recursos de hardware y el rendimiento, además de ser capaz de representar las ricas dinámicas de los sistemas caóticos de orden fraccional.

#### 1.0.5. Objetivo General

El objetivo de este trabajo es investigar estrategias para la implementación embebida de sistemas caóticos de orden fraccional (SCOF) y, con los resultados obtenidos, formular algoritmos eficientes para un diseño embebido basado en FPGA.

#### 1.0.6. Objetivos Particulares

Los objetivos particulares de este trabajo se enumeran a continuación:

- 1 . Estudio de Derivadas de Orden Fraccional. Realizar un análisis de las definiciones y propiedades de las derivadas de orden fraccional, así como los métodos existentes para resolver sistemas de orden fraccional.

- 2 . Caracterización de sistemas caóticos. Caracterizar la dinámica de sistemas caóticos de orden fraccional. Esto se refiere al estudio del comportamiento caótico a través de análisis de puntos de equilibrio, calculo de exponentes de Lyapunov y elaboración diagramas de bifurcación.

- 3 . Comparación de métodos para resolver sistemas de orden fraccional. Realizar una comparación de los métodos reportados en aplicaciones practicas de sistemas caóticos de orden fraccional. El objetivo es identificar ventajas, desventajas y áreas de oportunidad para proponer una metodología de diseño de sistemas caóticos de orden fraccional en sistemas embebidos.

- 4 . **Diseño de un sistema embebido**. Basado en la metodología propuesta en el punto anterior, proponer un diseño embebido para ser implementado en plataformas FPGA. Este diseño debe permitir la implementación de algoritmos

1. Introducción

de sistemas caóticos de orden fraccional, asegurando un procesamiento lo suficientemente rápido para la implementación en aplicaciones prácticas de estos sistemas.

5 . Implementación de sistemas caóticos de orden fraccional. Demostrar la metodología propuesta mediante la implementación de sistemas caóticos de orden fraccional.

#### 1.0.7. Metodología

Esta sección introduce las directrices que orientaron el trabajo de investigación, alineándose con los objetivos planteados, considerando que el objetivo principal es la implementación de sistemas caóticos de orden fraccional en un diseño embebido basado en FPGA, la metodología de investigación se dividio de la siguiente manera:

#### 1.- Análisis de las propiedades de derivadas de orden fraccional

- Definiciones Fundamentales: Esta parte se dedica al estudio de las definiciones formales de las derivadas de orden fraccional, como la derivada de Riemann-Liouville, la derivada de Caputo y la derivada de Grünwald-Letnikov. Cada una de estas definiciones proporciona diferentes perspectivas y herramientas matemáticas para modelar fenómenos con memoria y dependencias a largo plazo.

- Propiedades Matemáticas: Investigación de las propiedades clave de las derivadas fraccionales, incluyendo linealidad, conmutatividad con respecto a la integración, y comportamiento en el dominio de la frecuencia. Estas propiedades son esenciales para entender cómo las derivadas fraccionales pueden ser aplicadas a sistemas caóticos.

- Comparación de Métodos: Comparación de los métodos basados en estas derivadas para resolver sistemas fraccionales, evaluando su precisión, estabilidad y eficiencia computacional. Este análisis es fundamental para seleccionar el método más adecuado para diferentes tipos de aplicaciones.

#### 2.- Análisis de Sistemas Caóticos de Orden Fraccional:

Esta etapa se centra en la caracterización y análisis de sistemas caóticos de orden fraccional. Este análisis incluye:

- Caracterización de la Dinámica Caótica: Realizar un análisis de la estabilidad de los puntos de equilibrio y determinar el orden fraccional mínimo necesario para la existencia de caos.

- Implementación en Software: Uso de herramientas de simulación numérica para validar el comportamiento caótico mediante retratos de fase, cálculo de exponentes de Lyapunov.

- 3.- Análisis de métodos para aplicaciones prácticas de sistemas caóticos de orden fraccional: Este paso consiste en el análisis y comparación de diferentes métodos numéricos para resolver sistemas de orden fraccional en aplicaciones prácticas. El objetivo es determinar que método se adecua en distintas aplicaciones para IoT. Este análisis es esencial para seleccionar el método más eficaz según el contexto y las necesidades específicas de implementación. Basado en los análisis realizados en los puntos uno y dos de esta metodología, esta sección se enfoca en los siguientes métodos:

- Método de Grünwald-Letnikov (GL): Seleccionado por su precisión y capacidad para manejar discretizaciones directas de las derivadas fraccionales, lo que facilita su implementación en sistemas embebidos.

- Método de Descomposición de Adomian (ADM): Seleccionado por su eficiencia computacional y capacidad para descomponer problemas no lineales complejos en subproblemas más simples, mejorando así el rendimiento en implementaciones embebidas.

- 4.- Implementación y validación de un diseño embebido Basado en FPGA La etapa final se centra en la implementación de un procesador basado en RISC-V, optimizado para manejar sistemas caóticos de orden fraccional. Se propone utilizar un procesador basado en RISC-V debido a su capacidad para ofrecer un alto rendimiento computacional con un bajo consumo de energía, aprovechando la reconfigurabilidad del FPGA y la flexibilidad de la arquitectura RISC-V, para personalizar la solución en función de las necesidades específicas del sistema.

1. Introducción

## 1.1. Alcance de la Metodología y Resultados Preliminares

La metodología propuesta aborda los sistemas caóticos de orden fraccional, considerando tanto su análisis teórico como su implementación práctica en sistemas embebidos. Esta metodología ha sido validada mediante estudios comparativos y resultados experimentales los cuales se han reportado en diversas publicaciones, de las cuales destacan las siguientes:

- 1.- En la referencia [68], se realizó un análisis detallado de las ventajas y desventajas de las implementaciones embebidas y no embebidas de sistemas caóticos en FPGA. Este estudio demostró que las soluciones embebidas presentan un menor costo y menor consumo de energía, a pesar de un rendimiento ligeramente inferior en términos de velocidad. Estas implementaciones pueden beneficiarse del uso de hardware reconfigurable. Lo que oriento la decisión de utilizar un enfoque embebido optimizado para aplicaciones en tiempo real.

- 2.- En la referencia [69] se implementó un sistema PWL basado en el método de Grünwald-Letnikov, el cual fue aplicado en la encriptación de imágenes en tiempo real. Este estudio validó la viabilidad de los sistemas caóticos de orden fraccional en aplicaciones de comunicación en tiempo real y destacó la complejidad computacional del método de Grünwald-Letnikov.

En este trabajo se han seleccionado los sistemas caóticos PWL (Piecewise Linear o lineales por segmento) como caso de estudio, estos fueron elegidos debido a sus características únicas, como una estructura matemática simple y eficiente para generar comportamientos dinámicos complejos con múltiples atractores. Estos sistemas demostraron ser ideales para aplicaciones en criptografía tiempo real, según los resultados obtenidos en las publicaciones realizadas.

1.- En la referencia [70], se propuso un sistema basado en funciones signo, caracterizado por su simplicidad matemática y eficiencia computacional. Este sistema fue utilizado para aplicaciones de seguridad en datos médicos, particularmente en el cifrado ligero de señales biométricas en sistemas IoT de salud. Los resultados experimentales mostraron que este enfoque garantiza un nivel alto de

seguridad mientras mantiene un bajo consumo de recursos, haciendo viable su implementación en dispositivos con capacidades de hardware limitadas.

2.- De igual forma, en la referencia [69], se estudió la complejidad dinámica de los sistemas caóticos basados en funciones PWL, validada por la cantidad máxima de enrollamientos generados y el amplio régimen caótico con respecto a los parámetros y orden de la derivada fraccional, que estos sistemas pueden producir. Esta característica resulta en un espacio de llaves extremadamente grande, haciéndolo prácticamente invulnerable a ataques de fuerza bruta.

En ambos escenarios, se evaluó la resiliencia de los esquemas de seguridad basados en sistemas PWL de orden fraccional frente a diversos tipos de ataques, tales como, ataques de fuerza bruta, análisis estadísticos y la recuperación de datos en condiciones de ruido y pérdida parcial de información durante la transmisión de datos.

Las publicaciones mencionadas reflejan el amplio análisis realizado durante el desarrollo de la investigación, validando la relevancia y el potencial de los sistemas caóticos de orden fraccional, particularmente aquellos basados en funciones PWL, para aplicaciones prácticas en criptografía y seguridad de datos. Este documento se enfoca en los resultados clave relacionados con el alcance de los métodos para resolver sistemas caóticos de orden fraccional y el desarrollo de un sistema embebido basado en RISC-V

### 1.2. Organización del documento

### Organización del Documento

El presente trabajo está estructurado en seis capítulos y un apéndice, organizados de la siguiente manera:

#### Capítulo 1: Introducción

Este capítulo presenta el contexto general del trabajo, incluyendo la motivación, los objetivos generales y específicos, así como la relevancia del estudio. También se introducen los sistemas caóticos de orden fraccional y su importancia en aplicaciones prácticas.

1. Introducción

#### Capítulo 2: Análisis de Derivadas de Orden Fraccional

Se exponen los fundamentos teóricos de las derivadas de orden fraccional, abordando sus principales definiciones y propiedades. Además, se analiza la aplicabilidad de diferentes métodos numéricos para resolver sistemas fraccionales, considerando sus ventajas y limitaciones.

#### Capítulo 3: Formulación del Método de Descomposición PWL para Sistemas Caóticos de Orden Fraccional

En este capítulo se desarrolla y formula el método de descomposición PWL para la solución de sistemas caóticos de orden fraccional basados en funciones PWL, obteniendo soluciones que permiten analizar su naturaleza caótica.

#### Capítulo 4: Desarrollo Experimental

Este capítulo describe el diseño e implementación de un sistema embebido basado en RISC-V para la resolución y validación de sistemas caóticos de orden fraccional.

#### Capítulo 5: Análisis de Resultados

Se presentan y discuten los resultados obtenidos durante el desarrollo experimental, incluyendo métricas de rendimiento como throughput, uso de recursos de hardware y consumo de energía.

#### Capítulo 6: Conclusiones

En este capítulo se resumen los hallazgos principales de la investigación y se presentan las conclusiones generales del trabajo.

#### Apéndice

En el apéndice se incluyen las publicaciones realizadas durante el desarrollo de la investigación, las cuales respaldan y amplían los resultados presentados en este documento.

### Capítulo 2

## Análisis de Derivadas de Orden Fraccional

#### 2.1. Derivadas de Orden Fraccional

Según la clasificación propuesta por Teodoro, Machado y Oliveira [71], los operadores de orden fraccional se pueden clasificar en cuatro clases, de las cuales la clase  $F_1$  incluye los operadores fraccionales clásicos definidos por Riemann-Liouville, Caputo y Grünwald-Letnikov. Estos operadores fraccionales de la clase  $F_1$  preservan las propiedades de memoria y son no locales.

Consideramos únicamente las definiciones de operadores fraccionales de la clase  $F_1$ , ya que cumplen con el criterio de Ross [72] y con el Criterio de Sentido Amplio propuesto por Ortigueira y Machado [73], para evidenciar operadores fraccionales genuinos. En las siguientes subsecciones, introducimos los conceptos matemáticos básicos para la derivada de Caputo y su transformada de Laplace, la derivada de Grünwald-Letnikov, la integral de orden fraccional de Riemann-Liouville y sus propiedades, y la definición de sistemas de ecuaciones diferenciales fraccionales.

**Definición 1** La definición de Caputo para una derivada de orden fraccional se presenta de la siguiente manera [74, 75]:

$${}^{C}D_{t_{0}}^{q}f(t) := \begin{cases} \frac{1}{\Gamma(m-q)} \int_{t_{0}}^{t} \frac{f^{(m)}(\tau)}{(t-\tau)^{q+1-m}} d\tau & m-1 < q \le m, \\ \frac{d^{m}}{dt^{m}} f(t) & q = m, \end{cases}$$

(2.1.1)

$donde \; q \in \mathbb{R}^+ \; es \; el \; orden \; fraccional, \; m \in \mathbb{N} \; es \; el \; primer \; entero \; mayor \; que \; q, \; y \; \Gamma(\cdot)$

es la función gamma de Euler. Sea m = 1 y  $\alpha = -q$ , entonces

$$\Gamma(m-q) = \Gamma(\alpha+1) = \alpha\Gamma(\alpha), \quad \Gamma(\alpha) = \int_0^\infty t^{\alpha-1}e^{-t}dt. \tag{2.1.2}$$

**Proposición 1** Sea q > 0 y  $m = \lceil q \rceil$ . La transformada de Laplace de la derivada de Caputo de una función f(t) es  $\lceil 76 \rceil$ :

$$\mathcal{L}\lbrace {}^{C}D_{t_{0}}^{q}f(t)\rbrace = s^{q}F(s) - \sum_{k=0}^{m-1} s^{q-1-k}f^{(k)}(t_{0}), \qquad (2.1.3)$$

con  $m-1 < q \le m$ . Para condiciones iniciales nulas, la transformada de Laplace de la derivada de Caputo se reduce a  $\mathcal{L}^C D_{t_0}^q f(t) = s^q F(s)$ .

La definición de Grünwald-Letnikov para una derivada de orden fraccional se presenta de la siguiente manera [77,78]:

**Definición 2** Sea q > 0 y  $t \in \mathbb{R}$ . La derivada fraccional de Grünwald-Letnikov de orden q es:

$${}^{GL}D_t^q f(t) = \lim_{h \to 0} \frac{1}{h^q} \sum_{i=0}^{\infty} (-1)^j \binom{q}{j} f(t-jh), \tag{2.1.4}$$

donde los coeficientes binomiales  $\binom{q}{i}$  pueden calcularse de la siguiente manera:

$$\begin{pmatrix} q \\ 0 \end{pmatrix} = 1, \ \begin{pmatrix} q \\ j \end{pmatrix} = \frac{\Gamma(q+1)}{\Gamma(j+1)\Gamma(q-j+1)}, \ j = 1, 2, \dots$$

(2.1.5)

En la práctica, se utiliza la derivada fraccional truncada de Grünwald-Letnikov para simplificar el cálculo en funciones definidas solo a partir de  $t_0$  [79].

**Definición 3** Derivada fraccional truncada de Grünwald-Letnikov. Sea q > 0 y  $t_0 \in \mathbb{R}$ . La derivada fraccional truncada de Grünwald-Letnikov de orden q es:

$${}^{GL}D_{t_0}^q f(t) = \lim_{h \to 0} \frac{1}{h^q} \sum_{j=0}^N (-1)^j \binom{q}{j} f(t-jh), \tag{2.1.6}$$

with  $t > t_0$  and  $N = \lceil \frac{t - t_0}{h} \rceil$ .

La definición de Riemann-Liouville para un operador de integral fraccional  $J_{t_0}^q$  se establece como [80]:

**Definición 4** Operador de integral fraccional de Riemann-Liouville. Sea  $q \in \mathbb{R}^+$ . Entonces, el operador de integral fraccional  $J_{t_0}^q$  para una función f(t) definida en el espacio de Lebesgue  $L^1([t_0, T])$  se define como:

$$J_{t_0}^q f(t) := \frac{1}{\Gamma(q)} \int_{t_0}^t (t - \tau)^{q-1} f(\tau) d\tau, \ t \in [t_0, T], \tag{2.1.7}$$

donde  $\Gamma(\cdot)$  es la función gamma de Euler, y con  $J_{t_0}^0 f(t) = f(t)$ .

El operador  $J_{t_0}^q$  tiene las siguientes propiedades [74, 76, 80]:

• (a) Conmutativa y Aditiva

$$J_{t_0}^q J_{t_0}^p f(t) \iff J_{t_0}^p J_{t_0}^q f(t) = J_{t_0}^{p+q} f(t), \ q \ge 0, \ p \ge 0; \tag{2.1.8}$$

• (b) Dada una función de potencia  $f(t) = (t - t_0)^{\gamma}, \ \gamma > -1$

$$J_{t_0}^q (t - t_0)^{\gamma} = \frac{\Gamma(\gamma + 1)}{\Gamma(\gamma + 1 + q)} (t - t_0)^{\gamma + q};$$

(2.1.9)

• (c) Dada una constante  $C \in \mathbb{R}$

$$J_{t_0}^q C = \frac{C}{\Gamma(q+1)} (t - t_0)^q. \tag{2.1.10}$$

• La operación  $J_{t_0}^q$   $^CD_{t_0}^qf(t)$ , regresa:

$$J_{t_0}^{q C} D_{t_0}^q f(t) = J_{t_0}^q (J_{t_0}^{m-q C} D_{t_0}^m) f(t),$$

$$= J_{t_0}^{m C} D_{t_0}^m f(t)$$

$$= f(t) - \sum_{k=0}^{m-1} f^k (t_0^+) \frac{(t-t_0)^k}{k!}.$$

(2.1.11)

• La operación  $^{C}D_{t_{0}}^{q}$   $J_{t_{0}}^{q}f(t)$ , regresa: f(t).

**Definición 5** Sistema de Ecuaciones Diferenciales Fraccionales. Un Problema de Valor Inicial (IVP) para una ecuación diferencial fraccional en el sentido de Caputo se puede definir como:

$$\begin{cases}

{}^{C}D_{t_{0}}^{q}x(t) = f(t, x(t)) \\

x(t_{0}) = x_{0}, \ x'(t_{0}) = x_{0}^{(1)}, \dots, \ x^{(m-1)}(t_{0}) = x_{0}^{(m-1)},

\end{cases}$$

(2.1.12)

con  $x_0, ; x_0^{(1)}, \ldots, ; x_0^{(m-1)}$  como las condiciones iniciales en  $t_0$ . De esta manera, los sistemas fraccionales basados en Caputo tienen un significado físico más claro porque el problema de valor inicial depende únicamente de derivadas de orden entero. Además, el sistema (2.1.12) se puede expresar en forma matricial:

$$^{C}D_{t_{0}}^{q}x(t) = Ax(t) + Bu(t),$$

(2.1.13)

donde  $x(t) \in \mathbb{R}^n$ ,  $u(t) \in \mathbb{R}^m$ ,  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times m}$ ,  $Ct_0D^qtx(t) = [Ct_0D^qtx_1(t), \dots, Ct_0D^qtx_n(t)]^T$ ,  $(n, m) \in \mathbb{N}$ ,  $q \in (0, 1]$ . Cuando el sistema (13) es autónomo, se puede reescribir como  $C_tD_t^qx(t) = Ax(t)$ , con  $x(0) = x_0$ , 0 < q < 1,  $y \in \mathbb{R}^n$ .

**Definición 6** Estabilidad en sistemas de orden fraccional. Considere el sistema de orden fraccional

$$D_{t_0}^q x(t) = f(x(t)), (2.1.14)$$

donde (0 < q < 1) es la derivada de orden fraccional,  $x(t) = [x_1(t), x_2(t), ..., x_n(t)]^T \in \mathbb{R}^n$ ,  $y \ f(x(t)) = [f_1(x(t)), f_2(x(t)), ..., f_n(x(t))]^T$ . Sea eq. (2.1.14) un sistema de orden fraccional conmensurado  $q = q_1 = q_2, ..., q_n$ , con un punto de equilibrio hiperbólico en  $\bar{x} = [\bar{x}_1, \bar{x}_2, ..., \bar{x}_n]$ , se puede estimar que el comportamiento caótico puede emerger si el sistema satisface la siguiente condición [81]:

$$q > \frac{2}{\pi} \arg \left( \|\lambda_i (J(\bar{x}))\| \right). \tag{2.1.15}$$

Donde  $J(\bar{x}) \in \mathbb{R}^{n \times n}$  es la matriz jacobiana del sistema (2.1.14) evaluada en los puntos de equilibrio  $\bar{x}$  y los valores propios correspondientes satisfacen  $\ni \lambda_i$   $(i = 1, 2, \dots, n)$  con  $Re(\lambda_i) > 0$ ,  $Im(\lambda_i) \neq 0$ .

# 2.2. Métodos de solución para sistemas de orden fraccional

El paso crucial para implementar sistemas caóticos fraccionales utilizando hardware digital, tanto embebido como no embebido, es aplicar métodos de solución confiables, precisos y eficientes. Entre estos métodos se incluyen los métodos de aproximación (FDA), los métodos numéricos (ABM) y los métodos semianalíticos (ADM). No obstante, al resolver ecuaciones diferenciales de orden fraccional mediante alguno de estos métodos, pueden presentarse varios problemas [51, 82–86]. Las principales puntos a tomar en cuenta son:

- Cómo manejar adecuadamente la memoria persistente, ya que las propiedades de memoria prolongada de las derivadas fraccionales pueden hacer que el cálculo sea extremadamente lento y computacionalmente costoso.

- En otros casos, los métodos de solución presentan una baja precisión para emular el orden fraccional requerido.

- Además, para ciertos métodos de solución, sus coeficientes pueden necesitar ajustes antes de la implementación para coincidir con los formatos aritméticos disponibles en el hardware digital.

Por consiguiente, en las siguientes secciones, se analizan un conjunto de métodos de solución comúnmente utilizados en la literatura.

#### 2.2.1. Aproximación en el dominio de la frecuencia

La Aproximación en el Dominio de la Frecuencia (FDA, por sus siglas en inglés) es una técnica conocida y ampliamente utilizada para diseñar controladores de orden fraccional [87,88]. Además, ofrece una buena opción para resolver sistemas de orden fraccional [89,90]. El método funciona de la siguiente manera. Primero, la derivada fraccionaria se representa en el dominio de la frecuencia mediante la transformada de Laplace. Luego, se reemplaza, en un ancho de banda dado, por su aproximación de orden entero. La función de transferencia en el dominio s obtenida puede usarse para la implementación analógica de sistemas caóticos de orden fraccional. Para el alcance de nuestro trabajo, la implementación basada en circuitos digitales se obtiene mediante ciertas manipulaciones de procesamiento de señales, donde se puede derivar una función de transferencia en el dominio z [91], o incluso un sistema dinámico extendido de orden entero utilizando la fórmula de Faà di Bruno [49]. A continuación, se presentan las formulaciones teóricas del método FDA.

Consideremos la transformada de Laplace dada en (2.1.3) cuando se asumen condiciones iniciales nulas, entonces la solución para el sistema (2.1.12) se da por

$$x(s) = \frac{1}{s^q} \mathcal{L}f(x(t)), \qquad (2.2.1)$$