### Flexible Systolic Architecture for Image Processing at Video Rate

by

M. C. Griselda Saldaña González

A Dissertation submitted to the program in Computer Science, Computer Science Department in partial fulfillment of the requirements for the degree of

### DOCTOR IN COMPUTER SCIENCES

at the

National Institute of Astrophysics, Optics and Electronics 2007 Tonantzintla, Puebla

Advisor

Dr. Miguel Octavio Arias Estrada Principal Research Scientist Computer Science Department INAOE

© INAOE

All rights reserved The author hereby grants to the INAOE permission to reproduce and to distribute copies of this thesis document in whole or in part

## Flexible Systolic Architecture for Image Processing at Video Rate

by Griselda Saldaña Thesis Submitted to the Department of Computer Science, on 9<sup>th</sup> July 2007, in partial fulfillment of the requirements for the degree of DOCTOR IN COMPUTER SCIENCE

#### Abstract

Computer performance has improved tremendously since the development of the first all-purpose, all electronic digital computer in 1946. However, engineers, scientists and researchers keep making more efforts to further improve the computer systems performance to meet the demanding requirements for many applications such as Computer Vision and Image Processing which requires a high computational power to solve data-intensive applications in real-time.

There are basically three ways to improve the computer performance of algorithms in terms of computational speed. One way is *increasing the clock speed*; this parameter is determined by the worst-case delay in the datapath. The datapath elements can be rearranged such that the worst-case delay is reduced. Furthermore, it is possible to reduce the number of datapath actions taken in a single clock cycle. However, such attempts at reducing the clock cycle time have an impact on the number of Clocks per Instructions (CPIs) needed to execute the different instructions. Another way is to *reduce the CPI* by increasing the hardware concurrency. The final option consists in *reducing the number of instructions*; for this purpose it is possible to replace simple instructions. Once again any attempt to introduce new complex instructions has to be carefully balanced against the CPI, the clock cycle time, and the dynamic instruction frequencies.

Special-purpose parallel systems and, in particular the ones referred to as systolic arrays are very attractive approaches for handling many computationally-intensive applications. These systems consist of an array of identical Processing Elements (PE) executing the same operations on a set of data. These arrays capitalize on regular, modular, rhythmic, synchronous, concurrent processes that require intensive, repetitive computations.

The main obstacle to the widespread use of application-specific arrays of processors is development time, cost and their capacity to support a single algorithm at the same time. Recently, the use of reconfigurable hardware devices in the form of Field Programmable Gate Arrays (FPGAs) has been proposed as a means to implement parallel high performance solutions at an affordable price. These circuits provide a homogeneous surface of general-purpose logic elements which can be configured as often as desired to implement any combinational or sequential circuit.

Parallel processing architectures based on FPGAs provide an alternative to faster clock performance. This characteristic turns this approach into an attractive tool for high performance architecture implementation.

Low-level image processing operators play a fundamental role in modern image processing and computer vision algorithms. These operators exhibit natural parallelism that can be easily exploited using array of processors implemented with FPGAs.

Traditionally systolic array implementations are special purpose since they fit to one special algorithm; however in order to provide a higher degree of flexibility and generalization certain level of programmability support is essential. There have been previous efforts to develop general purpose systolic arrays; however these implementations require large local memories, and high-bandwidth for data communication between processors and global memory.

Within this context, this dissertation addresses the design and development of an FPGA-based image processing hardware architecture using a simple, resource-limited systolic array. The architecture is aimed to support operations involved in common low-level image processing algorithms which include 2D convolution, image filtering, matrix-matrix multiplication, morphological operations and pyramid processing. Furthermore, the architecture has been designed to pursue the implementation of higher complexity algorithms such as motion estimation, which has also been implemented in order to verify the generalization of the proposed schema. The architecture can achieve a processing rate that allows performance in real time, consuming a small amount of area. This feature allows replicating the architecture modules inside the same FPGA several times, consuming a small quantity of power.

The parallelism of this architecture has been explored for different key parameters. Different blocks in the architecture have been developed to generate a variety of operations, with different tradeoff in size and performance based on user-defined parameters. These parameters include the bit-width, array size, window size, image size and the application to be performed. This set of parameters determines the complexity of the operations in hardware, performance, power consumption, reliability and area occupancy which can guide for tradeoff during implementations for a particular application.

Memory optimization has been done at architectural-level in order to meet the best area-speed-power tradeoff. This was achieved by reducing the amount of memory accesses through memory splitting into buffers. In the context of memory bandwidth, an efficient balance between on-chip and off-chip memory has to be obtained to meet the best power-bandwidth tradeoff.

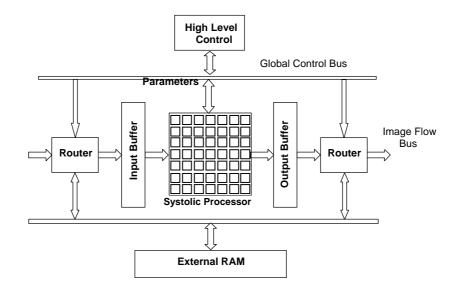

A complete image processing system usually requires a sequence of different tasks to be performed on an image. The intermediate result of one task is just the input of the next one. This process requires that data processed in the first stage are reused in subsequent stages. To facilitate the movement of the information among different phases of processing, in the proposed architecture Router elements are employed.

Using Routers it is possible to direct data between processing blocks that perform different algorithms inside the same architecture to chain results from these different processing stages. Furthermore Routers improve the system scalability constituting a means to increase the number of processing blocks inside the system

From high level, the architecture resembles a pipeline schema where a group of buffers stores data to be sent to the next processing block via Routers elements. This schema highly improves the architecture flexibility, since data movements among processing stages can be defined by the user.

The main contributions of the thesis are the following:

- Proposal of a new, high performance, flexible hardware architecture specialized in low-level processing under real time, which implies a processing rate of at least 30 frames per second, required in most of video standards.

- Generalization of the architecture as a hardware platform capable for test and implementation of higher complexity algorithms.

- Implementation of an enhanced systolic array that overcomes its inherent constraints such as extensibility (in the sense that it is impossible to produce an array to match all the possible sizes of different problems), speed limitation and high latency for large arrays.

- Implementation of a mechanism for easy scalability that allows enhancing the system by adding modules without redesigning the current basic structure.

- Implementation of a mechanism to chain processes in order to solve higher complexity algorithms.

- Analysis of area-speed-power tradeoff between the architecture main parameters.

- Analysis of constraints in area-performance behavior.

# Arquitectura Sistólica Flexible para el Procesamiento de Imágenes a Velocidad de Video

por Griselda Saldaña Tesis Sometida al Departamento de Ciencias Computacionales, el 9 de julio de 2007, como requisito parcial para la obtención del grado de DOCTOR EN CIENCIAS COMPUTACIONALES

#### Resumen

El desempeño computacional se ha mejorado tremendamente desde el desarrollo de la primera computadora totalmente electrónica de propósito general en 1946. Sin embargo, los ingenieros, científicos e investigadores siguen realizando esfuerzos que permitan obtener mejoras en el desempeño de los sistemas computacionales para satisfacer las exigencias de muchas aplicaciones tales como la Visión por Computadora, que requiere un alto poder computacional en la resolución de aplicaciones intensivas en datos bajo condiciones de tiempo real.

Básicamente hay tres formas de mejorar el desempeño de los algoritmos en términos de velocidad computacional. Una forma consiste en aumentar *la velocidad del reloj*, este parámetro se determina por el peor retardo en el datapath. Los elementos datapath se pueden reorganizar de manera tal que el retardo se reduzca. Además, es posible reducir el número de acciones que realiza el datapath en un solo ciclo de reloj. Sin embargo, tales tentativas por reducir el tiempo de ciclo de reloj tienen un impacto sobre el número de Ciclos por Instrucciones (CPIs) necesarias para ejecutar las diferentes instrucciones. Otra forma consiste en *reducir los CPIs* aumentando la concurrencia de hardware. La opción final consiste en *reducir el número de instrucciones*, para este propósito es posible reemplazar instrucciones simples por instrucciones más complejas de tal manera que el programa total ejecuta menos instrucciones. De nueva cuenta, cualquier tentativa por introducir nuevas

instrucciones complejas tiene que ser cuidadosamente balanceada contra los CPIs, el tiempo del ciclo de reloj y las frecuencias de instrucciones dinámicas.

Los sistemas paralelos de propósito específico y en particular los conocidos como arreglos sistólicos resultan ser enfoques muy atractivos para el manejo de muchas aplicaciones computacionalmente intensivas. Estos sistemas consisten de un arreglo de Elementos de Procesamiento (PE) idénticos que ejecutan la misma operación sobre un conjunto de datos. Estos arreglos toman ventaja de los procesos concurrentes, regulares, modulares, rítmicos, sincrónos, que requieren cálculos repetitivos e intensivos.

Los principales obstáculos para extender la utilización de los arreglos de procesadores de aplicación específica son el tiempo de desarrollo, el costo y la capacidad que tienen de dar soporte a un solo algoritmo a la vez. Recientemente, el empleo de dispositivos de hardware reconfigurables en forma Arreglos de Compuertas Programables en Campo (FPGA) se ha propuesto como un medio para implementar soluciones paralelas de alto rendimiento a un bajo costo. Estos circuitos proporcionan una superficie homogénea de elementos lógicos de propósito general que se pueden configurar tan a menudo como sea necesario para implementar cualquier circuito combinacional o secuencial.

Las arquitecturas de procesamiento en paralelo basadas en FPGAs proporcionan una alternativa para un desempeño más rápido del reloj. Esta característica convierte a este enfoque en un instrumento atractivo para la puesta en práctica de arquitectura de alto rendimiento.

Los operadores de procesamiento de imágenes de bajo nivel juegan un papel fundamental en los algoritmos de procesamiento de imágenes y de visión por computadora modernos. Estos operadores presentan un paralelismo natural que pude ser aprovechado fácilmente empleando arreglos de procesadores implementados con FPGAs.

Tradicionalmente, los arreglos de procesadores sistólicos son de propósito específico dado que sólo resuelven un algoritmo determinado, sin embargo, para proporcionarles un mayor grado de flexibilidad y generalidad es necesario proporcionar cierto nivel de programabilidad. Previamente se han realizado esfuerzos para desarrollar arreglos sistólicos de propósito general, sin embargo, estas implementaciones requieren memorias locales grandes y un gran ancho de banda para la comunicación de datos entre los procesadores y la memoria global.

Dentro de este contexto, este trabajo de investigación aborda el diseño y desarrollo de una arquitectura hardware versátil, basada en tecnología FPGA, para el procesamiento de imágenes, empleando un arreglo sistólico simple y recursos limitados. La arquitectura tiene como objetivo dar soporte a las operaciones involucradas en algoritmos de procesamiento de bajo nivel de imágenes comunes, entre los que se encuentran convolución 2D, filtrado, multiplicación de matrices, operaciones morfológicas y procesamiento piramidal. Además, la arquitectura se ha diseñado buscando la implementación de algoritmos de mayor complejidad tales como la estimación del esquema propuesto. La arquitectura puede alcanzar una razón de procesamiento que permite desempeño en tiempo real, consumiendo una pequeña cantidad de área. Esta característica permite replicar los módulos de la arquitectura varias veces dentro del mismo FPGA, consumiendo una cantidad de potencia reducida.

En esta arquitectura se ha explorado el paralelismo para los diferentes parámetros principales. Diferentes bloques en la arquitectura se han desarrollado para generar una variedad de operaciones, con diferentes compromisos en tamaño y desempeño con base en parámetros definidos por el usuario. Estos parámetros incluyen el número

de bits, el tamaño del arreglo, el tamaño de la ventana, el tamaño de la imagen y la aplicación a ser realizada. Este conjunto de parámetros determina la complejidad de las operaciones en el hardware, el desempeño, el consumo de potencia, la confiabilidad y la ocupación de área que proporcionan una guía para determinar los compromisos durante la implementación de una aplicación en particular.

Se ha realizado optimización de memoria a nivel arquitectural para encontrar el mejor compromiso entre área-velocidad-potencia. Esto se pudo alcanzar reduciendo la cantidad de accesos a memoria dividiéndola en buffers. En el contexto de ancho de banda de memoria, se debe obtener un balance eficiente entre la memoria interna y la memoria externa para encontrar el mejor compromiso entre potencia-ancho de banda.

Un sistema de procesamiento de imágenes completo por lo general requiere realizar una secuencia de tareas diferentes sobre una imagen. El resultado intermedio de una tarea es la entrada de la siguiente. Este proceso requiere que los datos procesados en la primera etapa sean reutilizados en etapas subsecuentes. Para facilitar el movimiento de la información entre diferentes fases de procesamiento, en la arquitectura presente se utilizan elementos Ruteadores.

Utilizando Ruteadores es posible dirigir los datos entre bloques de procesamiento que realizan algoritmos diferentes dentro de la misma arquitectura para encadenar resultados de etapas de procesamiento diferentes. Además los Ruteadores mejoran la escalabilidad del sistema ya que constituyen un medio para incrementar el número de bloques de procesamiento dentro del sistema.

Vista en alto nivel, la arquitectura asemeja un esquema de pipeline donde un grupo de buffers almacenan datos para ser enviados al siguiente bloque de procesamiento vía elementos de Ruteadores. Este esquema mejora la flexibilidad de la arquitectura ya que el movimiento de los datos entre etapas de procesamiento puede ser definido por el usuario. Entre las principales contribuciones de este trabajo se puede mencionar:

- Propuesta de una nueva arquitectura flexible de alto desempeño, especializada para el procesamiento de bajo nivel de imágenes en tiempo real, lo que implica una razón de procesamiento de al menos 30 cuadros por segundo, requerido en la mayoría de los estándares de video.

- Generalización de la arquitectura para conformar una plataforma hardware que permita la implementación y prueba de algoritmos de mayor complejidad.

- Implementación de un arreglo sistólico mejorado que supera las restricciones inherentes a este tipo de elementos, tales como la extensibilidad (en el sentido de que es imposible producir un arreglo para todos los tamaños posibles de los diferentes problemas), limitación de velocidad y una alta latencia en arreglos grandes.

- Implementación de un mecanismo para un fácil escalamiento del sistema que permite realizar mejoras agregando módulos sin tener que rediseñar la estructura básica actual.

- Implementación de un mecanismo de encadenamiento de procesos para resolver algoritmos de mayor complejidad.

- Análisis del compromiso entre área-velocidad-potencia entre los principales parámetros de la arquitectura

- Análisis de las restricciones en el comportamiento área-desempeño

### Acknowledgments

To the CONACYT for giving me the financial support to belong to an institution of excellence as the INAOE.

To the INAOE for providing the infrastructure and the human resources that allowed me to finish my PhD studies.

Furthermore, I want to take the opportunity to thank to my advisor Dr. Miguel Octavio Arias Estrada for his constant direction, supervision and support during the development of this thesis. His wide knowledge and his clear view have been of great value for the development of this research work. His ideas and concepts have had a remarkable influence on my entire career.

I want to thank also to the other members of my PhD committee who monitored my work and took effort in reading and providing me with valuable comments on this thesis: Dra. Claudia Feregrino Uribe, Dr. René Armando Cumplido Parra, Dr. Leopoldo Altamirano Robles, Dr. Carlos Alberto Reyes García, and Dr. Oswaldo Cadenas.

Furthermore I want to thank to all the members of the Computer Science Department of the INAOE who gave the opportunity to work with them in a good working atmosphere.

## **Dedicatorias**

A mis padres

Emilio Saldaña Márquez Blanca González Vázquez

Y a mis hermanos

Sara, Blanca y Emilio

Por apoyarme con su amor, paciencia y comprensión; por animarme a alcanzar todas mis metas profesionales. Ustedes son mi motivación y mi fuerza.

A mi cuñado Héctor de la Rosa por su apoyo y compañerismo.

A Gabriel Coronado por su paciencia y constancia durante los momentos más extenuantes.

# Contents

| Abstract                                                                                                                                                                                                                | ii       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Resumen                                                                                                                                                                                                                 | vii      |

| Acknowledgments                                                                                                                                                                                                         | xii      |

| Dedicatorias                                                                                                                                                                                                            | xiii     |

| Contents                                                                                                                                                                                                                | xiv      |

| List of Figures                                                                                                                                                                                                         | xvii     |

| List of Tables                                                                                                                                                                                                          | XX       |

| Chapter 1<br>Introduction                                                                                                                                                                                               | 1        |

| <ul><li>1.1 Motivation</li><li>1.2 Objectives and Contribution</li><li>1.3 Thesis Organization</li></ul>                                                                                                                | 6        |

| Chapter 2<br>Background and Previous Work                                                                                                                                                                               | 10       |

| <ul> <li>2.1 FPGAs.</li> <li>2.2 Reconfigurable Computing</li></ul>                                                                                                                                                     |          |

| Chapter 3<br>Systolic Arrays                                                                                                                                                                                            |          |

| <ul> <li>3.1 Parallel Architectures for Image Processing</li> <li>3.2 Parallel Computing Models and Systolic Arrays</li> <li>3.3 Systolic Systems, Arrays, and Algorithms</li> <li>3.4 Window-based Operators</li></ul> | 41<br>47 |

| 3.4.1 Convolution Characteristics       54         3.5 Systolic Arrays in FPGAs       57                                                                                                                                                                                                                   |                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Chapter 4<br>Architecture Overview                                                                                                                                                                                                                                                                         | 62                              |

| 4.1 Functional Requirements634.2 General Overview of the Architecture634.3 Functional Description of the Architecture724.4 Data Movements and Memory Schema744.5 Detailed Description of the Architecture734.5.1 Processing Element's Structure734.5.2 2D Systolic Array83                                 | 3<br>8<br>2<br>4<br>8<br>8      |

| Chapter 5<br>Hardware Implementation                                                                                                                                                                                                                                                                       | 86                              |

| 5.1 RC1000 Prototyping Board835.2 Fixed-Point Representation Analysis895.3 Implementation and Synthesis Results935.3.1 Processing Element Implementation945.3.2 Router Implementation105.3.3 2D systolic architecture105.4 Performance Analysis105.5 Scalability analysis1125.6 Architecture Discussion114 | 9<br>8<br>9<br>1<br>6<br>8<br>2 |

| Chapter 6<br>Architecture Applications                                                                                                                                                                                                                                                                     | 118                             |

| 6.1 Convolution1136.2 Filtering126.2.1 Median Filtering126.2.2 High Pass Filtering126.3 Matrix Multiplication126.4 Pyramid Decomposition126.5 Morphological Operators136.6 Template Matching136.7 Performance Discussion13                                                                                 | 1<br>1<br>3<br>4<br>6<br>0<br>3 |

| Chapter 7                                                                                                                                                                                                                                                                                                  | 120                             |

| Motion Estimation                                                                                                                                                                                                                                                                                          | 139                             |

| 7.3 Discussion                           | 146                                    |

|------------------------------------------|----------------------------------------|

| Chapter 8<br>Conclusion and Further Work | 147                                    |

|                                          | ······································ |

| 8.1 Conclusion                           | 147                                    |

| 8.2 Discussion                           | 148                                    |

| 8.3 Future Work                          | 149                                    |

| References                               |                                        |

| Appendix A. Glossary                     |                                        |

| Appendix A. Architecture Data Sheet      |                                        |

| Appendix B. Academic Report              |                                        |

# List of Figures

| Figure 2.1 Basic structure of Xilinx FPGAs.                                                                       | 13 |

|-------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2 Xilinx Virtex CLB                                                                                      | 15 |

| Figure 2.3 Computing paradigms                                                                                    | 19 |

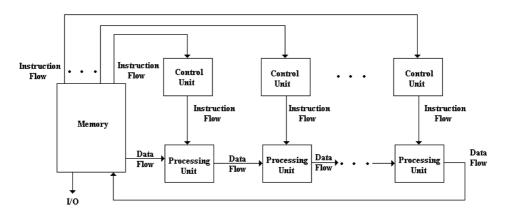

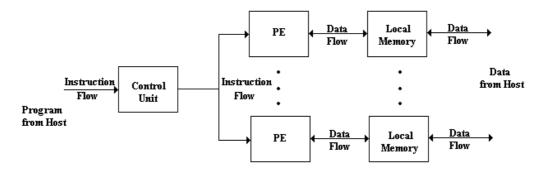

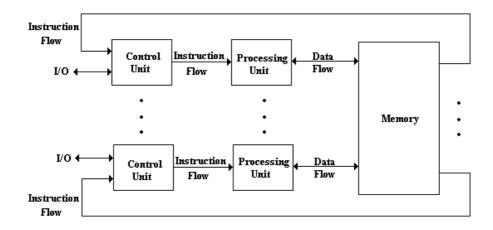

| Figure 3.1 SISD architecture in Flynn's Taxonomy                                                                  | 42 |

| Figure 3.2 MISD architecture in Flynn's Taxonomy                                                                  | 42 |

| Figure 3.3 SIMD architecture in Flynn's Taxonomy                                                                  | 43 |

| Figure 3.4 MIMD architecture in Flynn's Taxonomy                                                                  | 43 |

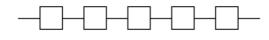

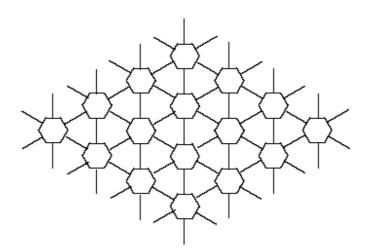

| Figure 3.5 Linear systolic array interconnection                                                                  | 48 |

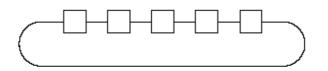

| Figure 3.6 1-dimentionalring interconnection                                                                      | 48 |

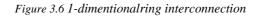

| Figure 3.7 2-dimensional square array                                                                             | 48 |

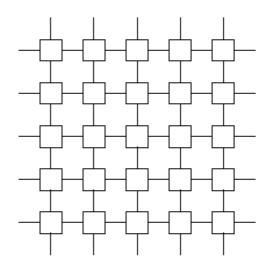

| Figure 3.8 2-dimensional hexagonal array                                                                          | 48 |

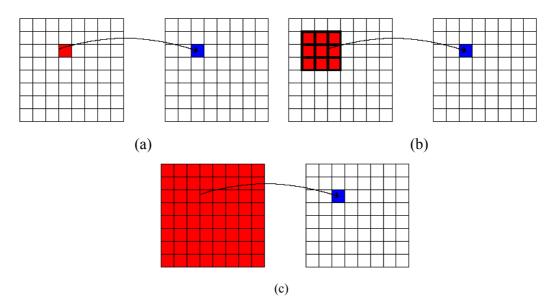

| Figure 3.9 Low-level image processing operators: (a) point operators, (b) window operators, (c) global operators. |    |

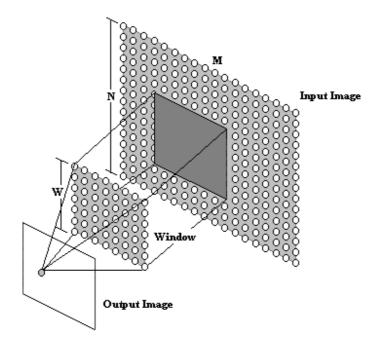

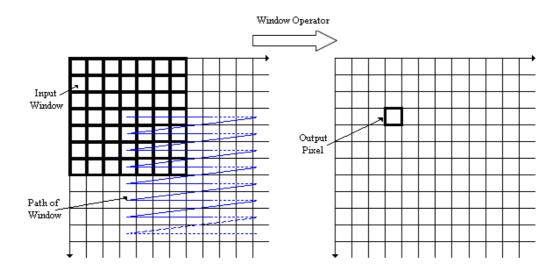

| Figure 3.10 Window operation                                                                                      | 53 |

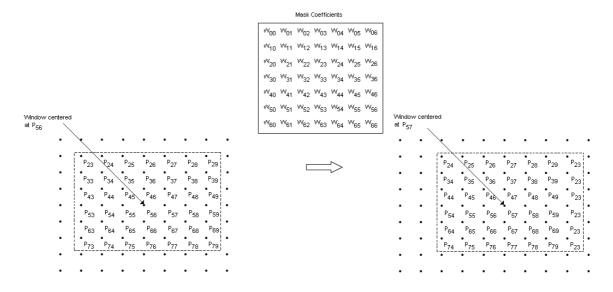

| Figure 3.11 Two consecutive output pixels for convolution                                                         | 54 |

| Figure 3.12 Image convolution process                                                                             | 55 |

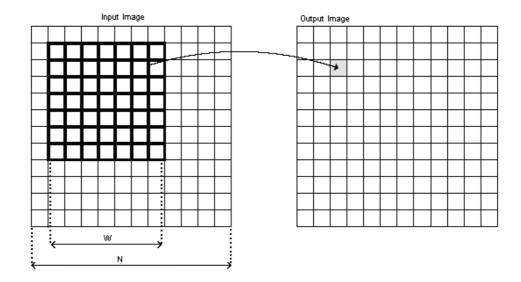

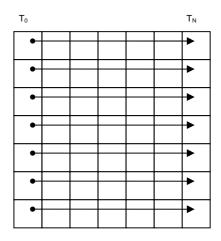

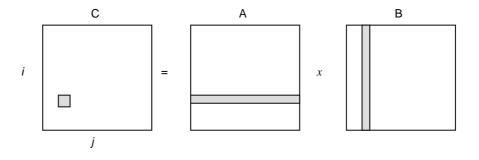

| Figure 4.1 Image scanning process for window operators                                                            | 65 |

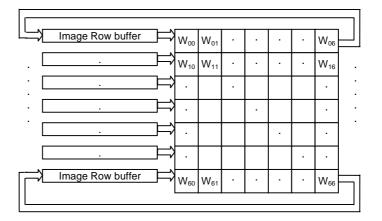

| Figure 4.2 Structure for image buffers.                                                                           | 66 |

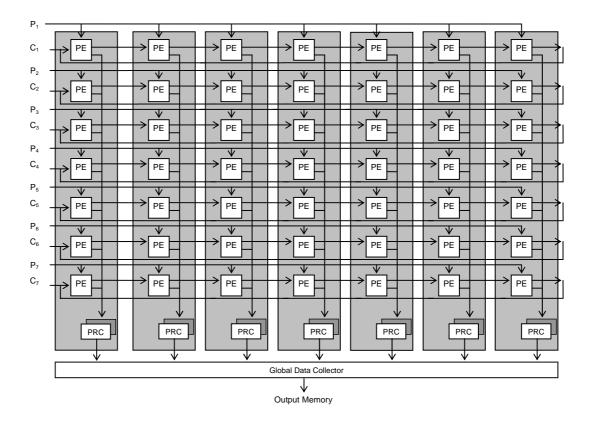

| Figure 4.3 Block diagram of the architecture.                                                                     | 69 |

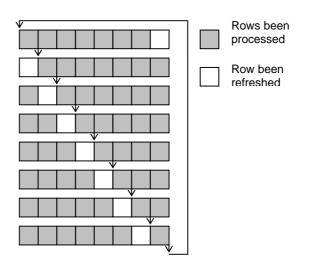

| Figure 4.4 Circular pipeline in the buffer memory                                                                 | 77 |

| Figure 4.5 Reading pattern for window mask                                                                        | 77 |

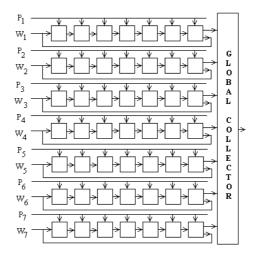

| Figure 4.6 2D systolic array implementation                                                                                                                   | 78          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 4.7 Convolution operation                                                                                                                              | 80          |

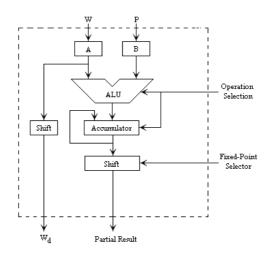

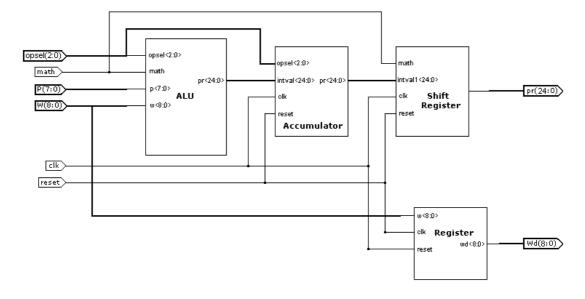

| Figure 4.8 Processing element implementation                                                                                                                  |             |

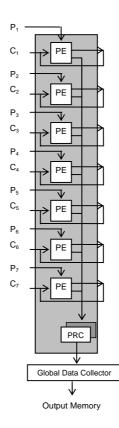

| Figure 4.9 Column of processing elements                                                                                                                      |             |

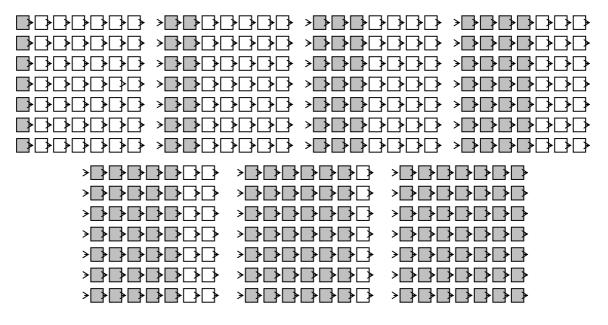

| Figure 4.10 Systolic array main modules                                                                                                                       |             |

| Figure 4.11 PE's activation schema                                                                                                                            |             |

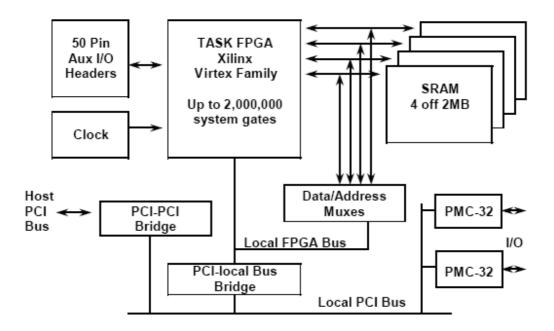

| Figure 5.1 RC1000 block diagram                                                                                                                               |             |

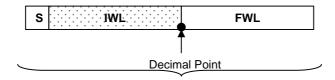

| Figure 5.2 Fixed-Point representation                                                                                                                         | 90          |

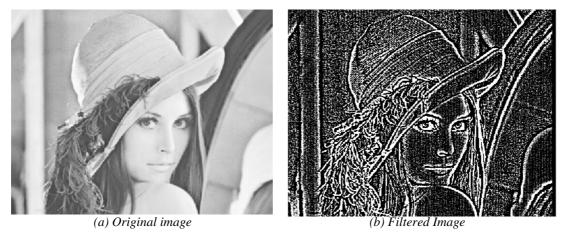

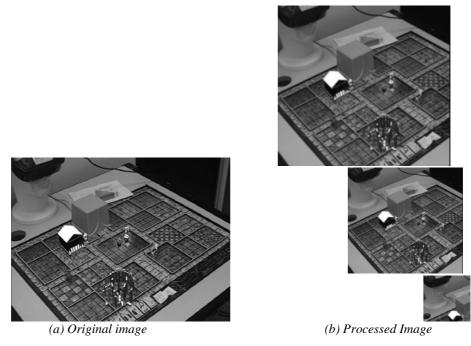

| Figure 5.3 Error image for a mean filter: (a) Original Image, (b) Output image processed by the architecture, (c) Output image from Matlab simulation, image. | , (d) Error |

| Figure 5.4 Error image for a mean filter using 8.8 representation                                                                                             | 96          |

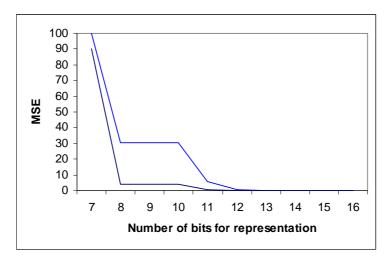

| Figure 5.5 Mean squared error vs. width of inputs                                                                                                             | 96          |

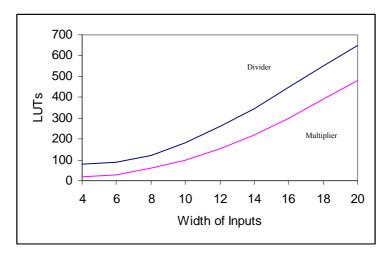

| Figure 5.6 Hardware cost for arithmetic operation                                                                                                             | 97          |

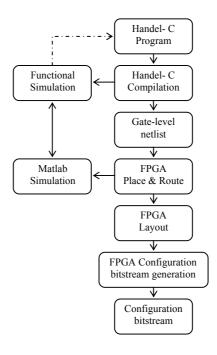

| Figure 5.7 Flow diagram to test the architecture                                                                                                              | 98          |

| Figure 5.8 Internal structure of the PE                                                                                                                       |             |

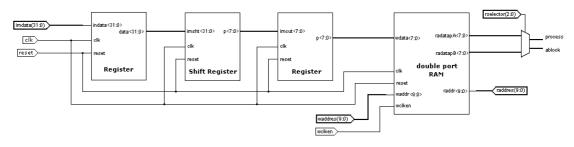

| Figure 5.9 Internal structure of the Router                                                                                                                   |             |

| Figure 5.10 Internal structure of the address generator                                                                                                       |             |

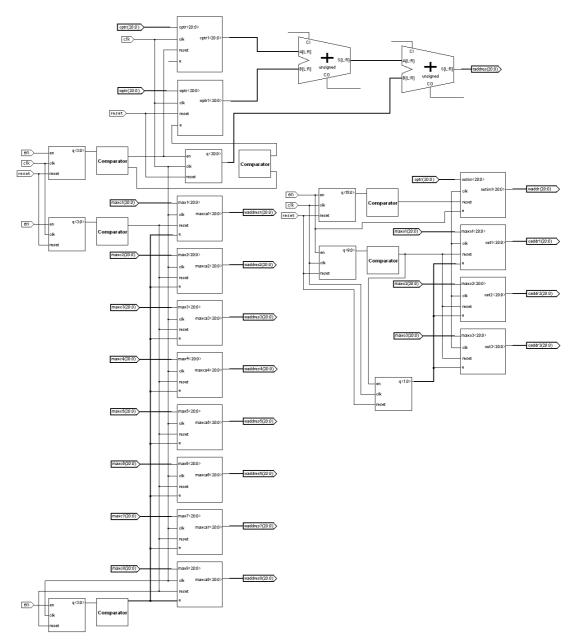

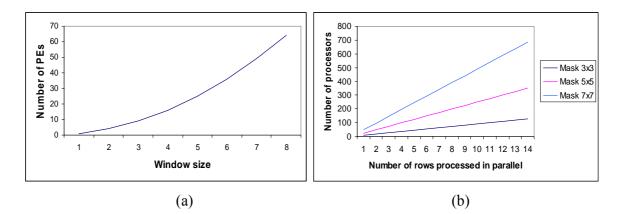

| Figure 5.11 Growth in the number of processor: (a) PEs required per window<br>PEs required per number of rows processed in parallel                           |             |

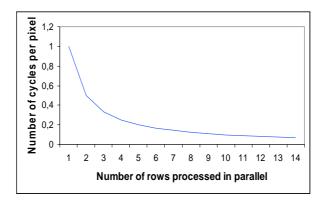

| Figure 5.12 Performance vs. Parallelism                                                                                                                       |             |

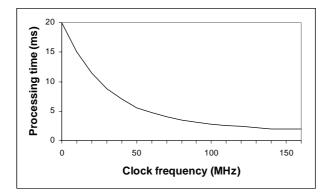

| Figure 5.13 Throughput                                                                                                                                        | 110         |

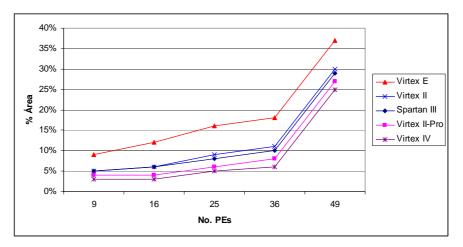

| Figure 5.14 Area occupancy for different FPGA families                                                                                                        | 112         |

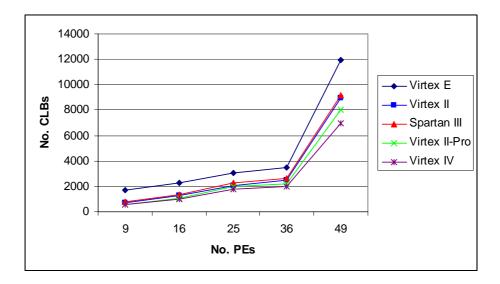

| Figure 5.15 Number of CLBs for different FPGA families                                                                                                        |             |

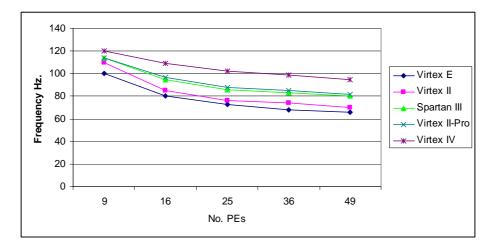

| Figure 5.16 Frequency for different FPGA families                  | 114 |

|--------------------------------------------------------------------|-----|

| Figure 6.1 Convolution concept                                     | 119 |

| Figure 6.2 Output for convolution using Laplacian operator         | 119 |

| Figure 6.3 Output for convolution using Gaussian operator          | 121 |

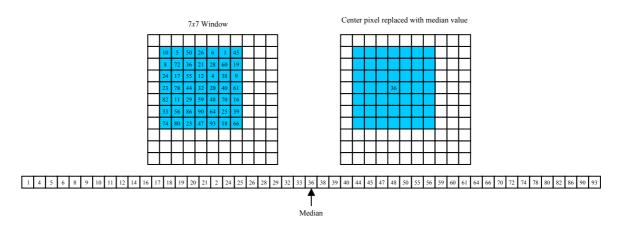

| Figure 6.4 Concept of median filter                                | 122 |

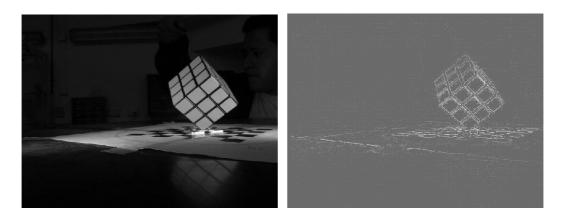

| Figure 6.5 Output for median filter                                | 123 |

| Figure 6.6 Output for high pass filter                             | 124 |

| Figure 6.7 Matrix by matrix multiplication                         | 125 |

| Figure 6.8 Matrix multiplication example                           | 125 |

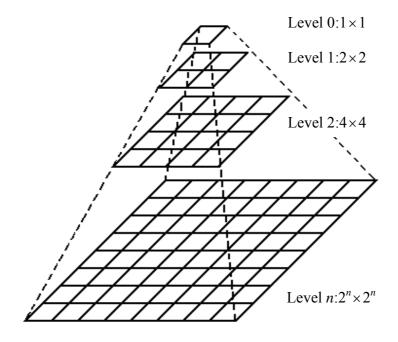

| Figure 6.9 Gaussian Pyramid concept                                | 127 |

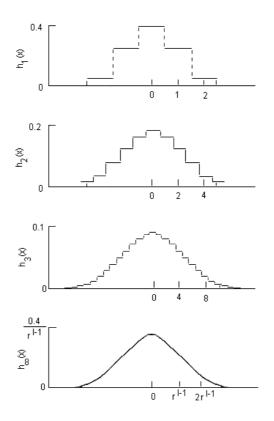

| Figure 6.10 Gaussian approximation                                 | 128 |

| Figure 6.11 Output image for 2 Level Gaussian Pyramid              | 129 |

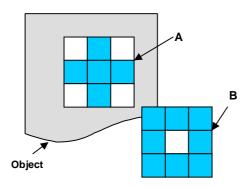

| Figure 6.12 Concept of structuring element                         | 130 |

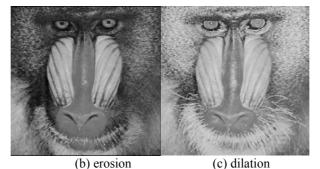

| Figure 6.13 Output for morphological operators                     | 132 |

| Figure 6.14 Output for template matching operator                  | 134 |

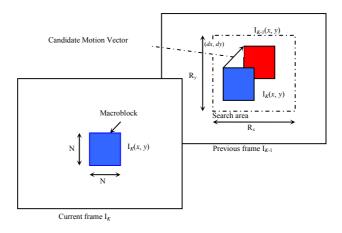

| Figure 7.1 Block-matching for motion estimation                    | 141 |

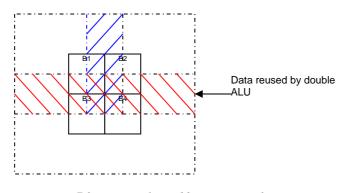

| Figure 7.2 Data overlapped between search areas                    | 144 |

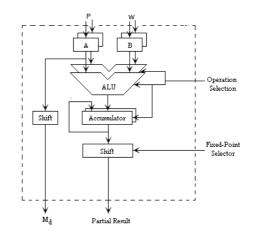

| Figure 7.3 Processing element for motion estimation implementation | 144 |

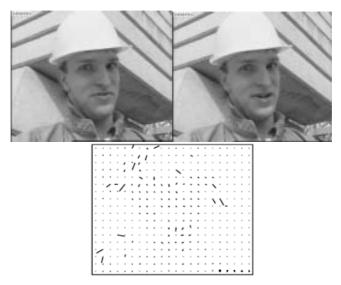

| Figure 7.4 Motion vectors for image sequence                       | 145 |

# **List of Tables**

| Table 2.1 Image Processing Architecture Taxonomy                  | 30  |

|-------------------------------------------------------------------|-----|

| Table 3.1 Computational load in convolution                       | 55  |

| Table 3.2 Scalar and local functions common in image applications | 56  |

| Table 5.1 Mean squared error                                      | 95  |

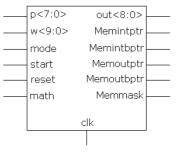

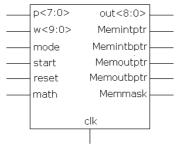

| Table 5.2 Signal description for PE module                        | 100 |

| Table 5.3 Technical data for the PE.                              | 101 |

| Table 5.4 Signal description for Router module                    | 102 |

| Table 5.5 Technical data for the Router                           | 102 |

| Table 5.6 Signal description for address generator module         | 104 |

| Table 5.7 Technical data for the Address generator                | 106 |

| Table 5.8 Technical data for the 2D systolic array                | 106 |

| Table 6.1 Technical data for the convolution                      | 120 |

| Table 6.2 Technical data for matrix multiplication                | 126 |

| Table 6.3 Vector of weighs for the Gaussian filter                | 128 |

| Table 6.4 Mask generated from vector of weights                   | 129 |

| Table 6.5 Technical data for erosion                              | 133 |

| Table 6.6 Technical data for dilation                             | 133 |

| Table 6.7 Technical data for template matching                    | 135 |

| Table 6.8 Summary of the architecture performance                 | 136 |

| Table 6.9 Amount of area for applications of the architecture     | 137 |

| Table 6.10 Performance for different architectures.               | 138 |

| Table 7.1 Technical data for the entire architecture.             | 145 |

# Chapter 1

# Introduction

### **1.1 Motivation**

Real-time image processing systems are finding many new applications in areas such as real time video rate processing, medical systems, multimedia and mobile systems. In building these systems, designers have essentially three options: developing the vision algorithms in software and running them on a *standard processor*, designing custom hardware specially tailored for the application like *Application Specific Integrated Circuits* (ASICs), or the use of *programmable hardware*.

The processing of images by computer is time costly due to the number of operations required and the volume of data to be processed [1]. The task is even more complex when the processing has to be carried out in real time. In order to meet the desired requirements of achieving the highest performance at lowest cost under real-time, special-purpose hardware architectures are often used. For performance improvement, reconfigurable computing systems have demonstrated to be a valuable alternative to traditional implementations. Reconfigurable solutions can often be orders of magnitude faster and/or less expensive than conventional alternatives like ASICs [2, 3]. Additionally reconfigurable systems have several advantages such as reduced development time; the capability to alter the hardware circuit after the system has been deployed in the field, and the possibility to implement modular and scalable applications.

General Purpose Processors (GPPs) are flexible enough to implement a variety of applications using the same device; however they can not always offer the computational power required for providing fast implementation of computationally intensive operations. In custom designed circuits functionality is hardwired once and cannot be changed again. ASIC implementations are usually efficient and can perform operations faster than other approaches; furthermore ASICs take advantage of existing parallelism in many image processing algorithms. But they are not implemented in practice because the required resources are not usually available at an affordable price and the design process takes a long time. These facts have usually limited researchers to the former option, which is to develop algorithms that can be executed as fast as possible on standard processors.

In the last few years, the third solution for real-time image processing system designers has become viable due to the rapid growth in capacity and speed of programmable hardware, which has demonstrated its efficiency to execute complex algorithms satisfying the simultaneous demand for application performance and flexibility [4, 5]. Programmable hardware has also been used successfully in some non signal processing applications [6]. FPGA technology allows designers to configure the chip according to the specifications of the algorithm cheap and quickly because it eliminates the most expensive and time consuming part of ASIC fabrication. It also reduces the debugging time because one can typically re-compile the design in a few hours and reconfigure the FPGAs in less than a second. FPGA technology presents four main benefits:

1. **Performance**. FPGAs enable custom computing systems to be highly specialized to specific data, as well as specific applications. One typical optimization is to implement highly parallel architectures that can exploit significant data-level parallelism. By capitalizing on these opportunities, a highly programmable system can be constructed that attains near ASIC performance.

- 2. **Cost Effectiveness**. Configurable computing can be used to reduce system costs through two approaches: hardware reuse and low Non-Recurring Engineering. A number of research efforts have demonstrated time-shared methods for simulating a large circuit on a smaller FPGA. Furthermore, as the feature size of semiconductor processes shrink FPGAs technology become much more cost effective.

- 3. **Custom I/O**. FPGAs provide an extremely rich and flexible set of programmable I/O signals. These components give the system designer an opportunity to reuse existing hardware, or commit earlier to a new hardware design. The benefits of custom I/O extend beyond the prototype stage; for example system functionality may change after deployment, and the ability to rewire system I/O through reprogramming the FPGA can be an invaluable advantage.

- 4. **Fault-Tolerance**. Some recent efforts have investigated the benefits of using FPGAs to provide fine-grained fault recovery. This approach has the benefit of increasing system reliability for much lower cost than the traditional approach of circuit and subsystem redundancy.

Low-level image processing operators play a fundamental role in modern image processing and computer vision algorithms. These operators exhibit natural parallelism that can be easily exploited using array of processors implemented with reconfigurable hardware.

FPGA implementations of this kind of applications have the potential to be parallelized using a mixture of spatial and temporal parallelism. Pragmatically, the degree of parallelization is subject to the processing mode and hardware constraints imposed by the system. Based on previous work [7-9] three main constraints have been identified for implementation: timing (limited processing time), bandwidth (limited access to data), and resource (limited system resources).

- **Timing constraints**. The data rate requirements of the application impose a timing constraint which in turn drives the other constraints, when real-time is demanded this restriction become crucial. If there is no requirement on processing time then the constraint on bandwidth is eliminated because random access to memory is possible and desired values in memory can be obtained over a number of clock cycles with buffering between cycles.

- Bandwidth constraints. Some operations require that the image be partly or wholly buffered because the order that the pixels are required for processing does not directly correspond to the order in which they are input. Frame buffering requires large amounts of memory. Typically FPGAs use off-chip memory for frame buffering but this may only allow a single access to the frame buffer per clock cycle, which can be a problem for the many operations that require simultaneous access to more than one pixel from the input image.

- Resource constraints. This issue arises due to the finite number of available resources in the system such as local and off-chip RAM, or other function blocks implemented on the FPGA. Programming without consideration of the hardware that will be generated has a direct effect on the speed of the implementation.

These constraints are inextricably linked and manifest themselves in different ways depending on the processing mode.

Traditionally these issues have been faced developing application specific architectures optimized to be used in the systems for which they were designed. In order to improve performance some well known pipeline structures have been used. They help to reduce memory overhead when predictable scanning schemas are used; however, it turns out that they cannot cope with unpredictable image scanning which has proved to be very efficient in the implementation of certain operators. Furthermore pipelining results in an increase in logic block usage, caused by the need to construct pipeline stages and registers. While the impact of pipeline registers on

logic block usage will be minimal, care must still be taken to make efficient use of the available logic blocks.

This thesis aims to make progress on the question of whether reconfigurable computing will supply a viable option to fulfill the requirements of real-time image processing systems of high performance, high flexibility and low power consumption. For this purpose it is essential to explore new design and implementation strategies at the architectural level. Also it is relevant to deal with issues arising from the integration of reconfigurable hardware with a processor including:

- To make an efficient use of area avoiding a poor utilization of the silicon resources available.

- To reduce latencies due to increased communication.

- To avoid a reduced bandwidth looking for scalability.

- Smart use of memory.

- To implement a cost-effective reconfigurable processor for intensive computer vision applications applying reconfigurable techniques.

- To achieve a good tradeoff in computer vision system design under the Reconfigurable Computing approach.

Many complex image processing algorithms use low-level results of window operators as primitives to pursue higher level goals [10, 11]; thus another problem to be addressed consists of finding a way to extend the architecture capability and flexibility to support these higher level applications. In this case, several issues must be taken into account:

- To use a reduced amount of on-chip memory for buffering data.

- Low cost of reconfiguration.

- Smart parameters transfer.

- High potential for scalability.

### **1.2 Objectives and Contribution**

The main objective of this thesis is to demonstrate that making use of parallelism of data present in low-level image operators, and reconfiguration techniques it is possible to implement a versatile reconfigurable systolic architecture for low-level image processing achieving high performance and low power consumption in real time.

The research aims to build a system for such commitments providing the processing of 30 frames per second on a  $640 \times 480$  sized grey level images:

- To implement a high performance flexible architecture specialized in lowlevel processing under real time.

- To propose a parallel architecture based on reconfigurable modules to execute a sequence of algorithms according to a predefined pattern.

- To implement a customizable systolic array allowing the use of different window size in image operations.

- To analyze area-speed-power tradeoff between the architecture's main parameters.

- To optimize architecture performance according to metrics like:

- Processing Time

- ➢ Area Used

- To propose guidelines to apply Hardware/Software co-design in the proposed architecture.

- To define a testbench to quantify the improvement obtained with the proposed reconfigurable architecture compared to previous approaches.

The research approach and the key contributions of the thesis are as follows:

- Design and development of a new flexible high performance FPGA-based hardware architecture for window-based image processing, that can be generalized to support other algorithms of higher complexity.

- Implementation of a systolic array with extended capacities to reduce its inherent constraints such as extensibility (in the sense that it is impossible to produce an array to match all the possible sizes of different problems).

- Determining metrics to reduce the reconfiguration cost associated to reconfiguration techniques.

- Implementation of a mechanism to chain processes in order to solve algorithms of higher complexity.

- Analysis of mechanisms to build a hardware library of reusable image processing modules.

- Analysis of potential application for the architecture and its implications for implementation.

### **1.3 Thesis Organization**

The thesis is organized as follows. Chapter 2 gives a background to the work undertaken in the thesis. It explains the concept of reconfigurability upon which this research is based, along with a review of other works that led to this research. Some mechanisms of reconfiguration are described in detail to identify its major characteristics. Previously proposed hardware implementations of image processing tasks are briefly analyzed and discussed in order to identify some problems, limitations and drawbacks. This chapter details the different FPGA approaches for image processing hardware implementations and concludes presenting some unsolved problems to be addressed using reconfigurable computing. Chapter 3 reviews different characteristics of parallel architectures for image processing discussing in detail the concepts of systolic processing, pipeline and Single Instruction Multiple Data (SIMD) in the context of image processing as well as their application to a special kind of operators denominated as window-based operators and concludes with some considerations for an FPGA implementation of such systems.

Chapter 4 introduces the systolic architecture for window-based image processing providing its functional requirements as well as a top-down description of its main modules and their operation. The data movement and the memory schema used are presented to highlight the mechanism to reduce number of access to memory.

Chapter 5 provides the FPGA implementation details of the architecture and a description of the hardware used to test and to implement the system. Furthermore an analysis of the considerations for the implementation of fixed-point operations is performed in order to achieve a small amount of error. Simulation and synthesis results, timing and performance of the proposed architecture are presented using standard metrics for evaluation; a special section of this chapter is devoted to the performance analysis and discussion of the architecture and the comparison with other technologies. A brief discussion is carried out at the end of the chapter highlighting the main features of the architecture; modularity, communication, memory and data flow.

Chapter 6 presents some processing applications mapped to the architecture: convolution, filtering, matrix multiplication, pyramid decomposition, morphological operators, and template matching to validate the correct functionality of the proposed architecture. One section of this chapter is devoted to determine the silicon area occupied by the architecture in order to use this parameter as a standard metric for evaluation. The synthesis results obtained for each operator are presented to make a

comparison with previous systems implemented, highlighting the main improvements achieved with the present implementation.

Chapter 7 describes some concepts of motion estimation algorithms from a video coding perspective, focusing on block based techniques; furthermore a short review of previous work in literature is presented. In this chapter some characteristics of motion estimation algorithm that allow the representation as a window operator are clarified to determine the modifications required to the implementation of this algorithm. The synthesis results for this version of the architecture are presented as well as a discussion of the performance achieved.

Finally chapter 8 presents the thesis conclusions emphasizing the advantages provided by the implementation of the present architecture in comparison with previous works, the accomplishments and contributions are detailed. In addition some potential applications and extensions for the architecture are discussed in order to outline the future work. In this section the possibility of using dynamic reconfiguration is remarked due to this is a strong research direction to follow.

# **Background and Previous Work**

There are two traditional approaches to implement digital logic systems: mapping an algorithm to a General Purpose Processor and designing custom hardware that implements an algorithm. GPPs can implement a wide variety of tasks, but do not fully utilize the potential power of the silicon with which they are implemented. The other approach is to design custom silicon for a particular task. The custom silicon is commonly known as an ASIC.

ASICs are designed specifically to perform a given computation, and thus they are very fast and efficient when executing the exact computation for which they were designed. However, the circuit cannot be altered after fabrication. This forces a redesign and refabrication of the chip if any part of its circuitry requires modification. This is an expensive process, especially when one considers the difficulties in replacing ASICs in a large number of deployed systems.

ASICs can be used to carry out fixed applications that have to be executed with the minimum amount of area, delay and energy costs. As the size of the application grows, it becomes practically impossible to implement it in silicon. This is where the GPP steps in. Processors execute a set of instructions to perform a computation. By changing the software instructions, the functionality of the system is altered without changing the hardware. However, the downside of this flexibility is that the performance may diminish, if not in clock speed then in work rate, and is far below than an ASIC. The processor must read each instruction from memory, decode its meaning, and only then execute it. This results in a high execution overhead for each

individual operation. Additionally, the set of instructions that may be used by a program is determined at the fabrication time of the processor. Any other operations that are to be implemented must be performed out of existing instructions.

The reconfigurable computing domain has emerged as a new computing paradigm to fill the gap between ASICs and GPPs [12], achieving potentially much higher performance than software, while maintaining a higher level of flexibility than hardware. The goal of reconfigurable systems is to achieve implementation efficiency approaching that of specialized logic while providing the silicon reusability of general purpose processors [13].

FPGAs are the building blocks for reconfigurable computing. The ability to exploit the parallelism often found in the algorithms, as well as the ability to support different modes of operation on a single hardware substrate, gives to these devices a particular advantage over fixed architecture devices such as serial Central Processing Units (CPUs) and Digital Signal Processors (DSPs). Furthermore, development times are substantially shorter than dedicated hardware in the form of ASICs, and small changes to a design can be prototyped in a matter of hours. Adding a reconfigurable portion to a system, enables it to support a broader range of applications and lets developers adapt the hardware to changing needs and evolving standards. Thus a reconfigurable platform offers the advantages of both embedded software and custom hardware.

For optimum implementation of algorithms used in high-performance computing applications, reconfigurable hardware is a potential option to be applied. FPGAs are a more effective solution because the architecture can be defined at runtime. Both connectivity and processing capabilities can be tailored to suit the needs of the algorithm being implemented.

In particular, the largest part of the die area of an FPGA is consumed by the configurable routing and this is important because in general, the biggest limiting factor of any implementation of a parallel algorithm is data passing [14]. For this reason FPGAs will always offer significant opportunities of improvement over any GPP with fixed communication buses. The majority of the silicon used by a GPP is not actually operating on each clock cycle because there is generally only one instruction being executed at a time and each of those instructions rarely use a significant fraction of the capability of the processor. FPGAs offer a big advantage here not only because all of the hardware can be executing on each clock cycle, but also because the mix of computational elements can be tuned to the precise requirement of the application.

For these reasons, among others, reconfigurable computing offers significant advantages over fixed computing and these advantages are overwhelming in the area of high performance computing such as Video Processing [14].

### 2.1 FPGAs

The most common reconfigurable devices today are Field Programmable Gate Arrays. An FPGA is a programmable logic device that supports implementation of logic circuits, its real advantage is that the chip can be erased and re-programmed any number of times making the process of debugging both quick and cheap, requiring just one initial purchase cost.

Traditionally, FPGAs were used primarily for prototyping. A designer could quickly prototype his designs in hardware to check that the design meets the specification and provides a correct solution. Through this use, it is unnecessary, until the final stages of prototyping, to ever fabricate the hardware design being developed. This

drastically reduces both the cost and the time of hardware development [15]. In recent years, both the performance and capacities of FPGAs have grown such that they can now be used to implement many end products. While the process of moving the FPGA into commercial products has been used in embedded systems for a while, it is only now beginning to be used in non-embedded computing [16].

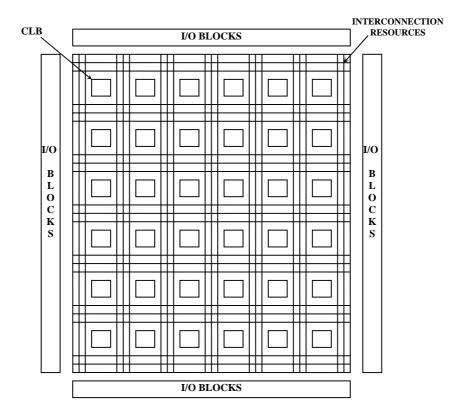

Typical architecture of a Xilinx FPGA comprises a regular array of Configurable Logic Blocks (CLBs) with routing resources for interconnection and it is surrounded by programmable Input/Output Blocks (IOBs). CLBs provide the functional elements for constructing logic while IOBs provide the interface between the pins of the package and the CLBs. FPGAs are widely used as a prototype before fabricating a VLSI design, or can be used directly in a product. Figure 2.1 shows the basic structure of Xilinx FPGAs [17].

Figure 2.1 Basic structure of Xilinx FPGAs.

The structure of a CLB can be as simple as a transistor or as complex as a microprocessor [18]. The CLBs can be arranged in a row or, more commonly, in a matrix form. The number of CLBs available also varies from vendor to vendor. The interconnection network serves as the underlying fabric to provide flexible interconnection between CLBs for logic synthesis. Of the three building blocks in an FPGA, the interconnection network typically occupies maximum space [19].

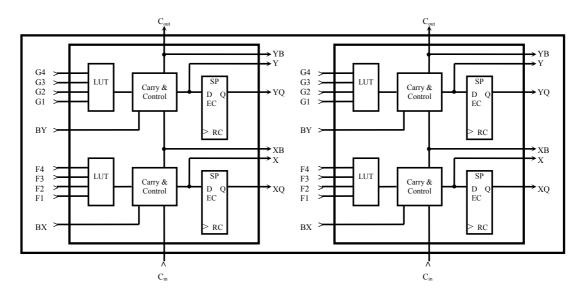

A CLB is constructed from the following components:

- Look up tables (LUT): A CLB contains a certain number of LUTs that are the basic computing elements inside FPGAs. An n-input LUT is an *n*-address memory used to store the 2<sup>n</sup> possible values of an n-inputs boolean function. With an n-input LUT it is possible to implement any function with *n* variables. The values of the function for any combination of the *n* variables is computed and stored in the LUT. The actual variables are used to address the LUT at the location where the correct value is stored. The result appears at the LUT output.

- 2. **Flip Flops (FF):** Flip Flops are used to temporally store values. The value to be stored in the FF can be the LUT-output or a signal with an external source.

- 3. **Multiplexers (MUX) :** Multiplexers are used in CLBs to connect the LUToutput or another CLB-input signal to the FF-input or to a CLB-output

Figure 2.2 shows a Xilinx Virtex II CLB [20]

Figure 2.2 Xilinx Virtex CLB

FPGA chips can be classified into three categories according to the structure of their configurable parts [21]. These categories are Static Random Access Memory (SRAM) based FPGAs, Electrically Erasable and Programmable Read Only Memory (EEPROM) based FPGAs, and antifuse-based FPGAs. Because the configuration of an antifuse is permanent, antifuse-based FPGAs are one time programmable devices. The configuration of an EEPROM-based FPGA can be changed electrically using high-voltage electrical signals. SRAM-based FPGA chips can be reconfigured by loading the bits in the configuration file into the SRAM memory cells. These chips can be reconfigured at run time by loading a new configuration to the SRAM cells. Since they use the same technology as computer memories, they have to be configured each time the system is powered on. Because the ease of configuration, SRAM-based FPGA chips are the most widely used FPGA chips. Also, theoretically these chips can be reprogrammed an infinite number of times.

The design process for FPGAs is aided through the use of a variety of CAD tools. These tools allow the designer to describe the design using various specification formalisms such as VHDL [22], Verilog [23], Handel-C [24], state machines, or other

proprietary languages. Using this specification, the tools perform synthesis of the design to generate a gate-level description of the system. This is followed by place and route tools which fragment the design into the FPGAs basic logic components and determines optimal interconnecting schemas.

### 2.2 Reconfigurable Computing

A Reconfigurable Computing (RC) system can be defined as a computer system that contains one or more general purpose processors and one or more configurable hardware components that are designed for their hardware functionality to be configured by the user for different applications [25]. Usually the general purpose processor acts as the host processor and the reconfigurable hardware components are used as a coprocessor. The users of the RC system typically partition their applications and execute the computationally complex sections on the reconfigurable hardware to potentially increase performance.

Reconfigurable computing exploits configurable computing devices, such as FPGAs, so they can be customized to solve a specific application [7]. Due to its potential to accelerate a wide variety of applications, reconfigurable computing has become the subject of a great deal of research. Its key feature is the ability to perform computations in hardware to improve performance, while maintaining the flexibility of a software solution. This flexibility is significant as it reduces the costs in comparison to an ASIC when changes to the system are required.

Many types of programmable logic are available. The current range of offerings includes everything from small devices capable of implementing only a handful of logic equations to huge FPGAs that can hold an entire processor core. In addition to this difference in size there is also much variation in architecture.

At the low end of the spectrum are the original Programmable Logic Devices (PLDs). These were the first chips that could be used to implement a flexible digital logic design in hardware. Other names that might be found for this class of devices are Programmable Logic Array (PLA), Programmable Array Logic (PAL), and Generic Array Logic (GAL). As chip densities increased, the PLD manufacturers evolved their products into larger parts called Complex Programmable Logic Devices (CPLDs). For most practical purposes, CPLDs can be thought of as multiple PLDs in a single chip. The larger size of a CPLD allows the implementation of more complicated designs.

At the high-end, in terms of numbers of gates, FPGAs can be found. These devices provide an array of reconfigurable logic resources consisting of combinational logic functions, flip-flops, and programmable interconnections. Functionality of current FPGA devices is established by programming.

FPGAs have a different architecture than PLDs and CPLDs, and typically offer higher capacities. The primary differences between CPLDs and FPGAs are architectural. A CPLD has a somewhat restrictive structure consisting of one or more programmable sum-of-products logic arrays feeding a relatively small number of clocked registers. The result of this is less flexibility, with the advantage of more predictable timing delays and a higher logic-to-interconnect ratio. The FPGA architectures, on the other hand, are dominated by interconnections. This makes them far more flexible, in terms of the range of designs that are practical for implementation within them, but also far more complex to design for.

Another notable difference between CPLDs and FPGAs is the presence in most FPGAs of higher level embedded functions, such as adders and multipliers, and embedded memories. A related, important difference is that many modern FPGAs support full or partial in-system reconfiguration, allowing their designs to be changed "on the fly" either for system upgrades or for dynamic reconfiguration as a normal

part of system operation. Some FPGAs have the capability of partial reconfiguration that allows one portion of the device to be reprogrammed while other portions continue running.

FPGAs were originally created to serve as a hybrid device between PALs and Mask-Programmable Gate Arrays (MPGAs). Like PALs, FPGAs are fully electrically programmable, meaning that the physical design costs are amortized over multiple application circuit implementations, and the hardware can be customized nearly instantaneously. Like MPGAs, they can implement very complex computations on a single chip, with devices currently in production containing the equivalent of over a million gates.

FPGAs have an order of magnitude more raw computational power per unit of area than conventional processors. For many applications, FPGA implementations of algorithms offer substantial improvements in energy consumption and execution speed [26] over conventional microprocessor implementations. FPGAs can complete more work per unit of time for two key reasons, both enabled by the computation's spatial organization:

- With less instruction overhead, the FPGA packs more active computations onto the same silicon die area as the processor; thus, the FPGA has the opportunity to exploit more parallelism per cycle.

- FPGAs can control operations at the bit level, but processors can control their operators only at the word level. As a result, processors often waste a portion of their computational capacity when operating on narrow-width data.

Because of these features, FPGAs had been primarily viewed as glue logic replacement and rapid-prototyping vehicles. However, the flexibility, capacity, and

performance of these devices have opened up new opportunities in high-performance computation, forming the basis of reconfigurable computing.

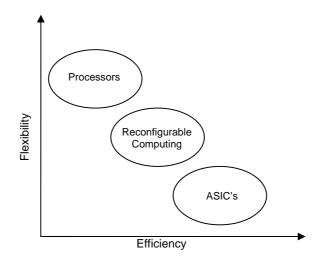

In Figure 2.3 it is shown the tradeoff between flexibility and efficiency as well as the position of reconfigurable devices compared to processors and ASICs.

Figure 2.3 Computing paradigms

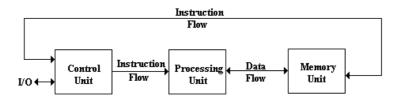

Processors have a general, fixed architecture that allows tasks to be implemented by temporally composing atomic operations, which are provided for example by an Arithmetic Logic Unit (ALU) or a floating-point unit. In contrast, ASICs implement tasks by spatially composing operations, which are provided by dedicated computational units like adders or multipliers. Reconfigurable computing combines these computing paradigms by means of reconfigurable hardware structures, which allow tasks to be implemented both in time and in space providing a higher level of flexibility.

In the GPP case, the instructions (composed into the program code) define the behavior of the computing element. The behavior of a reconfigurable device is specified by its configuration. The behavior of an ASIC is typically hard-wired and

does not allow for any dynamic adaptation, except maybe for some adjustable coefficients.

It has been shown that executing computationally complex sections of applications on RC systems significantly reduces the execution time of the applications compared to the general purpose processor only systems [27]. However, applications must be mapped to FPGA devices before they can be executed on these systems. The mapping processes can be performed either manually or automatically using software tools. Several applications have been mapped to RC systems including image processing algorithms, genetic optimization algorithms, and pattern recognition.

Configurable computing generally presents four main benefits:

- 1. **Performance**. FPGA enable custom computing systems to be highly specialized to specific data, as well as specific applications. One optimization technique uses a form of partial evaluation, where some of the data are assumed static; the FPGA circuit is optimized to take advantage of this static data. Another typical optimization is to implement highly parallel architectures that can exploit significant data-level parallelism. By capitalizing on these optimization opportunities, a highly-tuned, yet programmable, system can be constructed that attains near-ASIC performance.

- 2. Cost Effectiveness. Configurable computing can be used to reduce system costs. A number of research efforts have demonstrated time-shared methods for simulating a large circuit on a smaller FPGA [28-30]. Furthermore, as the feature size of semiconductor processes shrink, silicon foundries are raising mask charges and minimum fabrication runs. These trends are driving low volume digital designs away from state-of-the-art process technology, and making FPGAs much more cost effective.

- 3. **Custom I/O**. FPGAs provide an extremely rich and flexible set of programmable I/O signals. These components give the system designer an opportunity to reuse existing hardware, or commit earlier to a new hardware

design. The benefits of custom I/O extend beyond the prototype stage, if system functionality changes after deployment the ability to rewire system I/O through reprogramming, the FPGA can be an invaluable advantage.

4. **Shorter time to market.** Products that eventually target ASIC platforms can be released earlier using reconfigurable hardware. In many market segments, the early market entry compensates for the more expensive and power hungry nature of the initial product series.

### 2.2.1 Types of Reconfigurable Computing

There are two types of reconfigurable computing that are characterized based on the manner in which they utilize the reconfigurable computing device [31]. The first type, which is most broadly used, is *Compile Time Reconfiguration* [32]. This is when the configuration of the computing device is decided at compile time. In this environment, the reconfigurable device is programmed at the beginning of execution, and remains unchanged until the application has finished. The second type of reconfigurable computing is *Runtime Reconfiguration* (Dynamic Reconfiguration). In this computing paradigm, the application consists of a set of tasks that can be downloaded into the reconfigurable device [32]. During the execution life of the application, the reconfigurable device is re-programmed a number of times from a set of tasks.

### 2.2.2 Dynamic Reconfiguration

FPGA reconfiguration typically requires an entire device to be reconfigured even for the smallest circuit change, thus interrupting all other circuits operating on the array during this period. Ideally, it is desired to configure only the area that is being updated, without interrupting the rest of the system operation. This type of reconfiguration is referred to as Dynamic Reconfiguration or run-time reconfiguration and has been actively researched for the last decade [33, 34].

In the area of reconfigurable computing, dynamic reconfiguration has emerged as a particularly attractive technique to increase the effective use of programmable logic blocks. Dynamically Reconfigurable Logic (DRL) devices allow the change of the device configuration on the fly during system operation.

FPGAs that are not dynamically reconfigurable must be off-line before a reconfiguration cycle, partial or full, can begin. If such a suspension is required then this limits what can be actually done efficiently on the device. Usage, for example, as a programmable algorithm accelerator, is limited in this case, as even small changes to functionality become critical to its whole operation. Certain algorithms, therefore, become undesirable in this kind of set-up. Such devices also have problems with task organization, when multiple tasks are being performed concurrently, as certain tasks are likely to complete before others, thus making it difficult to optimize the whole design for maximum speed advantage.

If a reconfigurable FPGA only supports complete reconfiguration the disadvantages multiply. As such devices increase in density and do not include the ability to partially reconfigure; this is likely to become more problematic.

Reconfiguration time is a crucial parameter for any dynamically reconfigurable computing system [35]. The reconfiguration time imposes limits on the applications that can be efficiently mapped to the reconfigurable hardware. Reconfigurable devices, in particular FPGAs, show relatively long reconfiguration times in the range of dozens of milliseconds [36]. Consequently, rather long-running application functionality is mapped to such devices. For shorter term functionality the

reconfiguration overhead can be significant, negating any performance gain over software. The trend towards ever larger devices intensifies the problem further, because the reconfiguration time is proportional to the amount of configuration data, which grows with the device size.

The data required to configure a reconfigurable device is commonly denoted as a context [37]. Depending on the capabilities of the device, two basic classes are distinguished. Single-context devices store exactly one configuration on the chip. Before a new context can execute, the corresponding configuration data has to be loaded from off-chip. Conventional FPGAs fall into this category. Multi-context devices hold a set of configurations on-chip. At any given time exactly one configuration is in use, the so-called active context. To execute a new context, the contexts are switched, i.e. a previously inactive, stored context becomes active. Since the configuration data does not have to be loaded from off-chip, the context switch is significantly speeded up.

In DRL, a circuit or system is adapted over time. This presents additional design and verification problems to those of conventional hardware design [38] that standard tools cannot cope with directly. For this reason, DRL design methods typically involve the use of a mixture of industry standard tools, along with custom tools and some handcrafting to cover the conventional tools inadequacies. The lack of commercial Computer Aided Design (CAD) tool support and complexity of designing dynamically reconfigurable hardware has led to the creation of a number of research tools such as JHDL and JBits.

JHDL [39, 40] is a free Java based tool for FPGA design. This tool is a result of BYU research. JBits [17, 41] is the only commercial available tool that supports dynamic and partial reconfiguration of Xilinx Virtex FPGAs using standard Java functions. Xilinx uses this language in its Internet Reconfigurable Logic via standard Java

applications. These tools are based on Java language which is the most popular software language with Internet support.

Current tools are slow and hardware oriented and there is no way to program such systems in a general purpose manner. Other software tools are also required which suit reconfigurable systems, such as:

- Simulation Models for dynamic reconfiguration.

- Automatic design partitioning, based on temporal specifications.

- Support for generation of relocatable bitstreams.

- A simulation package for modeling new FPGA architectures.

- Debugging tools.

Reconfigurable computing is an active research area with several new directions being explored to develop better architectures, methodologies, algorithms and software tools. There is an acute need for software tools that permit simulation of dynamic reconfiguration and mapping of applications onto dynamically reconfigurable architectures.

### 2.3 Handel-C

Handel-C [42] is a programming language whose objective is to allow the designer a fast prototyping of applications on target FPGA from specifications in a high-level language. Handel-C uses syntax similar to conventional C language, with the addition of parallel descriptors and some features to handle channels and interfaces.

Sequential programs can be written in Handel-C just as in conventional C, but to gain the most benefit in performance from the target hardware, its inherent parallelism must be exploited [40]. As with conventional high level languages, Handel-C is designed to allow the expression of the algorithm without worrying too much about exactly how the underlying compilation engine works. This philosophy makes Handel-C a programming language rather than a hardware description language.

Although Handel-C is inherently sequential, it is possible to instruct the compiler to build hardware to execute statements in parallel. Handel-C parallelism is true parallelism, it is not the time sliced parallelism, familiar from general purpose computers. When instructed to execute two instructions in parallel, they are executed at exactly the same instant in time by two separate pieces of hardware.

The principle of Handel-C is the following: during the phase of compilation, every instruction on the source program is transformed into a material entity which makes one or several treatments on every associated instruction to generate a set of material blocks representing all the instructions of the program. The DK design suit synthesizes the design and generates a netlist in an EDIF format. The netlist is then passed to a vendor place and route tool which generates a placement and routing, and finally a bitstream to configure the device. Because of its high abstraction level, Handel-C allows coding of complex algorithms without having to consider lower-level designs. Using Handel-C constructs, the development cycle for the creation and testing of FPGA designs can be accelerated. In addition, the package includes a library of basic functions and a memory controller to access the external memory on the FPGA board.

### 2.4 Related Work

Parallel computing has been major subject of research since at least the early 1980s. This approach has permitted to solve complex problems and to implement highperformance applications in areas such as science and engineering.

A parallel computer is constituted of a set of processors that are able to work cooperatively to solve a computational task. This definition is broad enough to include parallel supercomputers that have hundreds or thousands of processors, networks of workstations, multiple-processor workstations, and embedded systems.